面向任务关键型应用的FPGA

描述

大多数FPGA技术都无法满足关键任务设计要求,但基于防熔断器的架构取得了成功,提供了抗辐射性和设计安全性等基本属性。

当今的高密度 FPGA 为设计人员提供了快速创建定制组件的机会,以实现最佳性能和任务关键型系统的快速部署。但对于军事和航空航天应用,众所周知,基于存储器的FPGA技术无法满足几个重要要求,包括抗辐射性和设计安全性。防熔断器FPGA技术成功地满足了这些要求,将可编程逻辑的优势带到关键任务系统设计中。

许多开发人员明白,任务关键型系统必须设计为在极端环境条件下可靠运行,但发现大多数FPGA技术都难以满足这些需求。此外,在确定设备是否适合大多数FPGA技术不足的关键任务服务时,还有其他要求同样重要。我们的讨论将集中在其他三个关键要求上:非易失性配置、辐射环境中的可靠运行和设计安全性(表1)。

表1

影响关键应用的三个因素

对非易失性配置的要求源于关键任务军用航空应用中电源中断的高概率。在维护或维修期间更换带电系统组件、从线路电源切换到电池电源时的失误以及掉电都可能触发系统从电源中断中恢复的需要。非易失性系统配置简化了恢复过程,无需重新加载系统设置和参数。这使得系统恢复比必须重新加载配置时更快、更不容易出错,从而提高了系统可用性以执行其任务。

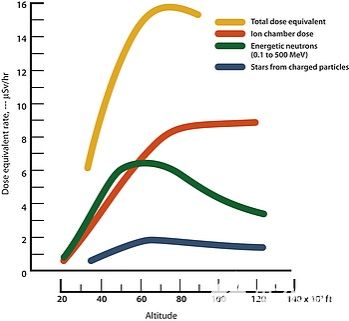

此外,随着冷战的结束,对军用航空系统在辐射环境中运行的需求已经从普遍意识中消失了。然而,这一要求不仅仅来自在核事件中幸存下来的需要。即使在日常操作中,关键任务系统也可能暴露在高辐射水平下。辐射以宇宙射线和太阳风的形式出现,以及这些来源在高海拔地区产生的高能二次粒子(见图1[1])。

图1

虽然辐射通量通常不足以损坏半导体器件,但它确实会对系统运行产生影响。辐射的典型效应是单事件翻转(SEU):一种能够改变存储单元位值的局部能量尖峰。如果这种变化发生在FPGA内的关键位置,可能会对系统运行造成严重破坏。

设计安全性是关键任务系统设计的第三个要求,特别是军事系统。如果设计不安全,敌人可以通过逆向工程和克隆捕获的设备供自己使用来迅速消除此类设计提供的任何技术优势。系统还可能嵌入敏感信息,例如密码、加密密钥和跳频算法。从捕获的系统中提取此类信息将允许敌人制造能够拦截和解释编码通信或生成模仿信号以混淆指挥和控制活动的设备。进行逆向工程困难、昂贵且耗时的设计可以通过延迟结果直到它们不再有用来防止这种妥协。

比较 FPGA 技术

在利用FPGA技术开发关键任务系统时,这些被忽视的设计要求尤为重要。使用 FPGA 器件可为开发人员提供与使用 ASIC 相当的设计灵活性和集成度,但成本要低得多,并且可用性更即时。然而,并非每种FPGA技术都适合任务关键型设计的需求。

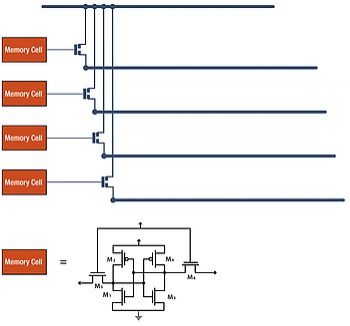

例如,许多FPGA未能满足非易失性要求,因为它们以SRAM为基础。这些 FPGA 中的内部逻辑连接依赖于 SRAM 单元来保持开关晶体管的打开或关闭(图 2)。因此,存储在存储器中的数据决定了FPGA的配置,但SRAM单元在断电时将丢失其数据。

图2

基于 SRAM 的 FPGA 需要在上电时接收配置数据,以便为系统运行做好准备。典型的方法是采用小型外部非易失性存储器源(如串行EEPROM)来保存配置数据。上电后,FPGA从EEPROM检索数据并自行配置工作。根据存储器的大小和FPGA可以检索数据的时钟速率,FPGA可能需要上电后几百毫秒才能准备好使用。系统的其余部分必须等到FPGA准备就绪才能完全运行。

可编程逻辑的SRAM方法也有几个不幸的设计属性。一是每个连接点所需的电路相当大,需要多个晶体管来形成SRAM单元,导致互连密度降低。开关晶体管的互连电容增加了FPGA的动态功耗,增加了结温并降低了器件可靠性,即使不计时,大存储单元的漏电流也会浪费功率。

一种非易失性可编程逻辑方法具有类似的开关结构,但使用EEPROM单元而不是SRAM来保持配置。这种方法解决了波动性问题,但仍与基于SRAM的FPGA共享许多其他属性。该架构仍然要求在每个连接点安装一个开关晶体管,从而限制了通过连接的互连密度和信号速度。

EEPROM单元的工作原理是在浮动栅极上保持电荷,以保持开关晶体管的打开或关闭。当高压编程信号通过穿过氧化层将电子驱动到栅极上或离开栅极时,浮动栅极接收或失去其电荷。在正常工作中,栅极没有可用的放电路径,因此使得FPGA配置是非易失性的。

提供非易失性的另一种方法是使用防熔断技术。防保险丝是FPGA中每个可配置电路结处的非晶硅过孔。未经编程,过孔是绝缘体,在该站点没有连接。通过对其施加高压来编程过孔,将其状态更改为导体,从而在该站点进行连接。因此,过孔的物理状态与FPGA的配置保持一致。状态变化是永久性的,使防熔断器FPGA非易失性。由于没有晶体管参与维持逻辑连接,因此互连密度高且没有漏电流。互连电容低,降低了动态功耗。

解决辐射问题

除了波动性问题之外,在辐射环境中工作的需求是对基于存储器的FPGA技术的第二次打击。通过有源半导体器件的高能粒子在硅中产生临时电离路径。这些通路可以短暂地短路晶体管,产生称为SEU的瞬态脉冲。

在SRAM中,SEU可以反转单个位的状态,然后存储器电路将保持该状态。在EEPROM中,SEU可能会对浮动栅极放电,从而导致永久性的位变化。虽然处理器应用中使用的存储器通常包括纠错和检测来处理此类事件,但FPGA的配置存储器没有这种保护。因此,SEU 可以在基于存储器的 FPGA 中引入持久的逻辑更改。

反保险丝FPGA没有这样的漏洞。SEU的能量不足以对过孔进行编程,瞬态脉冲对逻辑没有显着影响。在NASA/戈达德进行的测试表明,在辐射能量高达193 MeV的反保险丝FPGA操作中没有错误,而存储设备开始出现低至100 MeV的位错误。

防熔丝 FPGA 还比基于存储器的 FPGA 更有效地解决设计安全性问题。要完整表征编程的FPGA,需要两条信息:配置细节和底层结构。配置细节在基于存储器的FPGA中最容易捕获。对于实时系统,无源探测可以在配置期间移动到基于 SRAM 的 FPGA 时捕获编程数据。电子探测可以确定电路处于活动状态时EEPROM构型电池的电荷状态。这两种方法的执行速度都相对较快,实施成本也很低。

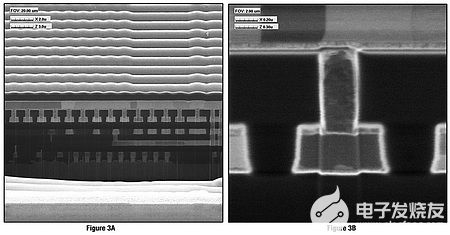

确定FPGA的逻辑结构需要更多的努力,但逆向工程方法可以提取器件的设计细节,价格低于10万美元。方法是使用等离子体(用于钝化和氧化层)或化学(用于金属层)蚀刻剥离逻辑器件的每一层,一次一层,然后在显示每一层时拍摄高分辨率照片(图 3)。这些照片可以重建用于制造设备的掩模组。然后,这允许分析甚至克隆设备。

图 3:3A 和 3B

然而,研究反熔断器FPGA的编程需要更精细的措施。这部分是因为可编程元件位于多层结构中,因此表面扫描无效。此外,没有信号或存储电荷进行探测;程序存储是影响电阻的结构变化,而不是电荷的积累。

只有体检才能显示反引信的编程状态,剥层法不会有效工作。反引信中改变区域的横截面太小,无法从上方观察,因此可靠地看到结构的唯一方法是从侧面(再次参见图 3)。获得此视图需要使用聚焦离子束 (FIB) 在设备中创建沟槽,然后铣削边缘以逐步扩展沟槽。在每一步拍摄照片可以创建电路的3D图像。然而,这个过程需要昂贵的设备,而且在不知道去哪里寻找的情况下非常耗时。即使有先见之明,需要检查的反引信数量也使这项任务变得不切实际。对编程反熔丝FPGA(如QuickLogic的QL1P075和QL1P100‘Äì)进行逆向工程所需的时间实际上使它们绝对安全。

防熔断器满足关键任务需求

军用航空应用的设计安全需求,以及耐辐射性和非易失性,在文献中经常被忽视,但设计人员也不容忽视。在寻求FPGA在设计中的优势时,开发人员习惯性地寻找能够解决mil temp操作的器件,但他们也应该考虑基础技术满足上述需求的能力。在FPGA技术中,反熔断器可编程性是唯一满足关键任务设计所有要求的技术。

审核编辑:郭婷

-

fpga关键路径2013-07-12 4280

-

FPGA设计技巧_关键路径2014-04-22 35049

-

FPGA电源管理的关键是什么?2019-08-02 1457

-

什么是OpenCL?面向FPGA的OpenCL有什么优点?2019-09-17 1873

-

关键任务系统中的任务热插拔技术2009-04-22 815

-

Altera推出面向Stratix IV FPGA的最新开发2009-12-09 1142

-

Altera发布面向FPGA的OpenCL解决方案 简化FPGA开发2012-09-04 1147

-

基于_SAN_的存储基础架构支持当今多样化的任务关键型工作负载所2016-12-28 867

-

OLED显示模块是关键任务型应用首选2019-03-07 2930

-

莱迪思Nexus FPGA技术平台在关键任务应用中的优势2021-05-10 4863

-

FPGA执行通信密集型任务优势 FPGA部署方式特点及限制2022-08-10 1354

-

FPGA执行计算密集型任务性能表现及优势有哪些2022-11-10 1815

-

面向FPGA的电源管理2023-01-03 3034

-

FPGA设计的五个主要任务2023-04-06 1662

-

爱立信携手高通、Crosscall及Streamwide演示大规模部署任务关键型通信2023-06-09 2552

全部0条评论

快来发表一下你的评论吧 !