Versal ACAP GTY收发器仿真示例分析

描述

本篇博文侧重于提供 Versal GTY 仿真示例、演示 GTY 如何解复位以及如何执行速率变更。

在 Versal ACAP GTY 收发器中,引入了“Master Reset Controller”(主复位控制器)的概念。

主复位控制器用于自动单步执行 LCPLL、RPLL、ILO、TX 可编程分频器、RX 可编程分频器、TX 通道以及 RX 通道的复位。

您可在 AM002 的“收发器主复位”部分中找到详细描述。GTY 中的全新主复位控制器取代了前几代 UltraScale/UltraScale+ 收发器的 GT Wizard 内包含的复位控制器帮助程序块。

在本仿真示例中,Versal GTY 配置如下:

通道 2 (ch2) 上为单通道

采用双线速率,将 10G/25G 编程到 CONFIG0/CONFIG1 内

对于这两个速率,REFCLK 均为 156.25MHz 并穿过相同的参考时钟端口

IP 设计示例用于完成设计并提供仿真测试激励文件。

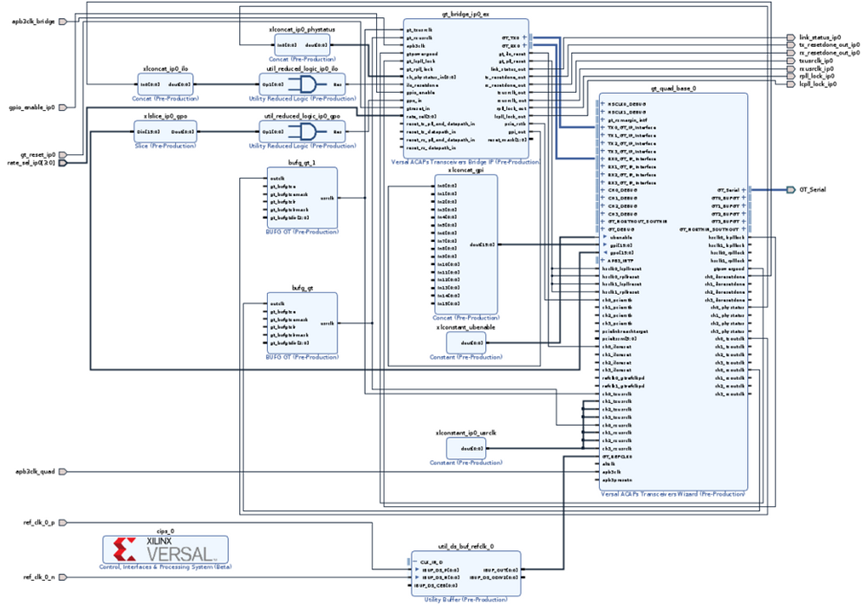

模块框图

设计示例的模块框图如下图所示。

此处随附了块设计 Tcl 脚本 (run.tcl)。

Vivado 步骤

创建 gt_quad_base IP 并打开 IP 设计示例

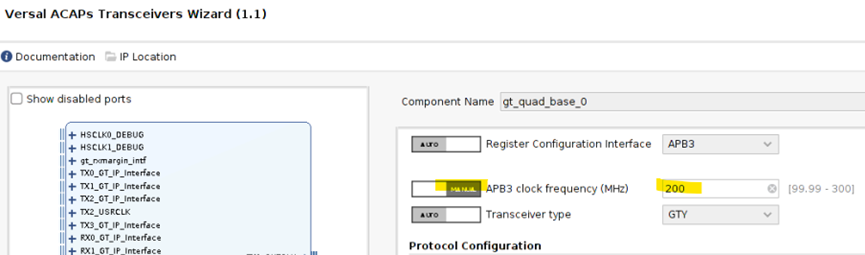

1. 创建 gt_quad_base IP。在此例中,我们使用单通道配置。

2. 针对“Number of Lanes”(通道数)和“Transceiver Configs Protocol 0”(收发器配置协议 0),将滑块设为“Manual”(手动)。这样即可使用自定义配置。

3. 将“Number of Lanes”设为 1。

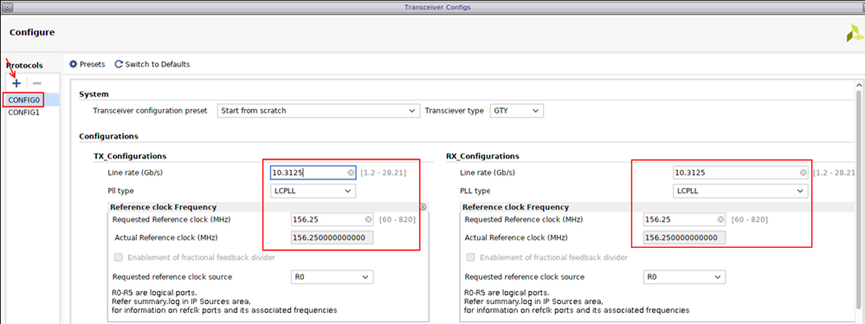

4. 单击“Transceiver Configs Protocol 0”,以自定义收发器。

5. 将 CONFIG0 设为 10.3125Gbps。

6. 将 CONFIG1 设为 25.78125Gbps。

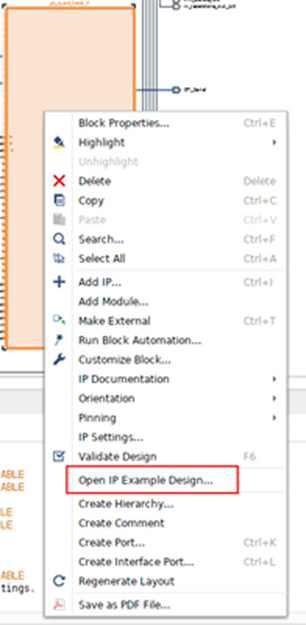

7. 在 IP integrator 画布中,右键单击 gt_quad_base,然后选择“Open IP Example Design”(打开 IP 设计示例)。这样将在新的 Vivado 工程内创建设计示例。

启动仿真

设计示例会为时钟和复位建立所有必要的连接,并生成顶层仿真测试激励文件 gt_quad_base_exdes_tb.sv。

在设计示例工程中,单击“Run Simulation”(运行仿真)启动仿真。

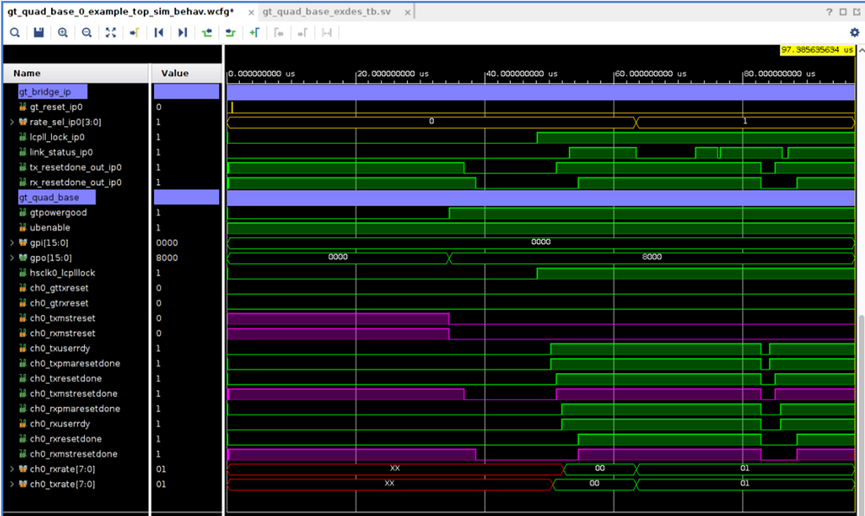

下图显示了仿真波形,其中包含要监控的关键信号。

复位初始化

默认 bridge_ip 使用 Versal GTY 中包含的 Master Reset Controller 来复位排序。

请参阅 ( AM002) 中的“收发器主复位”部分以获取详细信息。

当 T=0.8ns 时,gt_reset_ip0 将切换为启动复位初始化。

复位控制器状态机首先会等待 gtpowergood,然后再开始执行任何复位操作。当 T=34us 时,gtpowergood 断言有效。

txmstreset 和 rxmstreset 断言无效,这样即可启动主复位序列。

*resetdone 信号将断言无效,以响应 tx/rxmstreset 断言无效。

当 T=48us 时,lcplllock 断言有效。

当 T=50us 时,txpmaresetdone 断言有效,随后 txuserrdy 驱动至高位、txresetdone 断言有效,不久后 txmstresetdone 即断言有效。bridge_ip tx_resetdone_out_ip0 同样会断言有效。这样即可完成 TX 复位序列。

当 T=52us 时,rxpmaresetdone 断言有效,随后 rxuserrdy、rxresetdone、rxmstresetdone 以及(最后)rx_resetdone_out_ip0 断言有效。这样即可完成 RX 复位序列。

GTY 现已正常启动并运行,并采用默认 (CONFIG0) 速率 (rate_sel_ip0 = 0)。

速率变更

速率变更序列是通过将 rate_sel 端口更改为目标速率来发起的。所需的复位、时钟切换和属性更新都将自动执行。用户应等待 txresetdone 和 rxresetdone,这两者可作为当前速率变更进程和必要的复位序列均已完成的标志。

1. 当 T=63us 时,rate_sel_ip0 从 0 变更为 1。这样将发起速率变更序列,目标为自定义 GUI 的 CONFIG1 中配置的新线速率(在此例中为 25Gbps)。

2. 当 T=85us 时,txresetdone 断言有效。当 88us 时,rxresetdone 断言有效。这样即可完成速率变更序列。

3. GTY 现已正常启动并运行,并采用 CONFIG1 速率 (rate_sel_ip0 = 1)。

审核编辑:郭婷

-

Versal ACAP收发器向导 LogiCORE IP产品指南2023-09-14 473

-

Versal ACAP设计指南2023-09-13 491

-

Versal GTY/GTYP:使用PRBS生成器和检查器2023-07-10 2106

-

使用QEMU启动Versal VCK190 ACAP2023-07-07 1314

-

Versal GTY仿真:初始化,复位和速率变更2022-11-23 2214

-

Versal ACAP中的配电系统2021-09-09 5232

-

UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法2020-11-04 9923

-

Xilinx 创下新里程碑,Versal ACAP 开始出货了!2019-07-02 2607

-

符合Virtex UltraScale方案的Virtex UltraScale 30G GTY收发器2018-11-22 4163

-

是否有关于为GTY收发器发布IBERT的讨论?2018-09-28 3314

-

利用32.75Gbps Virtex UItraScale GTY收发器做些什么?2017-02-11 3560

全部0条评论

快来发表一下你的评论吧 !