如何清除标准单元布局?验证Tie high/low Cells的过程

电子说

描述

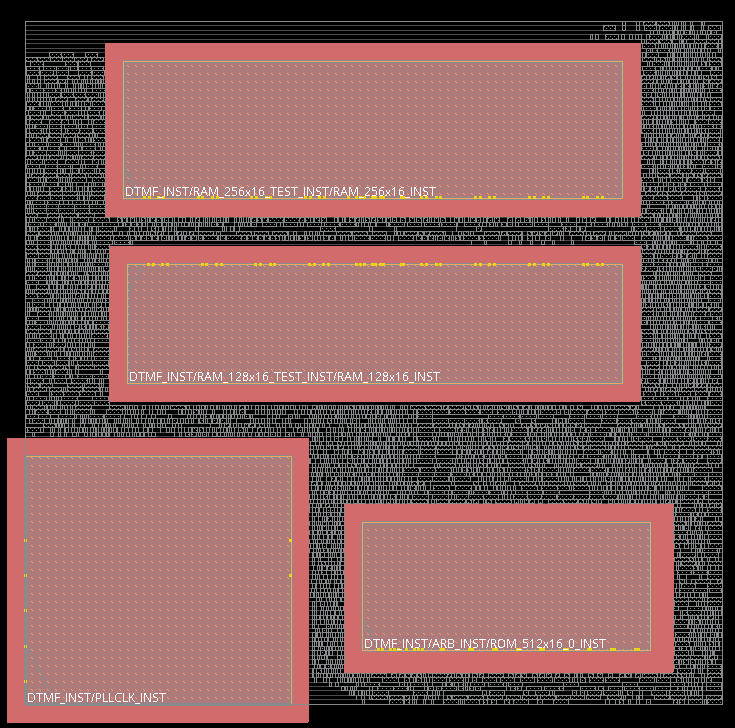

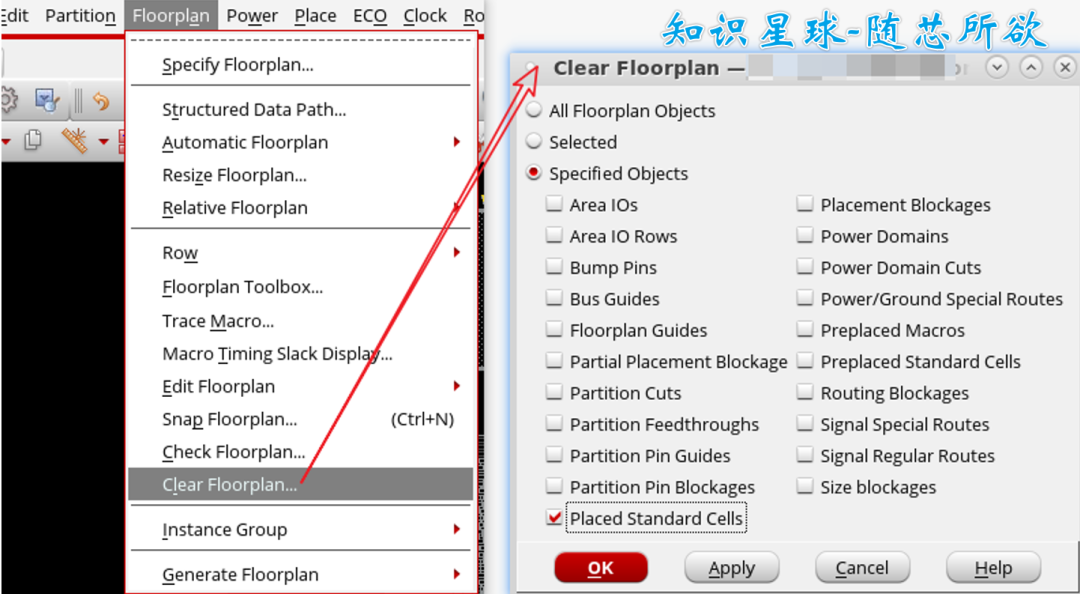

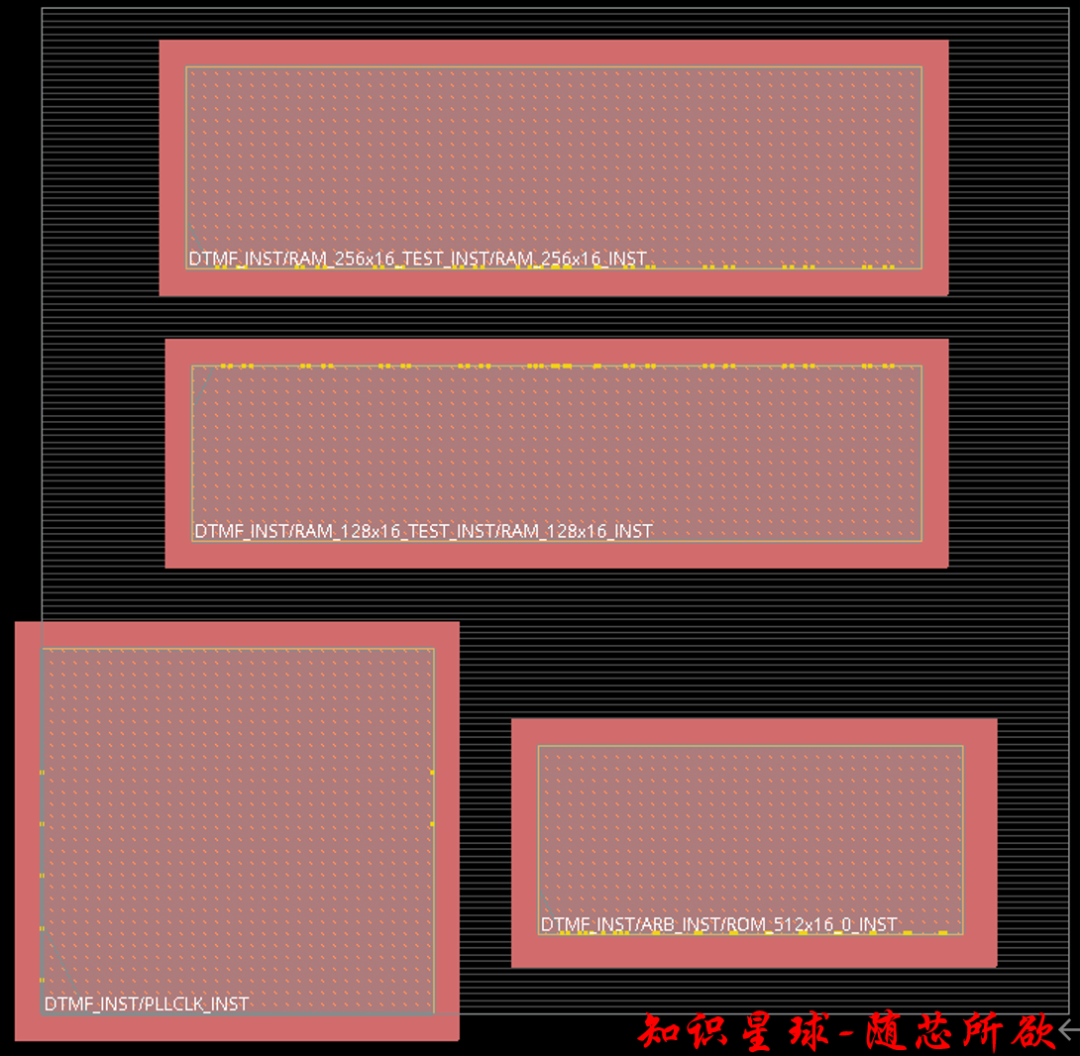

如何清除标准单元布局?

GUI操作: Floorplan > Clear Floorplan. 在对话框中选择“Specified Objects”,勾选“Placed Standard Cells”然后点击OK。

效果:

相应的命令: 下面的命令会把Design中所有状态是“Place”的Instance状态改为“Unplaced”。但是不会动那些状态是FIXED, SOFTFIXED或者COVER的Cell。

Legacy UI:

unplaceAllInsts

Common UI:

unplace_obj -insts

如果想将设计中所有的标准单元全部设置成Unplaced(也就是清除所有标准单元的布局),可以用下面的命令,将pStatus改为unplaced即可:

Legacy UI:

dbSet [dbGet top.insts.cell.baseClass core -p2].pStatus unplaced

Common UI:

set_db [get_db insts -if {.base_cell.class == core}] .place_status unplaced

Place阶段自动摆放Terminal

如果设计对Terminal的位置没有特殊的限制,自己可以随意控制,那么也可以不导入IO管脚排列文件,可以让工具在布局阶段自动摆放。

方法如下:

Place之前,在Mode Setup下方勾选Place IO Pins:

相应的命令:setPlaceMode -place_global_place_io_pins true

如果想对一些Pin的edge和layer等做一些约束,可以用命令

setPinConstraint setPinConstraint- Sets the constraint for a partition pin or an I/O pin

* The following command sets the sides, T and B, of layer 3 and 5 of partition cell ptn4

setPinConstraint -cell ptn4 -layer {3 5} -side {T B}

* The following command sets the edges, 2 and 0, of partition cell ptn4 setPinConstraint -cell ptn4 -pin * -edge {2 0}

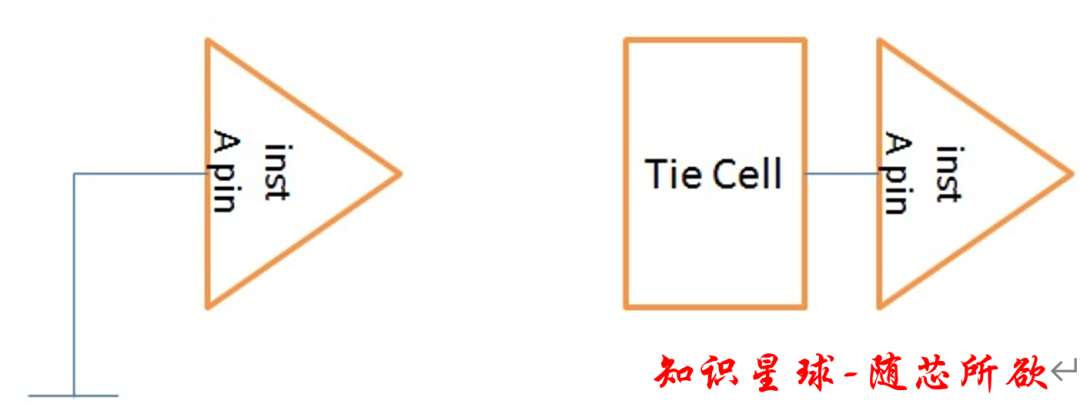

验证Tie high/low Cells

在做布局之前我们做了相应的设置来让工具在布局的时候添加Tie high/low cell,那么我们如何验证设计中所有接1/0的Cell的Cell的Pin都通过Tie high/low cell接到了电源地而非直接接到了电源地呢?

答案:

可以用命令verifyTieCell,在执行该命令前需要首先做好setTieHiLoMode的设置,否则会报下面的错误:

innovus 4> verifyTieCell

**ERROR: (IMPVFC-265):No TieCell defined, please refer to command 'setTieHiLoMode'.

**WARN: (IMPVFC-263):verifyTieCell failed.

verifyTieCell命令会检查那些需要tie high/low的Net是否接到了用setTieHiLoMode -cell指定的tie high/low cell上。

上图的左边部分显示verifyTieCell违反,右边部分显示没有违反。

除此之外,该命令还可以检查那些不应该接到tie high/low cell上的Instance或者Pin,可以加下面的选项:

-noTieCell filename filename

指定一个含有instance/pin名字列表的文件即可。

上图的左边部分表示verifyTieCell -noTieCell没有检查出违反,右图会检查出违反。

另外,我们应该在什么时候做这个检查呢?只需要在Place做这个检查么?

答案是不一定的,现在的PR工具在其他步骤也可以通过做逻辑的优化与更改,因此我们最好在每一步(place、CTS、postRoute)都做一下检查,发现问题赶快解决。

审核编辑:刘清

-

浅谈芯片设计中的标准单元2026-04-21 97

-

数字标准单元库的工艺设计套件生成步骤2026-02-02 509

-

概伦电子标准单元库特征化解决方案NanoCell介绍2025-04-16 1123

-

浅谈集成电路设计中的标准单元2025-03-12 2201

-

如何添加、报告、验证tie high/low cell?2023-09-25 2804

-

概伦电子精准高效标准单元库EDA解决方案NanoCell2022-07-28 2992

-

请问arm提供的标准单元库中的track是什么意思2022-06-14 2699

-

标准单元的ASIC为什么仍是唯一的技术选择?2021-04-08 1513

-

基于标准单元的SoC芯片设计流程2021-01-26 2994

-

如何使用Synopsys PAC进行标准单元布局的改进2019-03-04 1245

-

高能效宽电压工作标准单元库分析与优化2017-01-07 645

-

面向近亚阈值的标准单元库设计方法2017-01-03 563

-

MOS电流模逻辑标准单元设计方法2010-05-24 531

-

基于标准单元ASIC设计2010-03-26 1390

全部0条评论

快来发表一下你的评论吧 !