HKMG工艺在DRAM上的应用

描述

近期,DRAM制造工艺又实现了一次突破,这次操作来自于SK海力士,该公司宣布,已成功开发出全球首款采用HKMG(High-K Metal Gate)工艺的LPDDR5X内存,采用1αnm制程,该款LPDDR5X与上一代产品相比,功耗降低了25%,数据传输速率提高了33%,并在JEDEC设定的1.01V-1.12V超低电压范围内运行。

LPDDR5X用于以手机为代表的移动设备,它与PC、服务器用DRAM不同,对低功耗要求很高,同时,性能又不能下降太多,通过采用HKMG工艺,可以更好地保证提高性能地同时,又降低功耗。

以往,HKMG工艺主要用于逻辑芯片,特别是CPU、GPU等处理器,近些年,随着市场需求的发展,特别是5G通信、汽车智能化、VR/AR和使用AI的边缘计算等应用场景对内存性能的要求越来越高,DRAM制程工艺演进到了10nm-20nm范围,此时,高性能与低功耗的矛盾逐渐凸出,而HKMG是解决这一矛盾体的有效方法,首先是应用于非移动设备用DRAM,如服务器中的DRAM,代表企业是三星,如今,HKMG被引入移动设备用DRAM,也就是LPDDR,也是一个标志性的跨越。

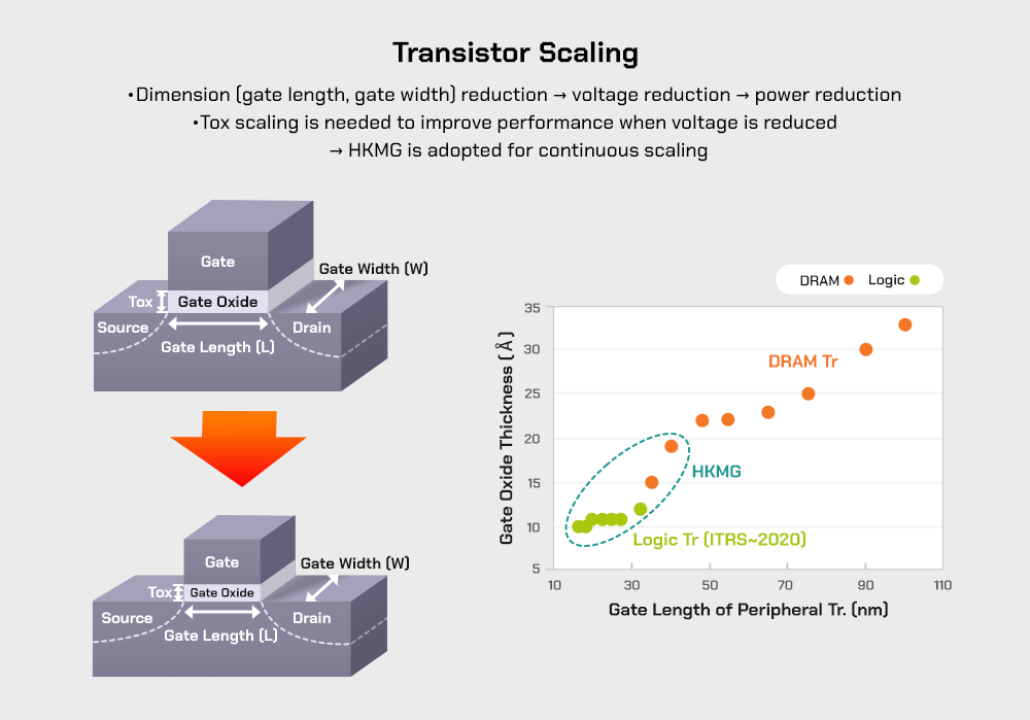

01、HKMG是何方神圣?

早期,集成电路晶体管栅极材料用的是铝,采用的相关配套结构是铝金属/二氧化硅,后来发展到了多晶硅栅,采用的配套结构是多晶硅栅/二氧化硅,之后又经过一段时间的发展,升级到了多晶硅栅/SiON,2007年,HKMG横空出世。

提起HKMG工艺的由来,不得不提到集成电路传统霸主英特尔,2007年初,英特尔宣布在45nm制程节点处利用新型High-k(高介电常数)介质材料HfO2(二氧化铪)来代替传统SiON作为栅介质层,以改善栅极漏电流问题,同时利用金属栅代替多晶硅栅,开发出了HKMG工艺。之所以是45nm,是因为半导体制程按照摩尔定律发展到这个节点时,晶体管中最先达到极限的是栅极电介质,传统的栅极电介质已无法满足晶体管性能提高、体积缩小的要求,易产生漏电流等问题,造成晶体管可靠性下降,而高K金属栅则可以解决这一问题。HKMG工艺的最大特点就是介电常数高,HKMG以金属氧化物作为栅极电介质,与传统栅极结构相比,可以减少栅极漏电流,降低工作电压,并提高晶体管可靠性。这是20世纪60年代以来,晶体管技术的重大突破,也是半导体产业的一项重要创新。

可用作高K金属栅极电介质的金属氧化物需要具备禁带宽度高、物理化学性质稳定、热稳定性好、可制造薄膜材料、与硅元素兼容、兼容CMOS工艺等特点。HfO2是主流的高K金属栅极电介质材料,在半导体产业得到广泛应用。但HfO2存在高温稳定性较弱、与硅兼容性较差、沉积薄膜易产生缺陷等缺点,新的高K金属栅极电介质还在开发过程中。另外,铪基材料与多晶硅栅的兼容性一直是一个问题,所以需要采用金属栅。

当然,采用HKMG技术,对于金属栅极是有要求的,金属栅极的选择受到多种因素的影响,具体就不在此详述了。

02、DRAM大厂聚焦HKMG

近些年,三星电子,SK海力士、美光这三大存储芯片厂商竞相开发10nm-20nm制程级别DRAM,相继引入了EUV光刻设备,这在以前只会用于制造各种CPU等处理器,可见市场应用对DRAM要求越来越高,使得这三大厂商必须在制程工艺方面下更多功夫,因此,继 EUV之后,HKMG成为了另一个焦点。

2021年,三星电子首次将HKMG工艺用于DDR5,并推动了商业化进程。当时,三星电子曾经表示,HKMG DDR5内存模块的功耗比传统工艺减少了约13%,计划根据下一代计算市场的客户需求,适时将该内存商业化。但是,三星一直没有公开该款DRAM的商用化案例。今年,TechInsights透露了相关信息,该芯片已经应用于一家中国台湾高性能内存模块制造商的产品,据悉,该款DRAM是16Gb的DDR5,采用了HKMG工艺制造。

作为三星电子的老对手,DRAM大厂SK海力士自然不会坐视三星在DRAM技术方面领先,看到对手在PC、服务器用DRAM上采用了HKMG工艺,SK海力士更进一步,将该工艺用在了对功耗要求更高的移动设备DRAM上,也就是前文提到的LPDDR5X。

那么,SK海力士是如何做到的呢?

首先要了解一下DRAM的基本结构,组成DRAM的晶体管有以下几种:存储数据的单元晶体管(Cell Transistor),恢复数据的核心晶体管(Core Transistor),涉及控制逻辑和数据输入/输出的外围晶体管(Peripheral Transistor)。随着技术的进步,单元晶体管在提高DRAM存储容量方面取得了一些技术突破。然而,原来的核心晶体管和外围晶体管特性越来越不适合DRAM的应用要求,成为了发展瓶颈,特别是对于外围晶体管而言,只有实现工艺尺寸的进一步微缩,才能提高性能,在需要快速提高性能的高端产品中尤为如此。因此,需要一种全新的解决方案来克服微缩基于多晶硅栅极/SiON的晶体管时存在的限制,此时,HKMG工艺就是一个理想方案。

为了将DRAM的多晶硅栅极/SiON转换为HKMG栅极,需要对相关工艺进行更改,还必须对HKMG材料、工艺和集成流程进行优化,以适合新材料和新工艺。具体来看,要开发出一套复杂的工艺(具体情况不得而知,因为这是SK海力士的核心竞争力,属于绝对的商业机密),来解决以下几个问题。

一是要解决兼容性问题。与多晶硅栅极/SiON相比,HKMG的热稳定性较弱,由于DRAM需要在高温下进行特殊处理,以实现单元阵列结构,这与逻辑芯片(CPU、GPU等)采用的HKMG工艺有很大不同。因此,DRAM中HKMG工艺的特殊性会导致其可靠性下降,这就必须对HKMG工艺和DRAM集成工艺进行优化,以解决可靠性下降问题。

二是新材料控制。需要引入工艺控制措施,例如针对新材料的测量方案,以防止现有器件受到新材料和新工艺的影响。

三是要开发具有成本效益的工艺。可通过工艺集成优化,最大限度地减少因引入新材料和新工艺而导致的成本增加。

四是设计与测试优化。随着栅极材料的变化,晶体管特性和可靠性与传统多晶硅栅极/SiON截然不同,为了最大限度地发挥HKMG的优势,增强可靠性,需要新设计方案,并优化相关测试。

总之,通过将HKMG整合、优化成为适用于DRAM工艺的形式,开发出新平台,并通过包括试点操作在内的预验证工艺来确保方案可行,从而实现将HKMG工艺用于DRAM量产。

03、结语

以往,具备低漏电、高性能特性的先进制程工艺多用于逻辑芯片,特别是PC、服务器和智能手机用CPU,如今,这些工艺开始在以DRAM为代表的存储器中应用,再加上EUV等先进设备和工艺的“互通”,逻辑芯片和存储器的制程节点和制造工艺越来越相近。

在上世纪60年代,当CPU刚开始批量生产的时候,其制造工艺就是基于当时的存储器SRAM的工艺,经过几十年的发展,应用系统的变迁对CPU的要求不断提高,相应的制程工艺随摩尔定律快速发展。相对而言,存储器对制程的要求没有CPU那么高,但随着应用的进一步发展,特别是大数据和AI的演进,原有存储器制程的发展节奏难以满足应用要求了。因此,存储器制程工艺紧追了上来,目前已经十分接近以CPU为代表的逻辑芯片了。

这样的发展也使得CPU和DRAM之间的工艺壁垒变小了,这也在一定程度上迎合了存算一体发展趋势,也就是将CPU、AI等功能集成进DRAM。HKMG工艺在DRAM上的应用可以进一步促进存算一体的发展。

审核编辑:郭婷

-

DRAM原理 - 1.存储单元阵列#DRAMEE_Voky 2022-06-28

-

DRAM原理 - 6.猝发模式与内存交错#DRAM原理EE_Voky 2022-06-28

-

DRAM内存原理2009-10-21 0

-

三星宣布:DRAM工艺可达10nm2015-12-14 0

-

HKMG实现工艺的两大流派及其详解2010-03-23 7900

-

专访格罗方德Subramani Kengeri:28nm量产致胜关键在于HKMG2012-07-15 4925

-

为什么英特尔那么牛?制程工艺引业界惊叹!2013-11-19 25263

-

三星18nm工艺的DRAM芯片惹祸了2017-03-03 2600

-

美光表示:EUV光刻机在DRAM芯片制造上不是必须的,直到1α及1β工艺上都也不会用到它2018-06-07 6382

-

美光认为暂时用不上EUV光刻机,DRAM工艺还需发展2018-08-20 1252

-

新突破!美光宣布批量出货1α工艺节点DRAM2021-01-27 3070

-

美光1αDRAM芯片工艺可提升密度40%2021-01-29 2438

-

对先进DRAM工艺中有源区形状扭曲的研究2022-08-01 1106

-

三星电子DDR5 DRAM内存颗粒实现HKMG工艺大规模应用2022-09-19 1621

-

SK海力士全球首次在移动端DRAM制造上采用HKMG工艺2022-11-11 1419

全部0条评论

快来发表一下你的评论吧 !