设计安全关键型嵌入式系统:在运行时检测SRAM故障的挑战

描述

作者:Henrik Nyholm,Jacob Lunn Lassen

在设计安全关键系统时,国际安全标准对我们选择适当的工艺和适当的技术来检测和避免最终产品中的危险故障至关重要。这些标准确保我们不会陷入与之前的安全工程师同行相同的坑。

然而,这些标准的危险在于,它们假设你对底层硬件(比如微控制器)有详细的了解,这可能会导致经验不足的安全工程师实施不安全的设计。例如,IEC(国际电工委员会)60730标准建议使用棋盘格内存测试来检测B类软件可变存储器中的直流故障,这比看起来更具挑战性。

本文描述了SRAM的逻辑和物理布局之间未记录的差异如何导致我们无意中错误地实施诸如棋盘格算法之类的内存测试。标准微控制器的数据表中通常没有必要的信息,但幸运的是,有些存储器测试算法不受SRAM逻辑和物理布局差异的影响。

在运行时测试 SRAM 是否存在缺陷

SRAM存储器显然由IC供应商在生产中进行测试,有缺陷的产品不会运送给消费者。尽管如此,在IC的使用寿命期间,随机硬件缺陷可能并且将会出现,这也是在安全关键应用中需要在运行时测试微控制器中的硬件的原因之一。

棋盘格内存测试

IEC 60730 (H.2.19.6.1) 等安全标准表明,对于必须符合 B 类安全等级的应用,可以使用棋盘算法来识别 SRAM 中的某些缺陷(直流故障)。通常选择棋盘格测试,因为它涵盖了SRAM中最可能的故障,并且速度相对较快,可以方便地将对应用本身的性能影响降至最低。除了位永久卡在高电平或低电平的直流故障外,棋盘格算法还可以检测相邻位相互影响的缺陷。

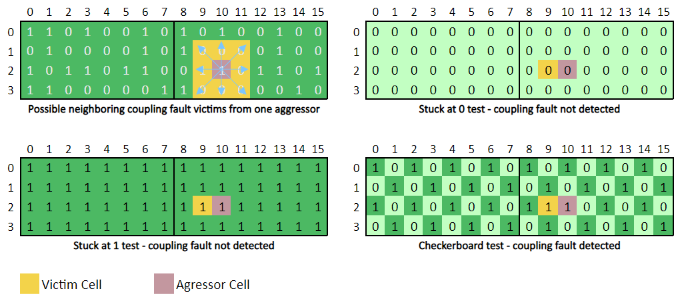

SRAM在逻辑上由许多用单词组织的位组成。这些字通常为 8 位、16 位或 32 位宽,但也可以更长。从物理上讲,这些位被组织成数组,其中每个位通常有八个相邻位(参见图1)。位中的物理缺陷会影响单个位,使其卡在高电平或低电平(直流故障),或者缺陷可能位于两个位的分离中,在这种情况下,相邻的侵略者单元(在图1中以紫色标记)可能会影响受害单元(在图1中以黄色标记)。侵略者-受害者场景通常称为耦合故障。从统计学上看,直流故障更有可能发生,但检测最可能的耦合故障仍然相关。

图1 - 相邻位之间的潜在耦合故障。

如果故障影响单个位,导致该位卡在高电平或低电平,则可以通过写入值 1,通过读回来验证 1,然后写入值零并通过读回来验证零来显示它,如图 1 所示。另一方面,如果缺陷是两个相邻位之间的耦合错误,例如第 2 行中的位列 9 和 10,则某些模式(例如所有 1 或所有 0)不会显示耦合故障,因为单元格在测试期间具有相同的值。

相邻单元(侧面、上方和下方)的耦合故障具有相反的二进制值。图1(右下)说明位10中的位污染了位9,由于位9未保持预期值为零,因此揭示了耦合故障。

SRAM 的物理布局与逻辑布局

为了使棋盘格算法正常工作,需要知道哪些位是相邻位。事实证明这是一个问题,因为数据手册通常只描述SRAM的逻辑布局,而不是SRAM的物理组织方式。

要了解SRAM的物理布局,必须区分面向位的存储器(BOM)和面向字的存储器(WOM),前者当时可以访问一位,后者当时读取和写入n位字。虽然大多数现实世界的内存都是以口碑形式实现的,但科学文献中的经典内存测试算法通常假设BOM实现。

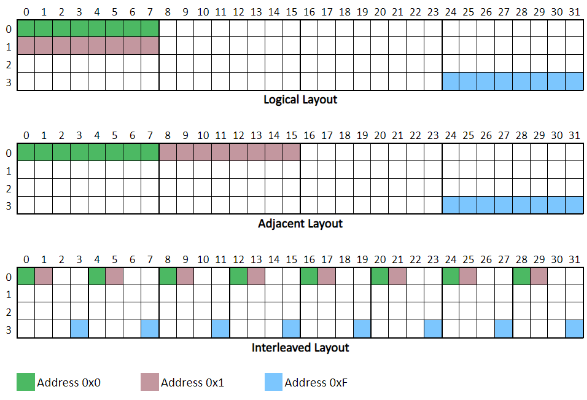

对于口碑记忆,构成单词的位的物理组织主要分为三类:相邻、交错和子数组。逻辑布局将每个单词放在同一列中前一个单词的下方(类似地址空间),而相邻的存储器将每个单词放在同一行中,彼此相邻,如图 2 所示。交错架构将字的每个位分隔到SRAM阵列的不同列和行中。最后,子阵列组织将字的每个位放置在SRAM的不同物理上独立的块中。现实情况是,您不知道物理布局,这是正确实施棋盘格测试所必需的。

图 2 - 面向单词的存储器的物理布局示例。

棋盘格测试的特性和缺点

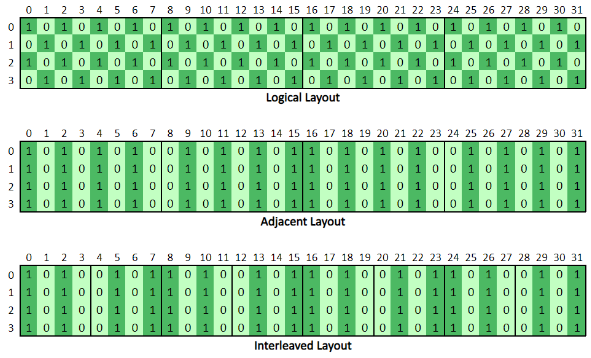

实现棋盘格算法的简单方法是交替地将值0xAA(假设是 8 位数据字)写入第一个地址,0x55写入下一个地址,直到所有被测地址都填充了棋盘格模式 1 和 0。然后验证该模式以检测相邻电池之间的任何直流或耦合故障。然后使用反向模式重复该过程。如前所述,有一个问题:内存逻辑布局中的棋盘图案可能不是底层物理布局中的棋盘图案,如图 3 所示。

图3 - 逻辑SRAM与物理SRAM的数据模式。

补偿逻辑布局和物理布局之间的差异似乎很明显,但器件的数据表中很少提供必要的信息。那么,你会怎么做呢?接受较低的覆盖率,毕竟诊断仍然会覆盖直流故障和相邻位之间的一些耦合故障?向 IC 供应商请求布局,并为每个器件定制棋盘格测试?还是选择其他算法?

现在您已经意识到棋盘测试的潜在缺点,您可以做出明智的决定。

SRAM 运行时测试的替代算法

IEC 60730中针对C类安全级别提出的存储器测试技术具有更高的故障检测覆盖率,但这些算法属于可以被认为是生产测试算法的算法:它们需要更长的运行时间,也可以检测罕见的故障类型,但通常会破坏存储在SRAM中的数据,因为它们在整个SRAM上运行,而不是在子块中运行。

一般来说,对于我们的嵌入式设计,我们不太能容忍这种情况。因此,我们建议您考虑从生产测试三月算法改编的混合三月算法:这些算法可用于 WOM 优化实现并提供高测试覆盖率。此外,可以实现这些混合March算法,以便它们在SRAM的较小重叠部分上运行,以避免一次擦除SRAM中的所有数据,这意味着可以避免重新启动嵌入式系统。March算法的缺点是它们比传统的棋盘格算法计算量更大,但这是安全关键系统中可能需要的费用。

如果您考虑将传统的棋盘格测试换成三月测试,您可以从一些微控制器供应商那里找到这样的实现。Microchip是提供March C-算法的性能优化实现的公司之一,作为其软件诊断库的一部分。Microchip实现支持整个SRAM的测试,通常在启动时完成,只是为了获得最大的测试覆盖率,以及较小的存储器块的测试,旨在减少对应用的实时影响。

审核编辑:郭婷

-

嵌入式电子控制单元(ECU)中如何准确找出运行时使用的RAM量?2024-01-31 880

-

如何在运行时禁用IWDG2019-01-15 2513

-

如何在运行时更新RAM?2019-10-23 2040

-

嵌入式系统能耗怎么实现动态管理?2020-03-24 2034

-

Touchgfx在运行时如何更改整个屏幕?2023-02-08 524

-

运行时软件故障注入器的设计与实现2009-04-06 673

-

嵌入式系统安全处理器的解决方案与设计2010-06-24 377

-

紫金桥组态软件新的功能_运行时组态2017-10-13 1219

-

多核对嵌入式设计原则造成哪些影响2022-06-14 1578

-

设计安全关键型嵌入式系统:在运行时检测SRAM故障的挑战2022-10-24 1219

-

在运行时检测SRAM故障的挑战2022-10-25 2485

-

嵌入式系统中函数如何调用2023-02-13 1987

-

如何在AUTOSAR OS系统运行时使用事件Event呢?2023-05-22 3868

-

如何保证它们容器运行时的安全?2023-11-03 1612

-

Exein设立台湾亚太运营中心:以运行时安全重构物联网全球标准2026-04-24 391

全部0条评论

快来发表一下你的评论吧 !