PCB设计---深入浅出的反弹图

PCB设计---深入浅出的反弹图

描述

作者:一博科技高速先生成员 孙小兵

众所周知,信号的反射与互连线的阻抗密切相关,可以说互连线中阻抗突变是产生信号反射的最直接原因。但究竟为什么会发生反射,反射对信号的影响是什么样的,信号反射的过程又是如何呢?刚好最近也在学习一些信号完整性方面的理论基础知识,也是深受这部分的理论所困惑。下面就和小编一起深入了解一下在传输链路中反射的产生过程和对信号波形的影响吧。

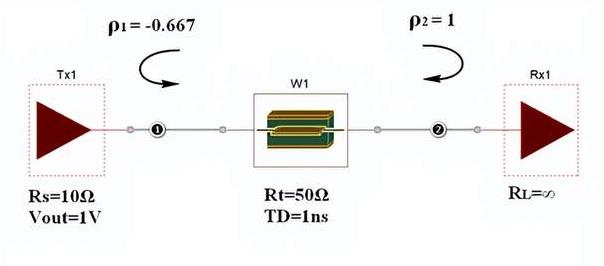

创建了一个简易的信号传输链路模型如下图。信号源驱动内阻Rs为10Ω,输出信号幅度为1V。中间传输线阻抗Rt为50Ω,传输延时TD为1ns。接收端负载阻抗无穷大,相当于远端开路。

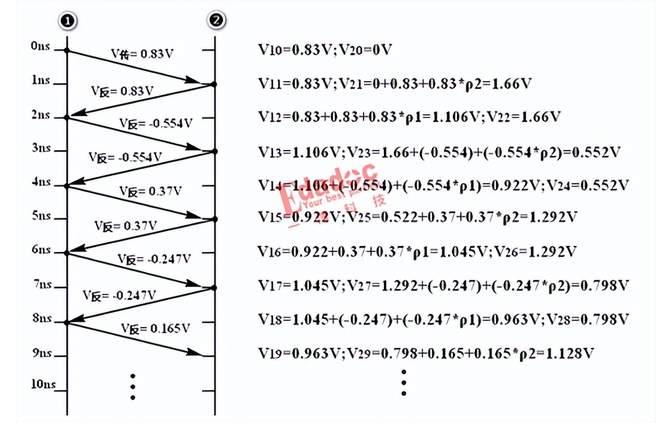

在该链路模型中,节点1位置是从10Ω输出内阻到50Ω传输线,而对于从远端到源端的方向来看,节点1位置是从50Ω传输线到10Ω输出内阻,该节点反射系数ρ1=(10-50)/(50+10)=-0.667。在节点2位置,由于远端开路,在远端反射系数ρ2=(∞-50)/( ∞+50)≈1,信号在该位置将发生全反射。基于该传输模型推导的反射逻辑图如下所示。

1.首先,假定信号边沿开始处为时间0ns位置,此时根据串阻分压,信号源输出的1V电压,经过输出电阻和传输线电阻分压后在节点1位置信号电压V10=1V*50/(10+50)=0.83V。而节点2位置还没有信号,故该时刻电压V20=0V。

2.经过1ns的传输后,信号到达节点2并发生反射,反射电压为0.83V*1=0.83V。此刻节点2位置的电压V21=0V+0.83V+0.83V*1=1.66V。

3.远端的反射信号经过传输线1ns后又会回到源端,并在源端也发生反射,此刻源端的电压V12=0.83V+0.83V+0.83V*(-0.667)=1.106V。由于还没有反射信号回到远端,远端电压V22=1.66V。

4.在源端位置产生的反射信号经过传输线1ns后又重新回到远端,并在远端发生反射,此刻远端的电压V23=1.66V+(-0.554V)+(-0.554V*1) =0.552V。

以此类推……

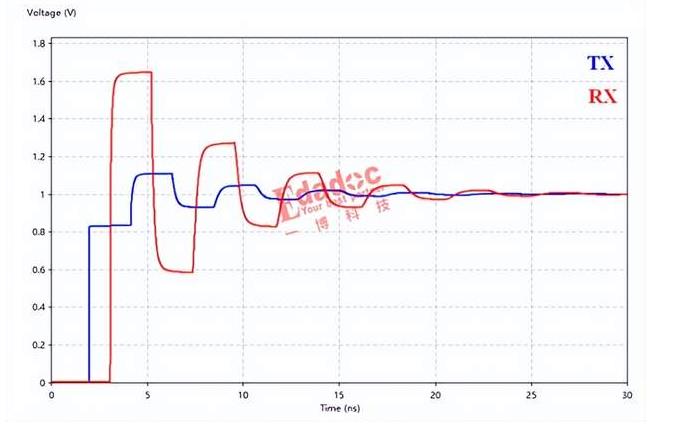

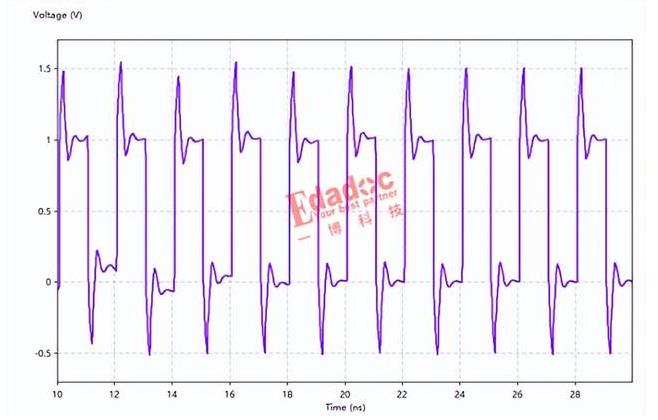

在上述情况下,内阻小于传输线阻抗,在源端位置出现负反射,这将引起通常所说的过冲和振铃现象。如下图所示,蓝色曲线是源端电压波形,红色曲线是远端接收到的电压波形。在此示例中,信号上升边远于传输线时延,而信号周期较大于传输时延。这样能够考虑到所有的多次往返反射和阻抗突变的情况。

由反弹图和以上的红蓝波形图可以看出,反射信号电压的绝对值在逐渐减小,震荡幅度在逐渐减弱,末端的电压最终逼近于信号源电压1V。这是由于该电路是开路的,信号源电压最终全部加在开路的末端。

这时有人可能又会疑惑了,既然信号源输出电压幅度为1V,那为什么会在末端接收到大于信号源的电压值1.66V呢?高出的电压是怎么产生的呢?这是由传输线上的分布电容(C)和分布电感(L)谐振所产生。

以上展示了信号单边沿后的反射全过程。当连续的码元输出后,将会在每一个上升沿和下降沿后的电平保持期间出现振铃现象。高电平最高位置将达到1.66V,低电平最低位置将达到-0.66V。过冲将会导致接收端误触发造成误码,还可能突破电平接收容限,严重的可能损害芯片。

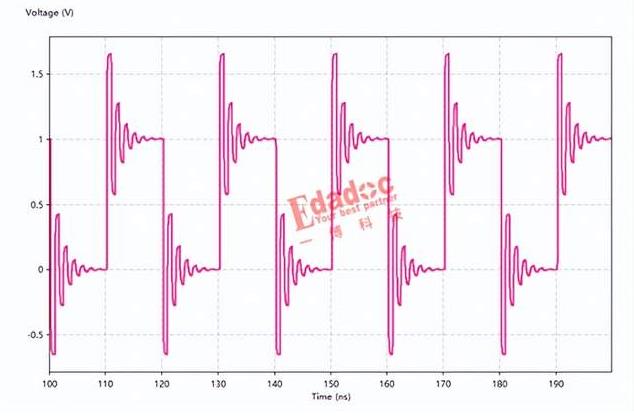

当信号速率升高达到一定程度或走线长度改变时,振铃全过程就不能够有充足的时间在信号平整区间完整的表现出来,后面的震荡将可能会淹没在信号上升沿或者下降沿期间,因而只表现出明显的过冲现象,如下图所示。

前面的链路中信号发生反射主要是由于源端内阻和传输线阻抗不匹配造成的,反射信号在源端和远端来回传输并多次反射形成了一个振铃效应。

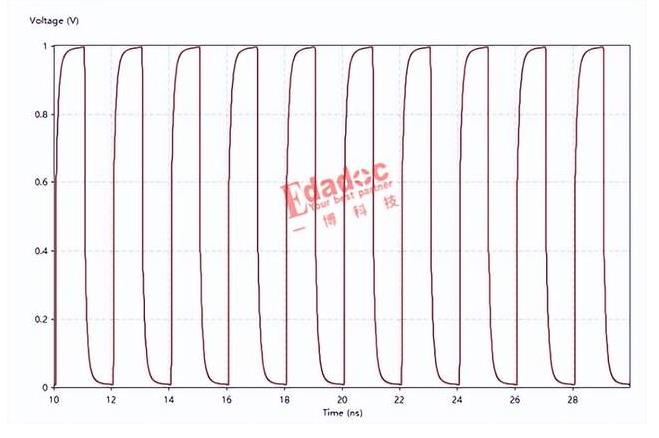

想要改善反射对信号的影响,端接在这里就派上用场了。大家可能都知道端接可以有效的抑制或消除反射。这里就尝试做一个端接处理,在源端位置串联一个40Ω的电阻,链路模型如下:

上图是做了端接处理后远端接收到的信号波形。可以看到反射被消除了,接收端的信号幅度为信号源输出信号电压1V,且信号波形比较完整。

作者:一博科技 edadoc.com 高速先生成员

-

PCB设计---深入浅出的反弹图2022-11-17 2946

-

深入浅出学习250个通信原理资源下载2021-04-12 1052

-

深入浅出数字信号处理2018-12-07 797

-

深入浅出Android—Android开发经典教材2017-10-24 1400

-

深入浅出谈多层面板布线技巧2016-12-13 722

-

深入浅出数据分析2016-01-15 730

-

深入浅出安防视频监控系统2014-05-22 4574

-

深入浅出Android2012-08-20 3144

-

HDMI技术深入浅出2012-08-19 4622

-

深入浅出ARM72012-08-18 5297

-

深入浅出玩转FPGA2012-07-21 4504

-

深入浅出AVR2012-07-15 13396

-

深入浅出AVR(傻孩子)2012-06-29 8945

全部0条评论

快来发表一下你的评论吧 !