EMI实际应用解决方案的学习

EMC/EMI设计

描述

EMI在硬件测试中一直是一个颇为难解的问题,有时会因为负载接线长度和布线等问题变得更为棘手。

在MPS研讨会中基于传输线理论和高频传导EMI进行建模分析,解释高频谐振的产生,并介绍实际应用中解决方案。

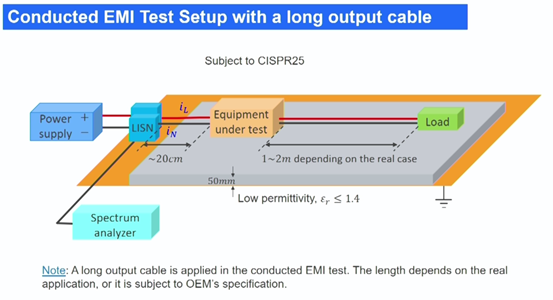

测试过程中环境布置

在有无负载线的情况下进行电源传导对比测试:

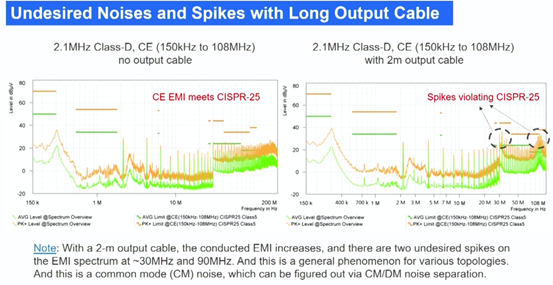

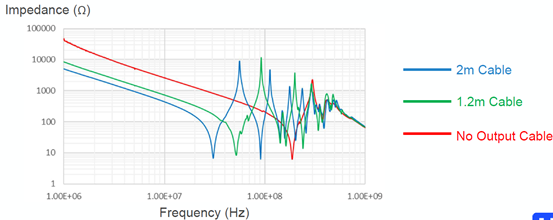

从测试图来看在2m输出线缆在30M和90M出现尖峰。

有四点疑问:为何在加入输出线缆长度后在高频段出现尖峰?不同的长度又会怎样的情况呢?高频EMI是以共模为主?30M、90M 发生谐振?

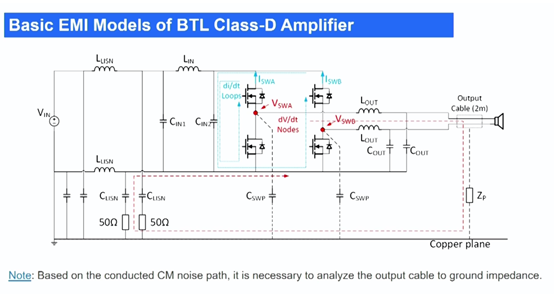

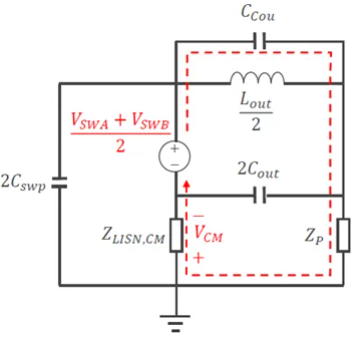

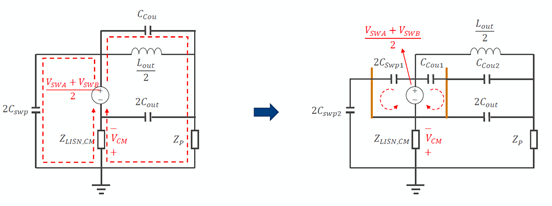

针对测试电路进行建模分析,以下模型基于共模噪声来进行分析:

模型包含Lisn、LC滤波器、H桥开关管、输出线缆、输出对地Zp阻抗,BTL功放H桥不断进行开关,必然会产生di/dt、dv/dt产生噪声源,分别可对它们等效成电流源和电压源,但在共模噪声中di/dt提供的作用小,从环路来主要是dv/dt。在这个模型中,共模电流有两条路径:

①dv/dt-Cswp-Lisn阻容回路

②dv/dt-Lout-Zp-Lisn阻容回路。

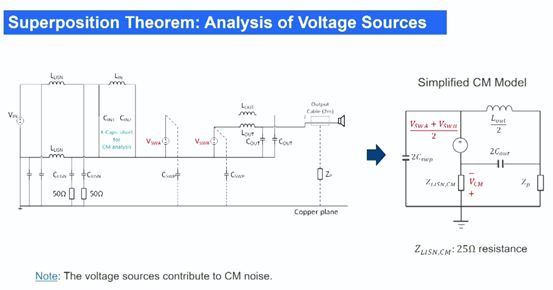

从电压源角度来看模型如下

在近场耦合中会出现耦合电容Ccou,高频的条件下此电容容抗减小,而电感感抗会增大,故共模电流会从耦合电容处流过,并对共模噪声影响很大,共模电流会经过Lisn形成回路。

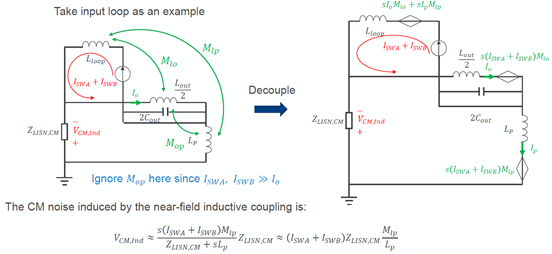

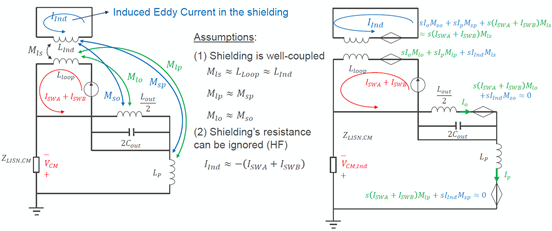

从电流源角度来看模型如下

di/dt形成电流源,变化的电流产生磁场,产生共模噪声需通过互感来形成。

噪声的产生由模型分析可知,那么输出线缆的长度会有怎样的影响,则需从传输线理论来分析。

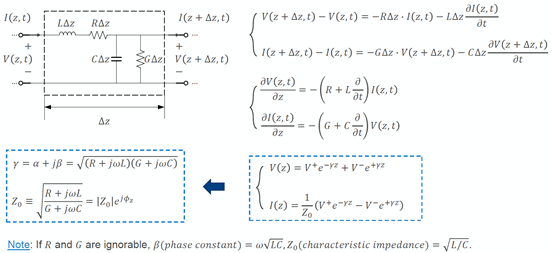

在高频的条件下,任何线缆都是有阻抗的,那这个阻抗的大小会是什么因素来决定?

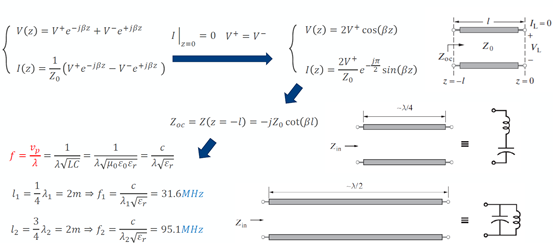

传输线理论一长段理论微分方程和差分方程,对我们应用来分析需理解线缆在高频条件下有阻抗,并且是随频率的变化发生串联谐振和并联谐振,线的长度在波长的1/4时就危险了。线缆在1/4波长时发生串联谐振,那么整个回路中阻抗最小,电流达到最大值,此电流经过Lisn会造成问题。而并联谐振发生时阻抗达到最大,回路电流最小。

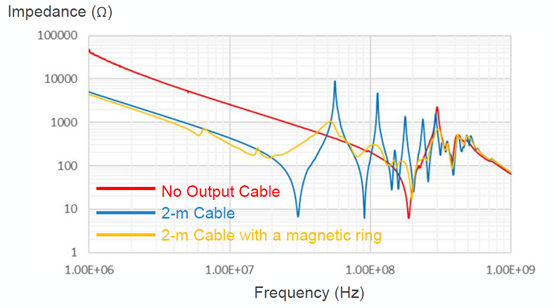

针对此问题,想办法改变谐振点,不然谐振频率落在测试频段内问题能解决,那该如何去操作?

①下图可以看出,不同的线缆长度谐振点不同,从这个角度出发,在适当时候减小线缆长度。

②下图可以看出,在线缆套入磁环可以改变谐振点。

增加屏蔽罩模型

①电压源模型

②电流源模型

增加屏蔽罩中,屏蔽罩需接地,形成新的回路来减小共模电流。

总结一下解决方向:

①减小噪声源

·减小dv/dt变化率

·利用展频技术

②减小噪声路径环路

·减小dv/dt节点大小和di/dt环路面积

·增加滤波器和磁环

·避免线缆长度与1/4、3/4波长相等

·增加屏蔽罩

一己之见:研讨会文档的缘故,整篇文字蕴藏的技术知识点含量很高,有近远场的距离分界点λ/2π,有传输线特性阻抗公式,有展频技术,三角波。还有1/4波长的奇数倍,这里让我想起为什么是1/4λ?为什么是奇数倍?提示一下:90°+90°=180°……

最后说一下电流源和电压源:

电流源可以理解成一个理想电源(没有内阻)与一个电阻(此电阻无穷大,相对于外接负载)并联。电压源是从实际电源抽象出来的一种模型,可以理解成在其两端总能保持一定的电压而不论流过的电流为多少。这里讲电流源和电压源模型,这个还真一时想不起来。

整篇文章看下来,越来越觉得EM才是信号完整性的基础。

审核编辑:汤梓红

-

立体智慧仓储解决方案.#云计算学习电子知识 2022-10-06

-

EMC/EMI综合解决方案与设计经验分享2011-07-11 0

-

LTC6909是EMI的理想解决方案2019-07-23 0

-

RS预兼容EMI测试解决方案2019-10-15 0

-

减少峰值EMI解决方案2009-02-08 657

-

印刷电路板(PCB)设计中的EMI解决方案2009-04-15 754

-

DSP系统中的EMC和EMI的解决方案2010-02-24 1005

-

Laird 完整的EMI及导热解决方案2016-12-14 901

-

EMI抑制解决方案2017-09-11 910

-

减少EMI和收缩解决方案的方法介绍2018-08-16 2745

-

低EMI电源解决方案2018-08-18 4832

-

贸泽电子推出EMI全新解决方案2018-08-30 5474

-

关于预兼容EMI测试解决方案的详细介绍2020-07-23 953

-

车载多媒体EMI的解决方案详细说明2020-04-14 888

-

开关稳压器的 EMI 解决方案2021-03-21 550

全部0条评论

快来发表一下你的评论吧 !