高K金属栅工艺(HKMG)

描述

随着晶体管尺寸的不断缩小,为保证栅控能力,需要维持足够的栅电容,因此要求栅氧厚度继续减薄。然而,当栅氧物理厚度减薄到低于 1.5nm时,由于直接隧道效应指数级增加,器件漏电随之大幅增加,从而导致器件无法实际工作。通过将相对介电常数(Relative Dielectrie Constant) 远大于 SiO2(K大约3.9)的高K栅介质材料导入集成电路工艺,如HfO2(相对介电常数为 24~40),可以在保证等效栅氧厚度(Equivalent Oxide Thickness, EOT)持续缩小的前提下,使栅介质的物理厚度相对较大,以抑制栅泄漏电流。然后用TaN、TiN 、TiAI、W 等金属合金或化合物叠层结构取代多晶硅栅,金属叠层具有功函数调节和降低电阻率等作用,可避免多晶硅栅的耗尽效应,同时保证高k栅介质材料与金属栅有较好的接触效果。

目前,高K栅介质与金属栅极技术已广泛应用于 28mmn 以下高性能产品的制造,它在相同功耗情况下可以使集成电路的性能大幅度提高,泄漏电流大幅下降。高K金属栅的应用经历了较长的探索过程:在很长的时间里,晶体管的栅氧化层都是采用高温干法或湿法热氧化硅形成氧化层;后来为了提高 氧化层的介电常数,在氧化过程中掺入N元素形成 SiON栅介质层;随着栅多晶硅厚度的降低,不仅导致电阻变大,还列起器件延迟和栅耗尽效应。在此背景下,在28nm这个工艺节点,工业界大多开始使用 HKMG 作为超大规模集成电路的标准工艺,虽然性能得到大幅提升,但也大大增加了工艺复杂度。

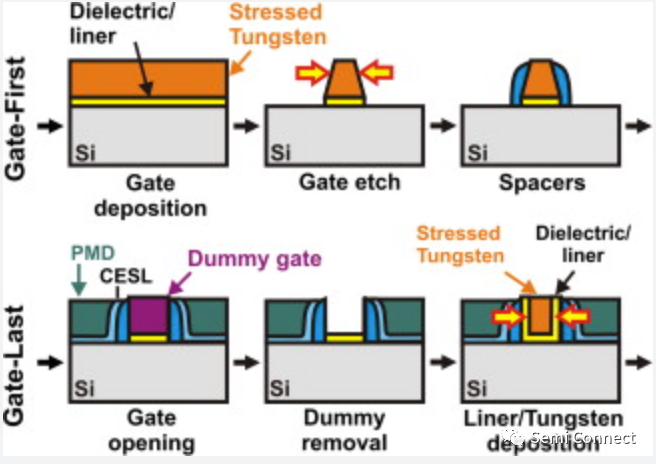

由于HKMG与 Poly/SiO2的 MOSFET结构有很大的不同,导致整个器件的工艺条件发生巨大变化,而且大量的 IP 核需要重新设计。 在最初的工艺开发阶段,业内存在两种制作HKMG 结构晶体管的工艺技术路线,分别是 Gate-Fiest(先栅极)工艺和 Gate-Last(后栅极)工艺。 Gate-First 工艺相对简单,但是 p-MOS 阈值电压很难控制;而 Gate-Last 工艺比较复杂,但它可以有效地调节栅极材料的功函数值,方便调节阈值电压,还可以在p-MOS 的沟道实现改善沟道载流子迁移率的硅应变力。在同时兼顾高性能与低功耗的情况下(如手机应用处理器和基带芯片等),Gate-Last 工艺逐渐取得优势,是目前大规模生产中的主流工艺。

审核编辑 :李倩

-

HKMG实现工艺的两大流派及其详解2010-03-23 8585

-

GLOBALFOUNDRIES德累斯顿工厂出货第25万枚32纳米HKMG晶圆2012-03-23 1068

-

深入赛灵思Kintex-7 FPGA内部:透视HKMG技术2012-04-13 6480

-

高介电常数栅电介质/金属栅极的FA CMP技术2012-05-04 8222

-

IMEC发布后栅极HKMG制式细节,英特尔、三星受益2012-06-14 1915

-

专访格罗方德Subramani Kengeri:28nm量产致胜关键在于HKMG2012-07-15 6093

-

基于主流的体硅高κ/金属栅FinFET工艺,提出了一种利用拐角效应2021-02-20 5161

-

集成电路制造工艺的演进2022-09-06 3291

-

SK海力士全球首次在移动端DRAM制造上采用HKMG工艺2022-11-11 2400

-

高K介质(High-k Dielectric)和替代金属栅(RMG)工艺介绍2023-01-11 14021

-

平面互补场效应晶体管替代金属栅工艺流程2023-01-17 4064

-

ICT技术高k金属栅(HKMG)的工艺过程简析2023-08-25 7884

-

高k金属栅(HKMG)工艺详解2024-01-19 31929

-

高K金属栅极的结构、材料、优势以及工艺流程2024-11-25 6984

-

集成电路新突破:HKMG工艺引领性能革命2025-01-22 5006

全部0条评论

快来发表一下你的评论吧 !