芯片的流片制造那些事儿

EDA/IC设计

描述

今天我们讲讲芯片的流片制造那些事儿。这个流程的输入是设计的版图文件,输出是做好的芯片晶圆。

这是芯片的第四个流程。这块儿,我国65nm这个量级的做的还可以,14nm应该SMIC也凑活,先进制程7乃至5nm的商业化基本是空白。属于真正被大洋彼岸卡脖子的部分。这篇文章科普一下整个制造流程。技术部分应该比较少,所以我们讲点儿故事。管中窥豹,我们的故事不妨从台积电展开。

二、台积电的过往

我们说芯片代工厂,你第一个想到的是什么?我想做芯片的大部分人可能脱口而出就一个——台积电(TSMC),全称是某省积体电路制造股份有限公司。积体电路就是集成电路的一种叫法,类似于把菠萝叫凤梨。中国人似乎讲究周期。台积电基本上恰好10年一个周期。

台积电的第一个十年——蹒跚起步

85年,德州仪器的一个哥们回岛了。他属于最早进入这个邻域的一批人,在德州仪器属于三号人物。在岛内混了几年,1987年,55岁的他决定搞个厂糊口(同年,深圳一个43岁的哥们也准备搞个厂糊口,你应当听说过)。这家厂子一开始就给自己定位成代工厂,不做设计,只负责制造。和大部分创业公司一样,台积电的前三年也经历了好多庙小妖风大的挫折,不过好歹,张忠谋在美帝有些人脉,1990年,英特尔CEO正想着怎么把公司中心从存储转到CPU上,经过张忠谋这么一忽悠,单子可不就来了么。英特尔老大哥帮台积电实现了第一次飞跃。

台积电的第二个十年——发展壮大

转眼,1997年,台积电已经成立10年了。一家公司,要是能活10年,确实有点东西的,遭到山寨也在所难免。这个时候另一个德州仪器的哥们叫张汝京的,回岛山寨了一个台积电出来,叫世大半导体。三年达到台积电30%产能。台积电一气之下就发动钞能力说动世大的股东把世大给买了。张汝京跑路到上海,建了另一个厂,叫SMIC,这是后话。这个阶段台积电过的有滋有味,不过和英特尔比它始终是个弟弟。全球最好的制程都在英特尔手中。

台积电的第三个十年——走向风口

日月如梭,2007年,一个穿着黑T恤和牛仔裤的哥们从裤兜里掏出一个手机。消费电子的时代到来了。台积电赶上了手机这波热潮。手机讲究一代手机,一代芯片。制程跟不上哪行,至此除了三星和英特人,其他家都选择了台积电的代工厂模式。2014年,张忠谋搞个了夜莺计划,从此,代工厂三班倒的时代到来了。这个时候英特尔不再那么遥远,慢慢超越了。

台积电的第四个十年——对抗 or 合作?

2017年,一个叫梁孟松的人回国加入了SMIC,隐约记得一个以前在中芯国际的哥们说,当年中芯国际为了请他来,把一层楼给他做办公室。他是台积电元老,09年离开台积电。去了三星,然后三星就越来越长的像台积电,在14nm工艺上甚至摆了TSMC一道。台积电一纸诉状让梁孟松离开了三星,结果2017年,他到了SMIC。虽然2020年蒋尚义归来,梁准备离开,但反映出的一个趋势值得我们注意。大陆不愿意在这个事儿上被卡脖子了。有人这么说过,中国其实是一个伪装成国家的文明,除非你有本事直接卡断脖子,否则非常容易集中力量办大事,给你甩出一个京东方出来。台积电后续怎么发展,我们拭目以待2027年。

二、芯片的制造流程

我们扯了一堆台积电,那么台积电到底怎么用沙子把版图造成芯片的?这个流程的图我是从intel 《From Sand to Silicon》这篇文章里贴的。

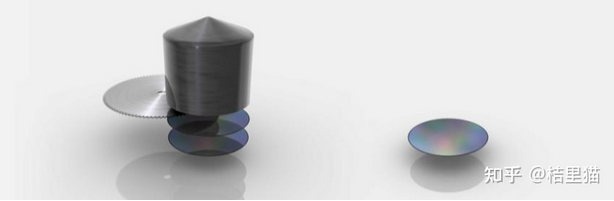

step1, 挖沙子,然后做成硅锭

其中,硅要足够的纯,要9个9,99.9999999%纯度。我们为什么要用SI做芯片?也简单,硅是半导体,能做开关,世界上沙子也多,还容易提纯,与是就决定是它了。

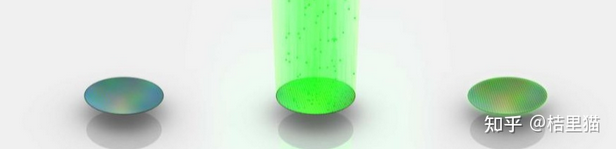

step2, 硅锭切成硅片

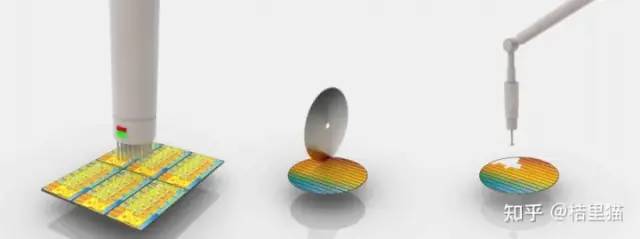

将硅锭切成1mm左右一片片的wafer(晶圆)。晶圆尺寸有大有小,比如8inch, 12inch的晶圆,光刻的时候直接刻整个圆,然后切下来好多小芯片。

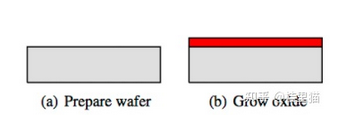

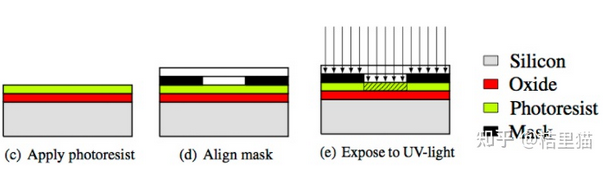

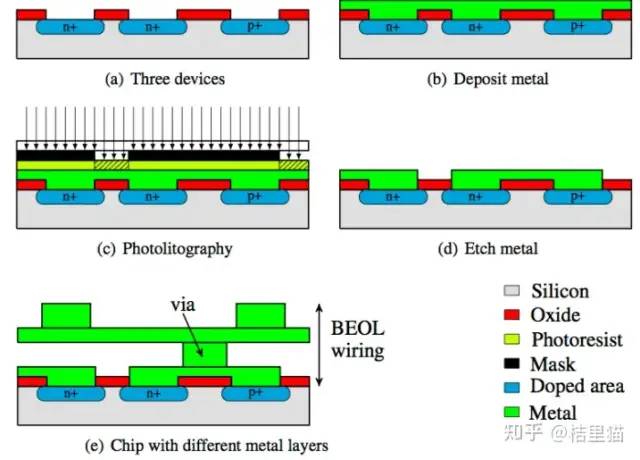

硅片切好以后,需要在上面氧化一层二氧化硅,用来做栅极。我们来看看下面的剖面图,红色的就是二氧化硅。

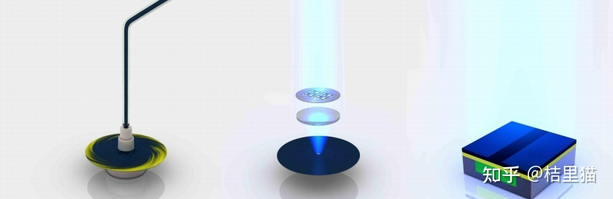

step3, 光刻

这个步骤首先在硅片上抹上一层光刻胶,一般来讲光一照,光刻胶就溶解(正胶)。然后用做好的掩模mask来照射wafer。

我们看上面这个剖面图,黄色的就是我们加入的光刻胶。黑色是我们根据版图制作出来的模板。然后用UV光去照,把光刻胶镂空。

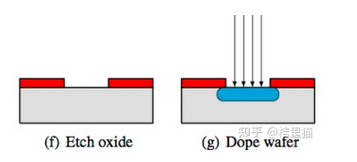

step4, 刻蚀与粒子注入

这个步骤,我们用药水把oxide刻蚀了,然后把光刻胶洗掉,最后注入离子。

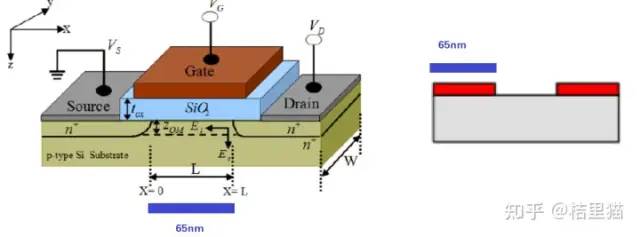

我们看剖面图。f就是刻好的oxide. 然后在洞里注入离子,形成源极和漏极。至此我们的晶体管就造好了。

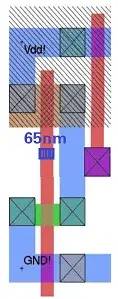

此处要插播一个小知识。我们平时说的工艺制程,比如28nm, 14nm指的是晶体管栅极宽度,也就是导电沟道的长度,不是指的线宽,最小线宽一般比制程要粗了现在。我在图上标注了65nm指的是什么。

在GDS版图上是这个距离,下面画了个非门的版图。

step5 金属线制作

这个步骤主要是上硅片上连上金属线。这个过程我们依旧看下面的剖面图比较清楚。

看b图,首先在上面电镀一层金属,c图用光刻胶和掩膜版再刻蚀一遍得到d图,然后一层一层刻蚀叠加起来就行,层与层之间只有固定的通孔via用于连接。

step6 硅片测试与切片

接下来代工厂还要做几个事儿。

第一件事儿是先检查一下晶圆和芯片是不是好的。主要包含了两个测试。

WAT (Wafer Acceptance Test), 这个主要是测试一下晶圆的电学特性是不是正常的。WAT测试电路代工厂在流片的时候就直接加入到晶圆里了,主要包括了各种晶体管参数比如阈值电压,漏电流,电阻,电容是不是正常的。WAT的测试向量是代工厂自己搞的。

CP(Chip Probing)测试。WAT测试没问题以后,接下来进行CP测试,先用探针看看芯片是不是好的,有问题的芯片直接扔掉,免得浪费封装成本。一般会用到前面讲的DFT三把斧,sacn chain, JTAG, BIST。CP测试向量由设计商提供。如果CP不合格,直接标记出来,扔掉。

CP测试完了以后,就把芯片按照划片槽切成一个个小的芯片,装盒。寄出来了。

三、总结

这篇文章我们一起回忆了一下台积电的往事,同时对芯片在代工厂的流程做了大概的讲解。实际上芯片的制作的工艺流程要复杂非常多,比如现在制程越来越小,光刻的时候量子隧穿效应非常严重,做出来模板肯定不是你想想的镂空的窗花,这里只是讲了最重要最基础的步骤。这篇文章的输入是设计的GDS, 输出是一个个芯片裸片。这些裸片没办法直接接到PCB上的,需要经过后续的封装和测试,才算是真正的芯片。

编辑:黄飞

-

芯片设计流片、验证、成本的那些事2024-08-09 4435

-

流片失败那些事儿 如何提高芯片一次流片成功率降低设计成本?2024-01-19 7512

-

什么是芯片流片?芯片流片为什么这么贵?2023-11-30 7899

-

聊聊芯片设计、流片、验证、制造、成本的那些事2023-10-07 5437

-

芯片流片是什么意思 芯片流片流程介绍2023-09-02 17613

-

讲讲芯片的流片制造那些事儿2023-02-02 5248

-

Linux内存的那些事儿2022-09-08 1305

-

MOS管的那些事儿.课件下载2021-12-06 1497

-

Linux的那些事儿之我是Sysfs2017-10-29 1166

-

电源选型的那些事儿2016-10-10 965

全部0条评论

快来发表一下你的评论吧 !