PCB设计仿真之探讨源端串联端接

描述

作者:一博科技高速先生成员 孙宜文

上期高速线生简单介绍了反射原理也提到了源端串联端接,笔者借此篇文章再深入探讨下,本文使用Sigrity Topology Explorer 17.4仿真软件。

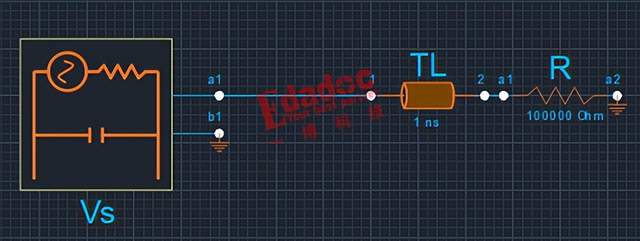

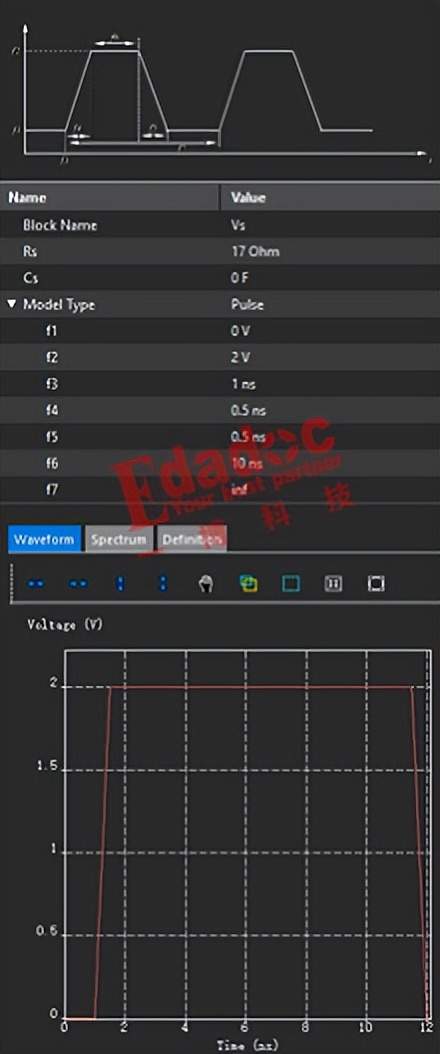

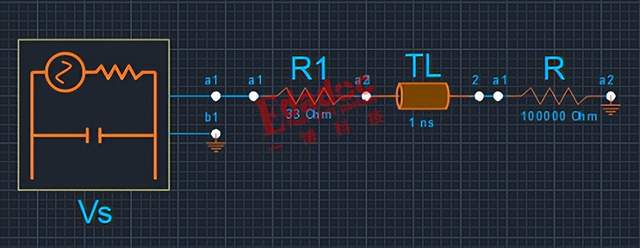

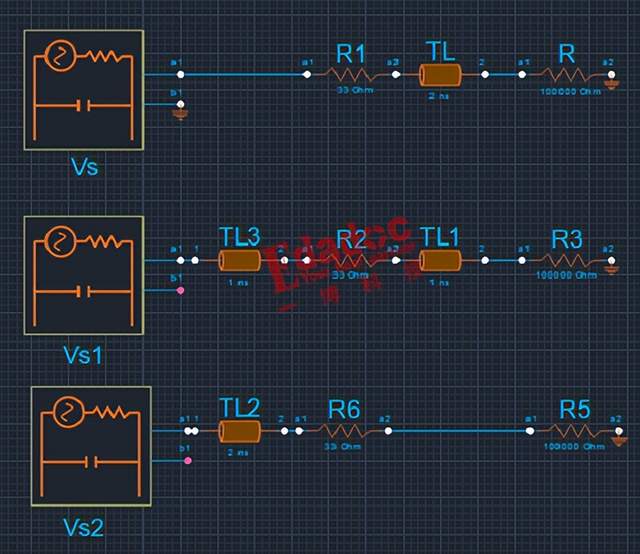

搭建一个简单的电路模型,给一个上升沿和下降沿均为0.5ns的脉冲波形,电压跳变为0V-2V-0V,高电平持续时间为10ns,假定芯片内部驱动17ohm,路径中传输线的时延为1ns,一起看下这个链路的接收端和发送端波形:

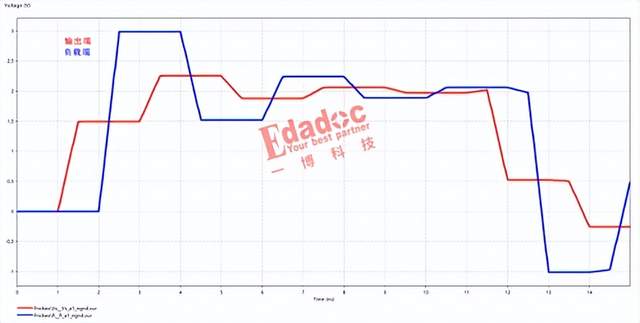

仿真结果:

传输线阻抗50ohm,通道末端开路。实际电路在工作的时候,末端通常是高阻状态,也就是和开路差不多。信号到达末端全反射,每个时间阶段观测点的电压值这里就不做解释了,感兴趣的读者可以结合反射系数计算。

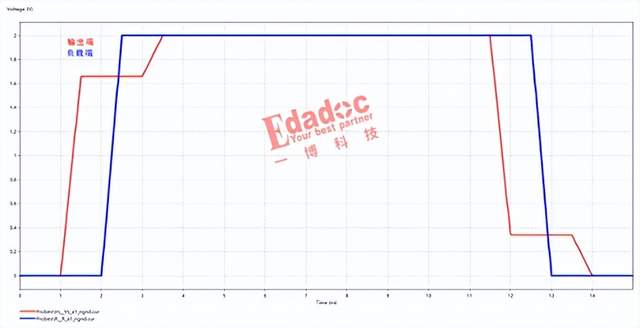

负载端接收到信号过冲很大,当在靠近源端的地方加上33ohm的电阻后仿真结果如下:

源端阻抗得到匹配

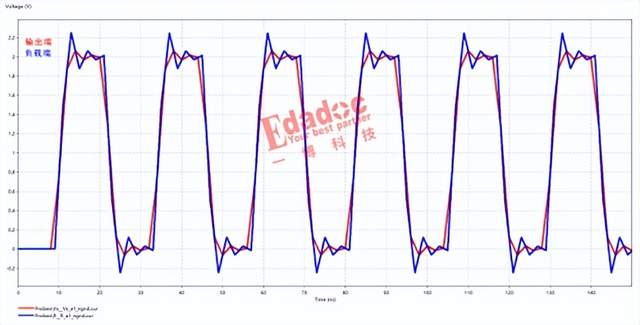

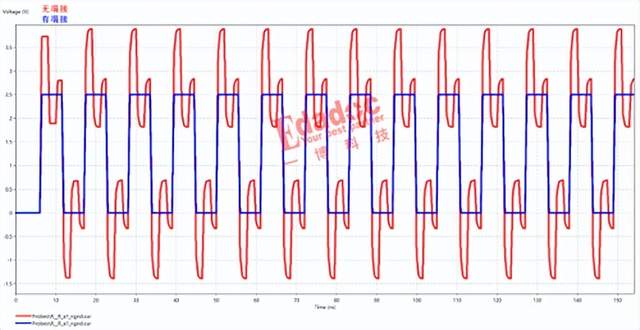

接下来我们用实际情况做例子,模拟一个33Mbps的local bus信号,发现无端接时候的信号波形,只有一点小小的过冲,是一个还不错的信号波形。

但我们把速率调到200Mbps,大概是DDR1的速率,发现不端接会有很大的过冲。

看来随着速率的提高,阻抗不匹配的链路中,源端串联还是有必要的。那么我们该如何判断何时需要端接?

这里和信号的上升时间Tr及传输线延时TD有关,下面有个经验公式可提供参考:

TD=20%Tr

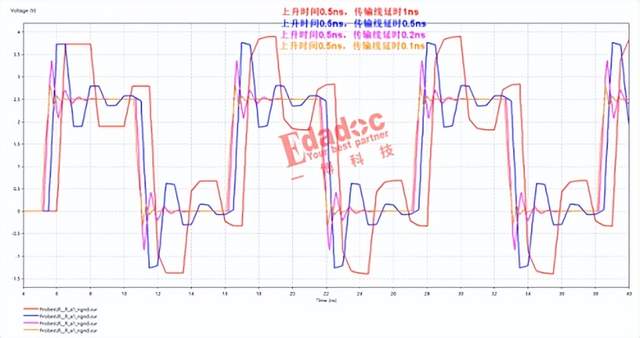

我们来验证下公式,拿刚才的示例继续仿真,调整参数,上升时间是0.5ns,传输线延时是1ns,递减传输线延时,从1ns逐渐减小至0.1ns(20%Tr),观察负载端的信号质量。

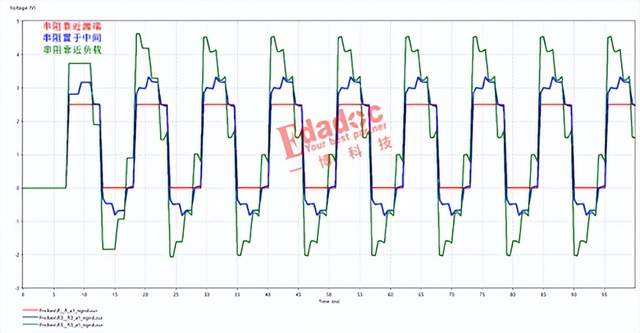

看起来,Tr减小到0.1ns的时候,反射噪声约为12%,不同的结构,不同的信号要求不同,具体看信号能容忍多大的噪声,仅作为快速定位的经验参考。另外需要注意串阻需要尽量靠近源端,不然会引起多次反射,降低端接效果,甚至导致信号更差,来看下不同位置的串阻带来的影响。

文末总结下源端串联端接的优点:

源端串联通过靠近芯片发送端串联电阻,使得该串联电阻与芯片的内阻之和尽量与传输线阻抗一致。该端接简单功耗小,不会给驱动器带来额外的直流负载,只需要一个电阻就可以抑制驱动端到负载端的二次反射,常适用于点对点的拓扑上。

审核编辑:汤梓红

-

飞凌嵌入式 ELFBOARD之传输信号的不同端接方式2024-07-16 2727

-

双向收发的信号应该在哪进行串联端接?分享几个实用设计方法!2024-07-12 2268

-

传输线在阻抗匹配时串联端接电阻为什么要靠近发送端?2023-11-22 2594

-

传输线在阻抗匹配时串联端接电阻为什么要靠近发送端2023-11-07 2887

-

探究电阻布局对端接效果的影响2023-02-27 706

-

PCB设计仿真之探讨源端串联端接2022-11-22 3080

-

高速数字设计第6章 端接2022-09-20 458

-

PCB设计的几类端接方法的差别2020-07-01 1835

-

高速电路中电阻端接的作用2020-03-16 2764

-

PCB设计之电容2019-08-13 3747

-

高速PCB的终端端接方式浅析2019-06-03 2006

-

端接的仿真分析2018-11-27 1694

-

端接介绍及其种类2016-06-13 2989

全部0条评论

快来发表一下你的评论吧 !