中科院研发出高性能单晶硅沟道3D NOR储存器

描述

NOR闪存以速度快、可靠性高和使用寿命长等优势,在人工智能、汽车电子和工业领域中发挥着重要作用。目前,普遍使用的平面NOR闪存在50纳米以下技术代的尺寸微缩遇到瓶颈,难以进一步提升集成密度、优化器件性能以及降低制造成本。为突破上述瓶颈,科研人员提出多种基于多晶硅沟道的三维NOR(3D NOR)器件,但多晶硅沟道迁移率低、读取速度慢,影响NOR器件整体性能。

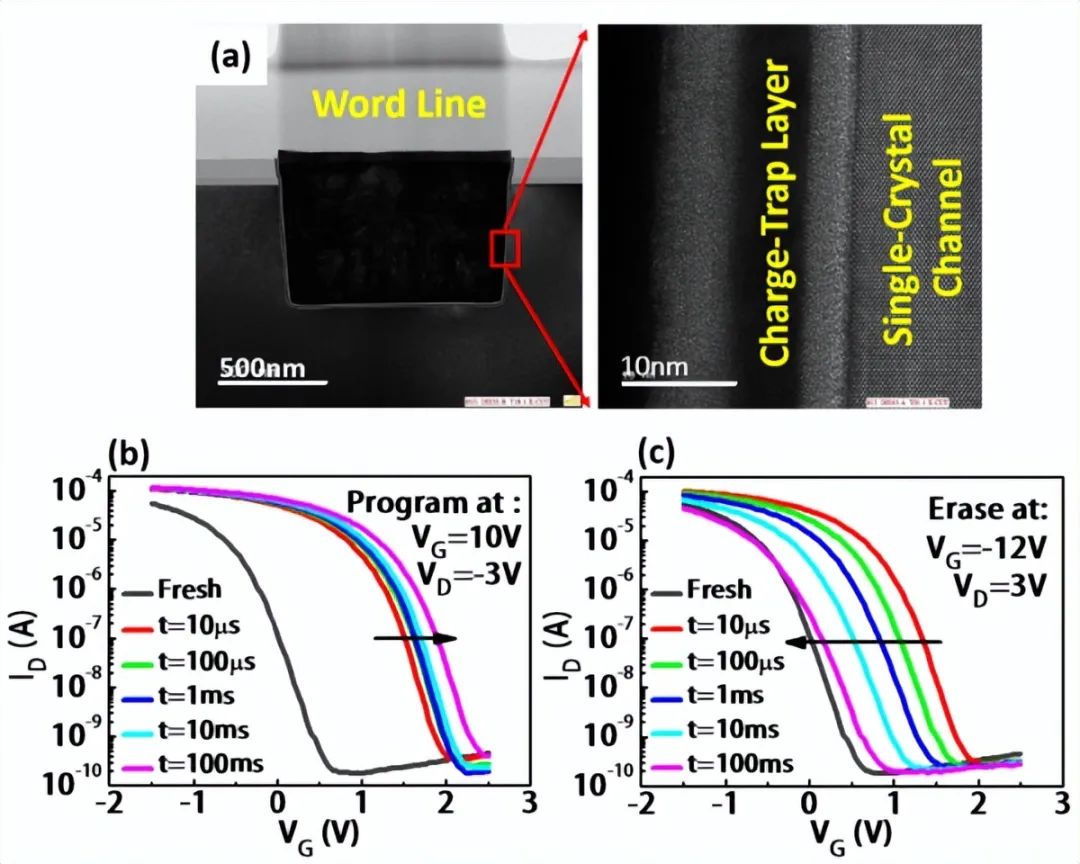

近日,中国科学院微电子研究所集成电路先导工艺研发中心研究员朱慧珑团队利用研发的垂直晶体管新工艺,制备出高性能的单晶沟道3D NOR闪存器件。该器件上下叠置的晶体管既具单晶硅沟道的高性能优势,又具三维一体集成的制造成本低的优点。该器件可在获得同等或优于单晶硅沟道平面NOR闪存器件性能的同时,无需升级光刻机也可大幅提高存储器集成密度、增加存储容量。科研团队研制的3′3′2三维NOR闪存阵列实现了正常读写和擦除,达到了读电流及编程、擦除速度与二维NOR闪存器件相当的目标,且新制程与主流硅基工艺兼容,便于应用。

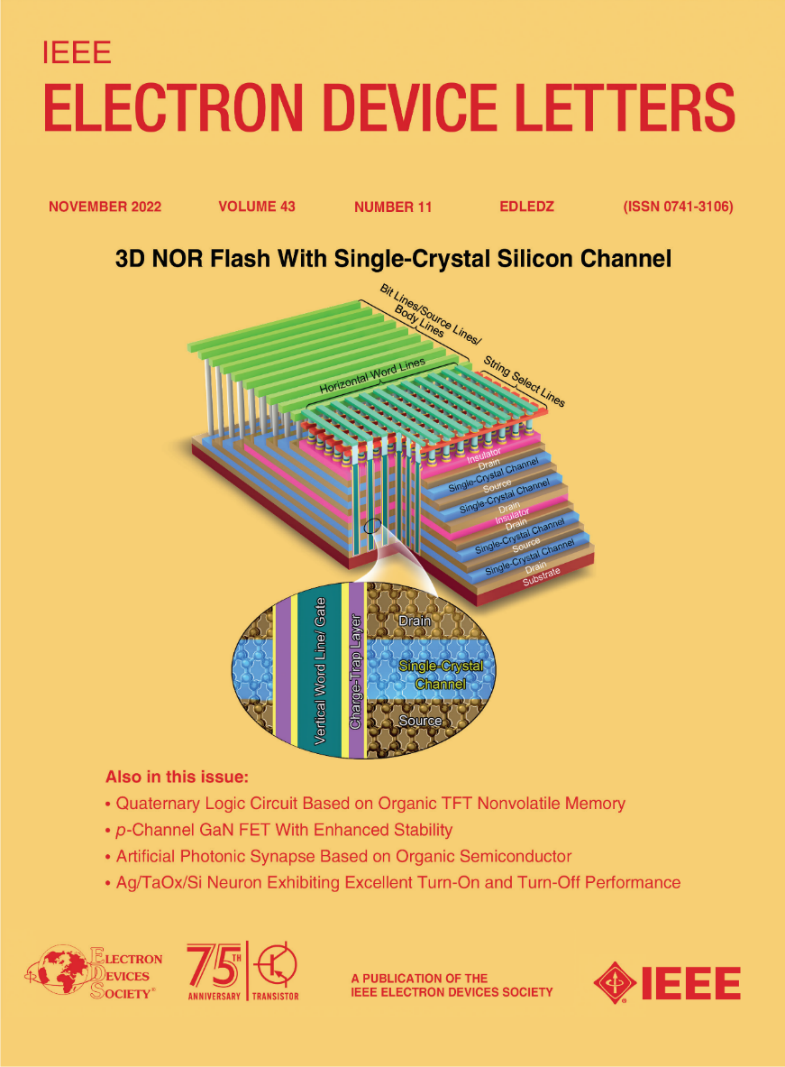

相关研究成果作为封面文章和“编辑特选”(Editors Picks)文章,以A Novel 3D NOR Flash with Single-Crystal Silicon Channel: Devices, Integration, and Architecture为题,发表在《电子器件快报》(IEEE Electron Device Letters)上。研究工作得到中科院自主部署项目的支持。

图1.刊登在Electron Device Letters封面上的单晶硅3D NOR电路架构(上)及垂直沟道晶体管结构(下)

图2.单晶硅沟道3D NOR器件及电性实验结果:(a)器件TEM截图(左)及沟道局部放大图(右),(b)编程特性,(c)擦除特性

审核编辑 :李倩

-

n型单晶硅退火工艺2011-03-01 3365

-

中科院剖析 LED怎样克服困难2012-07-18 8438

-

156单晶硅不同扩散方阻下的功率对比2012-08-06 3819

-

中科院深耕网络摄像机领域2015-02-05 5289

-

中科院3D打印机CEST400|国产工业级3D打印机2018-08-10 3267

-

中科院发布“香山”与“傲来”两项开源处理器芯片2023-05-28 6189

-

单晶硅与多晶硅的区别2009-03-04 5015

-

什么是单晶硅2009-04-08 12084

-

中科院_遥感课件及资料32016-05-05 617

-

单晶硅的制造方法和设备和分离单晶硅埚底料中石英的工艺2017-09-28 2098

-

全球单晶硅生产商排名2017-12-18 56309

-

一种高性能单晶硅沟道3D NOR储存器2022-11-24 764

-

研究团队研发高性能单晶硅沟道3D NOR存储器2022-12-22 1094

-

单晶硅和多晶硅的区别2023-06-12 8242

-

什么是单晶硅光伏板?单晶硅光伏板优缺点2023-11-29 6237

全部0条评论

快来发表一下你的评论吧 !