日月光扇出型封装结构有效提升计算性能

制造/封装

描述

日月光的扇出型封装结构专利,通过伪凸块增加了第一电子元件和线路层之间的连接强度,减少了封装件的变形,并且减小了填充层破裂的风险,有效提高扇出型封装结构的良率。

日月光半导体近日宣布,其先进封装VIPack平台,推出业界首创的FOCoS扇出型封装技术,解决了传统覆晶封装将系统单芯片(SoC)组装在基板上的局限性,将两个或多个芯片重组为扇出模组。

在扇出型封装结构中,尤其是扇出型衬底上芯片(FOCOS)封装,各材料间热膨胀系数(CTE)不匹配,在热循环过程中会产生翘曲,而整体结构无法直接释放翘曲所产生的应力,因此位于应力集中点的电子元件周围容易产生破裂而直接往下破坏线路层。

为此,日月光于2021年9月17日申请了一项名为“扇出型封装结构”的发明专利(申请号: 20211109373.1),申请人为日月光半导体制造股份有限公司。

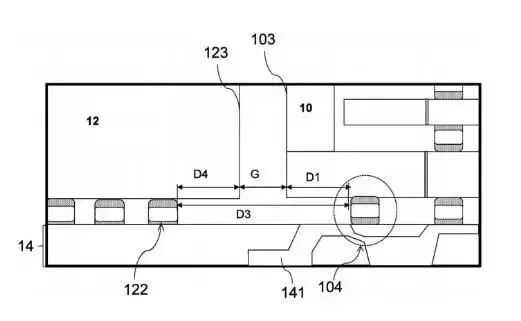

图1 扇出型封装结构和电子元件的示意图

图1为扇出型封装结构和电子元件的示意图,其中包括并排设置的第一电子元件10和第二电子元件12,以及二者下方的线路层14。还包括:填充层16,包覆第一电子元件和第二电子元件,二者通过填充层隔开。填充层包括模制化合物或底部填充胶或粘合层,位于第一电子元件、第二电子元件和线路层之间,第一电子元件的功能凸块阵列102和伪凸块104穿过粘合层。填充层和粘合层的热膨胀系数不同。粘合层的材料包括聚酰亚胺,在封装件受热时,由于线路层所在的一侧的填充层及粘合层较多,线路层所在的一侧的变形(膨胀)较大。

因此,在线路层所在的一侧的填充层具有破裂的风险。本申请的实施例的伪凸块增加了第一电子元件和线路层之间的连接强度,减少了封装件的变形,并且减小了填充层破裂的风险。

在一些实施例中,第二电子元件的横向尺寸大于第一半导体管芯的横向尺寸。第二电子元件周围有多个第一电子元件。第一电子元件是高带宽存储器(HBM)管芯,第二电子元件是特定应用集成电路(ASIC)芯片,第一电子元件和第二电子元件的热膨胀系数不同。

第一电子元件包括:功能凸块阵列,位于第一电子元件的下表面101的中心处;伪凸块,位于功能凸块阵列和第一电子元件的下表面的边界103之间。第二电子元件和第一电子元件的功能凸块阵列电连接至线路层,第一电子元件的伪凸块物理接触线路层。伪凸块与边界之间具有第一距离D1,与功能凸块阵列之间具有第二距离D2,第一距离D1小于第二距离D2。

第二电子元件的下表面具有第二凸块122,第二凸块与伪凸块之间具有第三距离D3,第一距离D1与第三距离D3的比值位于0至0 .5的范围内。第一电子元件和第二电子元件之间的间距拉大,降低了应力集中导致的底胶(填充层)破裂问题。

简而言之,日月光的扇出型封装结构专利,通过伪凸块增加了第一电子元件和线路层之间的连接强度,减少了封装件的变形,并且减小了填充层破裂的风险,有效提高扇出型封装结构的良率。

日月光为全球领先半导体封装与测试制造服务公司,提供芯片前段测试及晶圆针测至后段封装、材料及成品测试的一元化服务。日月光提供完善的电子制造整体解决方案,以卓越技术及创新思维服务半导体、电子与数字科技市场。

审核编辑:汤梓红

-

强强合作 西门子与日月光合作开发 VIPack 先进封装平台工作流程2025-10-23 4691

-

日月光斥资2亿美元投建面板级扇出型封装量产线2025-02-18 1719

-

日月光扩大CoWoS先进封装产能2025-02-08 1653

-

日月光资本支出加码,先进封装营收明年望倍增2024-07-27 1823

-

消息称日月光拿下苹果 M4 芯片先进封装订单2024-03-19 876

-

日月光加大资本支出,扩充先进封装产能2024-02-03 1594

-

日月光推出整合设计生态系统IDE2023-10-18 1679

-

日月光半导体推出VIPack™先进封装平台2022-06-02 2839

-

最新!日月光昆山厂因限电停产2021-09-27 27574

-

日月光投控积极布局封装技术有成2021-01-13 2800

-

日月光5G天线封装产品预估明年量产 另外扇出型封装制程供应美系和中国大陆芯片厂商2019-09-17 4467

-

紫光抛售所持日月光相关股份2019-07-14 4488

-

冲中低阶封装 日月光要收购洋鼎2011-12-29 878

-

日月光或将考虑并购日月鸿2011-12-13 1182

全部0条评论

快来发表一下你的评论吧 !