峰峰值频率监测

描述

频率监控电路有多种类型。“过零检测器”被认为是最常见的方法之一,因为它对周期性和常规信号的设计简单。但是,如果信号是非周期性的或不规则的(脉冲之间包含非瞬时零周期),则不能使用过零。在这种情况下,峰峰值频率监视器是理想的替代方案。

峰峰值法用于真实世界的模拟信号,通常来自模拟传感器。本文所述的设计使用SLG46620VGreenPAK™计算0.5 Hz至200 Hz信号的低端频率,其波形宽度在100 - 1000 ms之间。通过对该应用的基本了解,可以设计其他模拟宽度和周期的峰峰值测量。

该电路包括峰峰值设计的所有部分。因此,IC负责接收模拟信号样本并将识别的峰值存储在内部缓冲器中。它还负责将两个峰值之间的测量时间段与内部阈值进行比较,以便在超过这些阈值时给出信号。

该设计由一个模拟信号输入和 4 个输出组成:

PD:在检测到峰值时发出脉冲。

高 PPM:如果信号频率超过上限阈值,则给出高。

低 PPM:如果信号频率超过下限阈值,则给出高。

正常:如果频率在两个阈值内,则给出 HIGH。

该 IC 的模数转换器 (ADC) 宏单元非常适合峰值信号检测。所选电路功耗低且性价比高。它是此应用程序中所需的小型设备。该 IC 可以替代分立 IC 和无源器件系统。

对一般电路的解释是期望它将被增强以适应特定的实际应用。设计结果利用GreenPAK Designer软件信号发生器来测试各种信号并显示相应的输出。信号以高于和低于IC中存储的值的频率生成,并显示每种情况的相应输出,以向读卡器确认操作正确。

可以在此处找到此应用程序的完整设计文件。

设计概述

检测过程使用ADC模块对模拟信号进行采样,然后将其存储在内部缓冲器中。然后接收模拟信号的新样本,并与存储的样本进行比较。

如果新样本的值大于当前存储的值,则模拟电压正在增加。新样本存储在缓冲器中,接收并比较信号的下一个样本。但是,如果接收到的样本等于缓冲区中存储的样本,则信号是恒定的。此时,它要么达到一个短暂的常数值但没有达到峰值,要么已经达到峰值,因此只有在信号开始下降时才考虑峰值状态。

如果下一个样本小于存储在ADC缓冲器中的前一个样本,则记录峰值状态。在另一个循环中重复该过程以找到下一个峰值。

为了计算频率,我们计算两个连续峰值之间的时间,并将该时间与预先存储在IC内部寄存器中的某些阈值进行比较。如果此时间大于较高的阈值,则频率小于允许的限制。如果此时间小于下限阈值,则频率大于允许的限制。

由于该设计适用于相对低频的信号,因此它们通常以每分钟的脉冲数计算,在此上下文中缩写为PPM。阈值标记为高 PPM 和低 PPM。

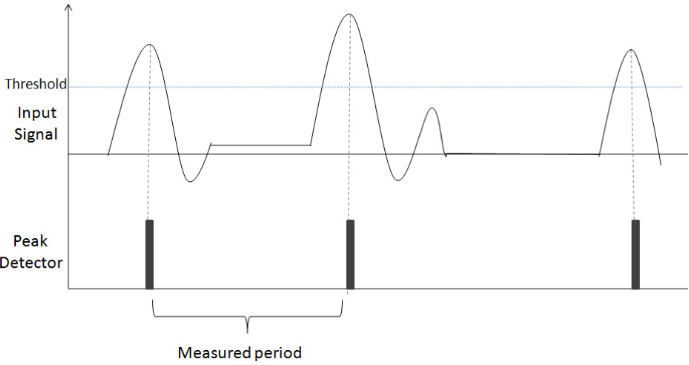

为了确保需要所有记录的峰值,将每个峰值与预先存储的电压阈值进行比较,以便仅在峰值幅度大于所选阈值时才考虑峰值,并忽略短幅度信号。图 1 显示了工作过程。

(图1:系统工作流程)

绿派设计

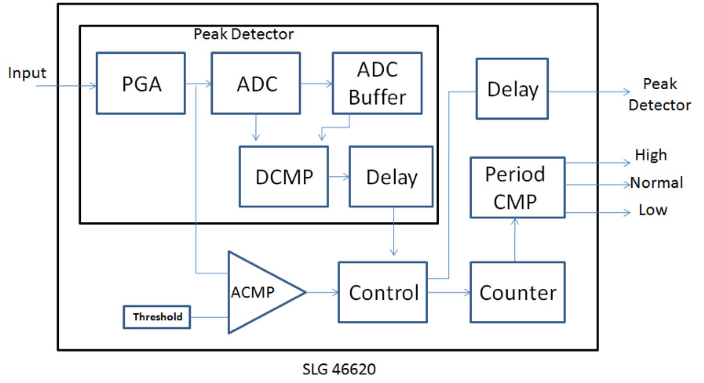

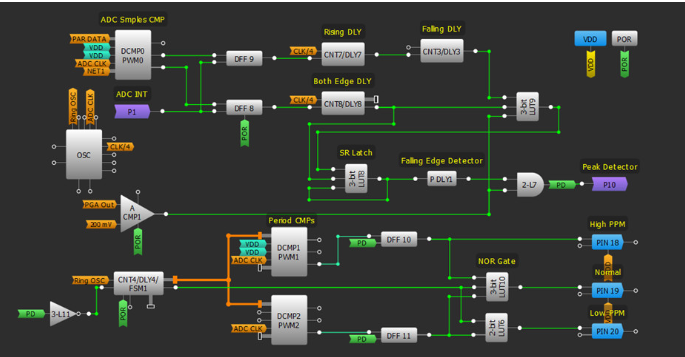

该设计由两部分组成:峰值检波器电路和频率监控电路,后者包含一个定时器和阈值比较器。图2显示了该设计的框图。

(图2:电路框图)

峰值检测器

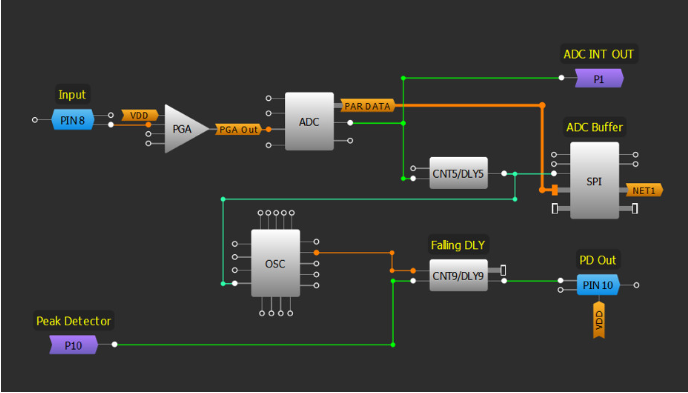

IC通过引脚8接收外部信号,该引脚配置为作为模拟输入/输出工作。然后,信号通过设置增益的可编程增益放大器(PGA)。ADC的工作模式为单端,并设置x1增益。然后,信号进入ADC模块。

在此设计中,输入信号为低频,因此通过将时钟周期除以16来降低采样速率。采样率相当于 97,6563 sps,以减少误差值和尖峰。

采样率 = PWM 和 ADC 时钟 / 256 = 25k / 16 / 256

为了指示峰值,必须给出一个信号来指示模拟输入是上升还是下降。为此,必须比较ADC输出的两个连续值。SLG46620V SPI模块配置为作为ADC缓冲器运行。

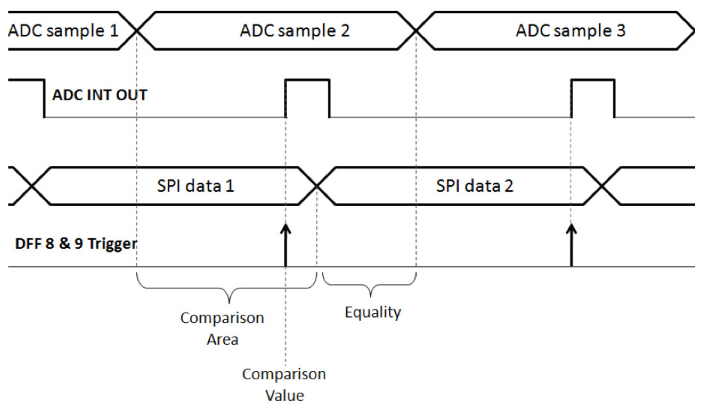

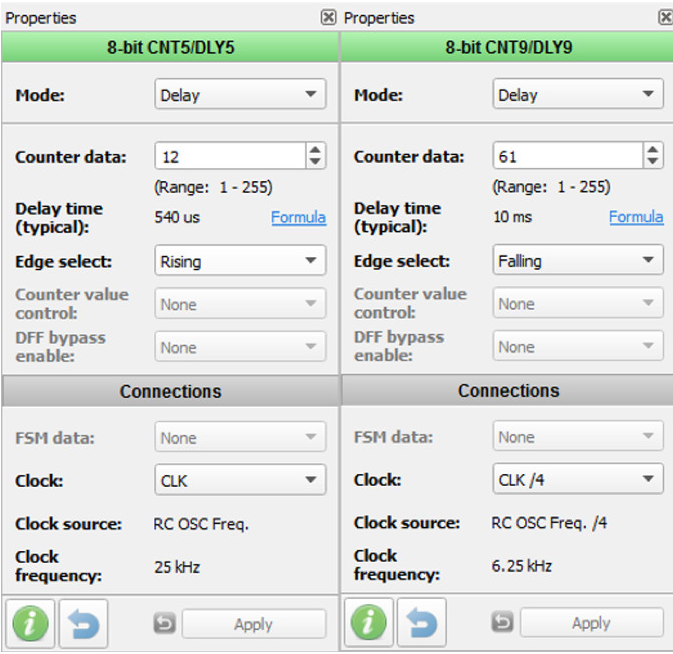

根据数据手册中的ADC属性,在ADC INT输出激活之前,PAR数据可以使用几个时钟周期。利用这一特性,ADC INT输出通过DLY5连接到SPI模块的SCLK输入,DLY5配置为作为上升沿延迟工作。因此,需要比较新的ADC值和具有ADC INT输出信号上升沿的旧ADC值。延迟后,DLY5输出触发SPI将新值存储在缓冲器中。工作时序图如图3所示。

(图3.ADC、SPI 和 DFF 时序图)

(图4.绿色PAK设计矩阵0)

通过DCMP0将ADC值与缓冲值进行比较,其中IN+输入从ADC [7:0]获取其值,IN-输入从SPI [7:0]获取其值。均衡器和OUT+输出分别连接到DFF8和DFF9。

如果 ADC 值大于 SPI 值,则 OUT+ = 1,EQ = 0。

如果ADC值小于SPI值,则OUT+ = 0,EQ = 0。

如果ADC值等于SPI值,则OUT+ = 0,EQ = 1。

EQ 和 OUT+ 输出与 ADC INT 输出信号的上升沿保持。为了确保每次比较时都不会记录相等状态,SPI将通过DLY5输出触发。因此,比较仅在两个连续值之间进行,如图 3 所示。

通过在系统运行期间监控EQ和OUT+输出的状态,会引入间歇脉冲,如果不考虑,会导致毛刺。为了防止这种情况并保持稳定的信号,CNT3、CNT7 和 CNT8 作为延迟运行以对系统进行去抖动。因此,可以防止尖峰对输出状态的影响。

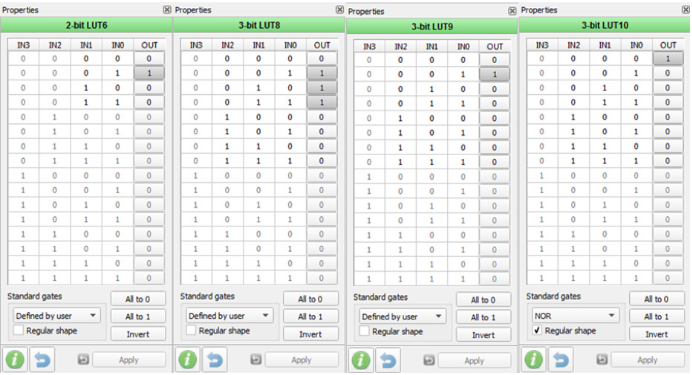

3 位 LUT8 用作 SR 锁存器,其中来自 OUT+ 输出的信号表示 Set,表示信号正在上升。复位来自3位LUT9,这意味着信号正在下降。

3L9配置为在OUT+ = 0、EQ = 0且ACMP1输出为高电平时发出高信号。

优先考虑上升状态,因为系统的目的是检测振幅的最高值。

一旦信号在上升状态后开始下降,3L8输出将从高电平变为低电平,并通过P DLY1检测下降沿。P DLY1输出指示峰值(PD)的检测。PD信号通过DLY9传递到Pin10,脉冲宽度增加,以适应任何外部设备的灵敏度。它还用于重置计数器。

ACMP1用于将PGA输出与固定阈值进行比较,在本设计中选择为200 mV。因此,如果峰值的幅度小于边际值,则将忽略该峰值。

(图5.绿色PAK设计矩阵1)

峰峰值频率监视器设计

构建峰值检波器设计后,我们将使用来自所述设计的PD信号来构建频率监视器。

FSM1用作计算两个峰值之间时间的计数器。由于预期信号是低频,FMS1的时钟源被选为LF OSC,除以16。因此,测量时间可以在 19 ms 到 2.35 s 之间,步长为 ~10 ms。通过使用低频振荡器,有源电流消耗被最小化。

DCMP1 和 DCMP2 将 FSM1 值与频率上限和下限阈值进行比较。DCMP1将FSM1值与(1:1)寄存器值进行比较,在本设计中设置为500 ms,表示下限阈值。DCMP2将FSM1值与寄存器2值进行比较,在本设计中设置为897 ms。

比较值与PD信号的上升沿一起存储在DFF10和DFF11中。Q输出极性已配置为DFF11反相。

FSM1 数据 < 寄存器0 值 ---> DCMP1 输出+ = 高 ---> DFF10 输出 = 高 ---> 高 PPM

FSM1 数据 > 寄存器2 值 ---> DCMP2 输出+ = 高 ---> DFF11 输出 = 高 ---> 低 PPM

寄存器0 < FSM1 数据 < 寄存器2 ---> 3L10 输出 = 高电平 --->正常

FSM1 通过 3L11 逆变器以 PD 信号的下降沿复位。如果周期超过 FSM1 工作范围 2.35 s,FSM1 输出向 3L10 和 2L6 提供高信号以关闭所有输出。这种情况表明测量的周期大于预期。此功能可用于指示输入中没有脉冲或特定应用处于危险的低周期。FSM的时钟源可以更改以适应要实现的应用。

(图6.LUT 属性)

(图7.CNT5 & CNT9 Properties)

结果

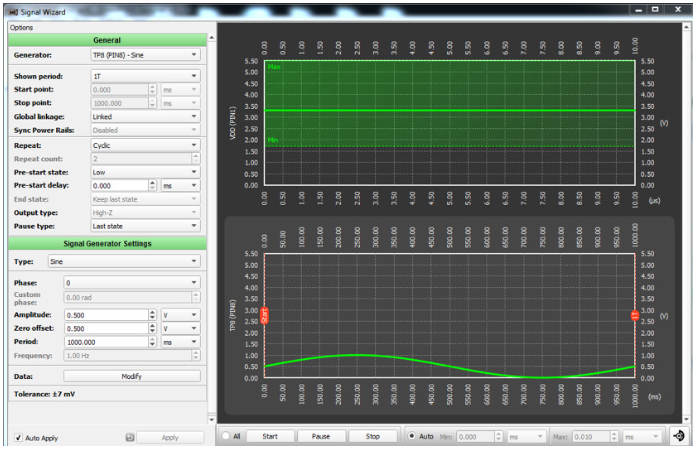

GreenPAK 设计器程序中包含的信号向导已用于检查设计并确保其按预期工作。

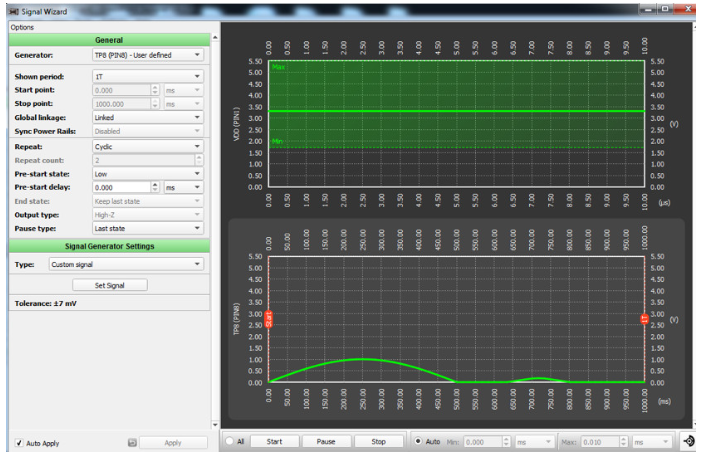

信号向导对于设计检查非常方便,无需使用外部信号发生器即可生成不同形状的信号。信号频率和幅度可以轻松控制。还可以生成自定义信号。

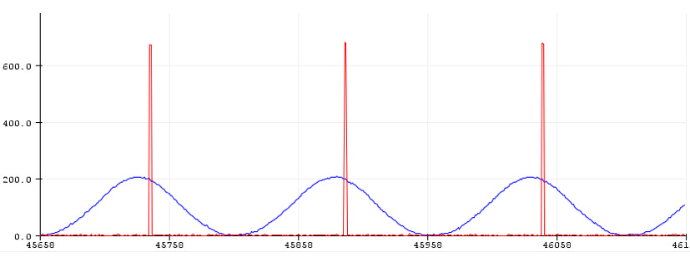

生成了几个信号。PD信号如下图所示。

(图8.CNT5 & CNT9 Properties)

(图9.蓝色信号为输入,红色信号为PD输出信号)

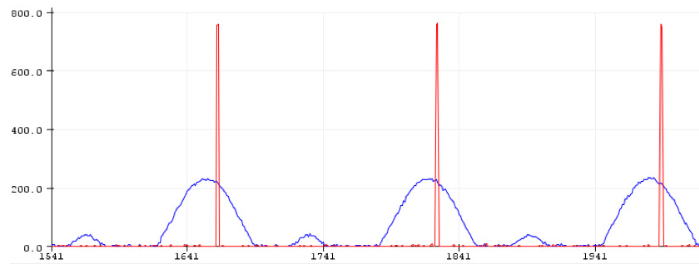

生成具有短不理想峰值的自定义信号。

(图10.生成自定义信号)

(图11.蓝色信号为输入,红色信号为PD输出信号)

对输入应用了不同的周期。相应的输出状态如表1所示。

表 1:不同周期的输出状态

本文概述了如何构建峰值检测电路,其中包括基于输入信号峰峰值时间计算的频率监控电路。该 IC 在集成多个功能方面表现出高效率,因为该项目需要这样的功能。此外,所选电路的低成本和小面积特别适用于本应用描述中针对的便携式和可穿戴解决方案。

审核编辑:郭婷

-

磁通计中峰值与峰峰值一篇看懂2025-09-18 1438

-

电源纹波是峰峰值吗,电源纹波越小越好吗?2024-02-25 12030

-

示波器怎么看峰峰值呢?2024-01-23 18282

-

信号峰峰值,周期和频率的原理公式2023-12-15 24428

-

市电220V说的是峰峰值还是有效值呢2022-09-07 22308

-

示波器峰峰值2019-12-14 5275

-

如何将RMS噪声转换成峰峰值噪声2019-06-12 9901

-

方波及峰峰值测量2018-10-04 2887

-

峰峰值定义_示波器峰峰值怎么看2017-11-22 201512

-

信号峰峰值测量2017-06-11 6892

-

峰峰值测量,模糊控制2014-12-22 4676

-

labview寻找峰峰值2014-04-25 14113

-

请问如何理解“峰峰值”?2013-09-27 5953

-

峰峰值杂音测量方法介绍2009-11-09 898

全部0条评论

快来发表一下你的评论吧 !