FPGA时钟系统的移植

可编程逻辑

描述

ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。因为后者有内建的时钟资源:锁相环、频率综合器、移相器,以及具有低延迟特性的专用时钟布线网络。ASIC芯片的时钟设计具有更大的灵活性,但FPGA芯片内建的时钟资源则能简化设计。正是因为两者的不同,带来了移植上的诸多麻烦。

ASIC设计中的时钟树结构,需要映射到FPGA芯片的专用时钟资源中,以及原型验证平台的不同FPGA芯片中。

一颗FPGA芯片的专用时钟资源是有限的,以Virtex-6LX760芯片也只有18个 MMCM时钟资源模块。这对于大部分FPGA设计来讲已经足够了,但是对于具有大量时钟树资源的ASIC设计来讲,往往还是不够使用。FPGA芯片的另外一个限制是同一个时钟域所能容纳的全局时钟资源有限。

门控时钟

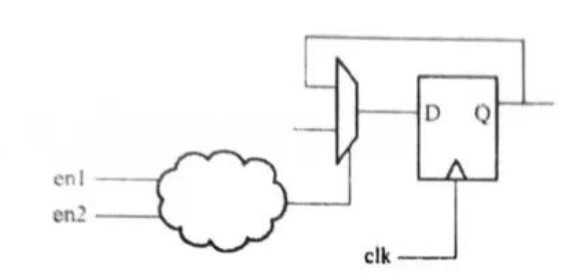

在ASIC设计中,常常采用门控时钟技术来降低整个芯片的低耗。图1显示了使用门控时钟技术的电路:时钟clk通过信号en1和en2进入组合逻辑后,驱动后续的两个寄存器。

从上述电路可以看出,当信号en1和en2的某种组合关系使得clk信号无法向后传递时,两个寄存器将停止工作,因此也不会消费功耗。

但是如果将ASIC设计中的门控时钟电路直接映射到FPGA芯片中,则会带来整体的性能甚至稳定性的下降。其根本原因在于FPGA芯片采用的是专用的低延迟时钟网络,只有整个时钟系统运行在该网络时,才能达到最高的性能。而通过组合逻辑的门控时钟信号运行在普通的布线资源上,这将大大的降低其性能,甚至带来建立保持时间的问题。因此必须将门控时钟通过某种方式映射到FPGA芯片的专用时钟资源上,而不是简单得代码移植。

门控时钟的转换

对门控时钟进行转换,就是要把时钟网络上的组合逻辑“删掉”,将所有时序逻辑的时钟驱动端口直接链接在FPGA芯片的专用时钟资源上。

其中一个方法就是将组合逻辑从时钟通路‘搬移’到数据通路上,这种方式可以通过图2中的多路选择器来实现。

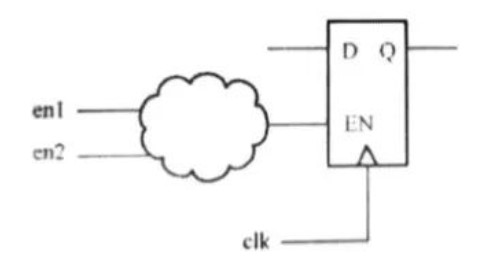

或者可以采用时钟使能的结构达到同样的功能,如图3所示。

设计工具对门控时钟的转换

Synopsys公司的Synplify Pro/Premier是高性能FPGA逻辑综合工具,可以自动地进行门控时钟转换。当然转换是有一定条件的:必须是带有组合逻辑的门控时钟结构;时钟必须要有确定的约束条件;门控时钟所驱动的时序逻辑电路不能是黑盒子。

前面提到的门控时钟转换电路都比较简单,在实际的设计中,门控时钟的组合逻辑也许会很复杂,所驱动的后续电路不仅仅有寄存器,还有 BRAM和DSP模块等时序逻辑。因此即便是Synplify pro/Premier这样的高性能综合器也可能有无法自动处理的电路结构,仍然需要手动修改。

时刻使能

对于ASIC设计中的时钟使能电路,没有必要做任何的转换工作。因此FPGA芯片内部的各种时序逻辑电路(包括寄存器、BRAM和DSP48模块)本身就带有时钟使能输入端口,因此综合工具可以做到完美的自动映射。

时钟管理单元的映射

ASIC设计中的大部分时钟管理模块(如PLL),仅仅需要对端口的细微修改就可以直接映射到FPGA对应的资源上。Xilinx的FPGA芯片提供了丰富的可配置时钟资源:DCM,PLL,MMCM,BUFG/BUFR,BUFGMUX,等等。

审核编辑:刘清

-

多平台FPGA工程快速移植与构建2024-11-20 2977

-

FPGA系统时钟问题2013-08-17 3412

-

采用FPGA的uClinux移植(IDE)pdf资料2010-02-08 561

-

大型设计中FPGA的多时钟设计策略2009-12-27 873

-

基于FPGA的时钟设计2011-09-21 4276

-

FPGA大型设计应用的多时钟设计策略2012-05-21 1681

-

如何正确使用FPGA的时钟资源2017-01-18 869

-

基于FPGA的高精度同步时钟系统设计2017-11-17 9058

-

时钟在FPGA设计中能起到什么作用2019-09-20 6179

-

FPGA知识汇集-ASIC向FPGA的移植2022-04-14 3132

-

如何移植FPGA的例程2022-09-05 2863

-

FPGA原型验证系统的时钟资源设计2023-04-07 1970

-

浅析FPGA原型验证系统的时钟资源2023-05-23 1579

-

FPGA的时钟电路结构原理2024-04-25 3608

-

FPGA如何消除时钟抖动2024-08-19 4281

全部0条评论

快来发表一下你的评论吧 !