RISC-V学习笔记【2】8051竟然是“复杂指令集CISC”?

嵌入式技术

描述

【1】8位、16位、32位、64位

除了 CISC与 RISC 之分,处理器指令集架构的位数也是一个重要的概念。通俗来讲处理器架构的位数是指通用寄存器的宽度,其决定了寻址范围的大小、数据运算能力的强弱譬如32位架构的处理器,其通用寄存器的宽度为 32位,能够寻址的范围为 232Byte,即4GB的寻址空间,运算指令可以操作的操作数为 32 位。

注意:处理器指令集架构的宽度和指令的编码长度无任何关系。并不是说 64 位架构的指令长度为 64位(这是一个常见的误区)。从理论上来讲,指令本身的编码长度越短越好因为可以节省代码的存储空间。因此即便在64 位的架构中,也大量存在16位编码的指

且基本上很少出现过 64 位长的指令编码。

综上所述,在不考虑任何实际成本和实现技术的前提下,理论上来讲:。通用寄存器的宽度,即指令集架构的位数越多越好,因为这样可以带来更大的寻址范围和更强的运算能力。

指令编码的长度越短越好,因为这样可以更加节省代码的存储空间常见的架构位数分为8位、16位、32位和64位。早期的单片机以8位和 16 位为主,知名的 8051 单片机是使用广泛的8位架构。

目前主流的嵌入式微处理器均在向 32 位架构转移。

目前主流的移动手持、个人计算机和服务器领域,均使用 64 位架构。

【2】CISC、RISC

常见的指令集架构大体上可以分为两大类:复杂指令集体系(CISC)和精简指令集体系(RISC)。

RISC全称Reduced Instruction Set Compute,精简指令集计算机。

CISC全称Complex Instruction Set Computers,复杂指令集计算机。

CISC既有简单指令也有复杂指令,后来人们发现典型程序中80%的语句都是使用计算机中20%的指令,而这20%的指令都属于简单指令;因此花再多时间去研究复杂指令,也仅仅只有20%的使用概率,并且复杂指令会影响计算机的执行速度。既然典型程序的80%都是使用简单指令完成,那剩下的20%语句用简单语句来重新组合一下模拟这些复杂指令就行了,而不需要使用这些复杂指令,于是RISC就出现了。

RISC的主要特点:

1)选取使用频率较高的一些简单指令以及一些很有用但不复杂的指令,让复杂指令的功能由使用频率高的简单指令的组合来实现。

2)指令长度固定,指令格式种类少,寻址方式种类少。

3)只有取数/存数指令访问存储器,其余指令的操作都在寄存器内完成。

4)CPU中有多个通用寄存器(比CICS的多)

5)采用流水线技术(RISC一定采用流水线),大部分指令在一个时钟周期内完成。采用超标量超流水线技术,可使每条指令的平均时间小于一个时钟周期。

6)控制器采用组合逻辑控制,不用微程序控制。

7)采用优化的编译程序

CICS的主要特点:

1)指令系统复杂庞大,指令数目一般多达200~300条。

2)指令长度不固定,指令格式种类多,寻址方式种类多。

3)可以访存的指令不受限制(RISC只有取数/存数指令访问存储器)

4)各种指令执行时间相差很大,大多数指令需多个时钟周期才能完成。

5)控制器大多数采用微程序控制。

6)难以用优化编译生成高效的目标代码程序

RISC与CICS的比较

1.RISC比CICS更能提高计算机运算速度;RISC寄存器多,就可以减少访存次数,指令数和寻址方式少,因此指令译码较快。

2.RISC比CISC更便于设计,可降低成本,提高可靠性。

3.RISC能有效支持高级语言程序。

4.CICS的指令系统比较丰富,有专用指令来完成特定的功能,因此处理特殊任务效率高。

复杂指令集最常见的例子是现在绝大多数家用计算机和网络服务器所使用的 AMD64 指令集(也叫 x86-64、x86_64、Intel 64、EM64T 等等,本文以发明人为基准称为 AMD64。)除此以外有一定使用量,和有历史意义的复杂指令集还有 IA-32、MC68000、MOS6502、Intel 8051、Intel 8080 等等。复杂指令集其复杂在于指令种类数量巨大,非常多次常用到不常用的功能都会被整合进处理器指令集中。同时复杂指令集系统每条指令的操作数寻址方式复杂,几乎所有指令都可以直接访问内存;相应的指令的机器码编码方式复杂,普遍使用不定长指令等。同时,复杂指令集系统一般没有独立的专用内存访问指令,处理器内所设置的通用寄存器数量也偏少。(例如 IA-32 没有严格意义上的通用整数寄存器,到了 AMD64 也才勉强设置了八个通用整数寄存器。)

精简指令集最常见的例子则是常见于智能设备和嵌入式平台的 ARM 指令集家族。除此以外除此以外有一定使用量,和有历史意义的精简指令集还有龙芯 LoongArch、MIPS、RISC-V、PowerPC、AVR 等等。精简指令集其精简在于指保留最基本最必要的指令,将复杂功能完全交给上层的软件算法和下层的专用外设去解决。同时精简指令集系统指令寻址方式往往非常单一,除了专门的访存指令以外所有指令都只能在寄存器范围内操作,相应的精简指令集系统普遍使用固定长度指令,也会配备相对比较多的通用寄存器。(例如上个世纪的 ARMv4T、MIPS32 就都已经有 29~31 个通用寄存器了,相比于同时期 IA-32 的 0 个。)

实际到了应用层面上,对于高级语言程序来说,对于处理器设计来说,两种指令集架构分类的实际差异已经不大了。Intel 和 AMD 的 AMD64 实现都使用了微代码,而从复杂指令翻译出来的微代码普遍都用了类 RISC 设计。本世纪初的时候还普遍认为复杂指令集处理器速度更快,到了现在精简指令集已经很强大了,完全比CISC更快。有些CISC最终也是转化为RISC进行执行了。

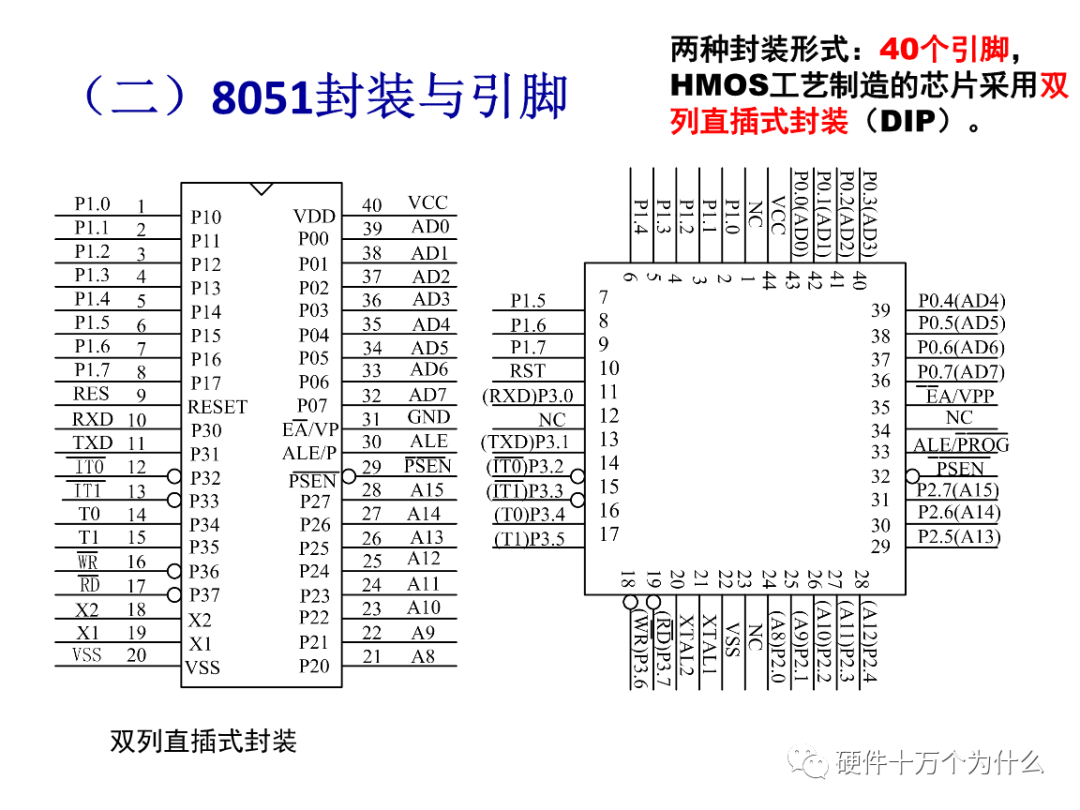

【3】8位的CISC——8051

8位和CISC两个似乎是矛盾的,但是8051活生生的辉煌了40年。

说起 8051 内核,几乎无人不知无人不晓。8051 作为一款生了数十年之久的微处理器内核,在8位入式微处理器内核领域,它是当之无愧的传“前辈”

自从Inlel于1980年为入式系统开发Intel MCS-51(通常简称 8051)单芯片微控制(单片机)至今,8051 内核架构已经走过将近 40个年头。Intel 还以专利转让的形式8051内核转让给了许多其他半导体公司,这些公司进一步发展出不同型号基于 8051内核微控制器芯片,因此形成了一个庞大的 8051 家族。

几十年发展下来的庞大的用户群和生态环境,以及多年来众多备受肯定的成功产品,可以说 8051内核几乎成为8 位微处理器内核的业界标杆。8051 内核架构在 1998 年失去专利保护,久经沙场的它再次进发出强大的二次生命力,各种形式的 8051 架构 MCU(微控制器Microcontroller Unit)进一步涌入市场,各种基于 8051内核的芯片产品层出不穷,各种免费版本的 8051 内核IP 也可以从各种渠道获取。

当然由于 8051 内核并没有一个统一的组织和标准进行管理,所以也存在着体系结构浪乱,各种增强型复杂多样的问题。虽然时常也都自称为 8051 内核,但是其实各有差别,琅满目让人难以分辨。但是这丝毫不影响 8051 内核的经典地位,时至今日,虽然目前微处理器内核正在经历着向32位架构迁移的大趋势,但是 8051内核仍然有着举足轻重的地位在大量的MCU、数模混合信号芯片、SoC 芯片中仍能看到 8051 内核的身影,并且在相当长的时间内,在适合8位架构处理器内核的应用领域中都将继续使用 8051 内核,可以说是“廉颇虽老,尚能饭也”。

8051 内核能在嵌入式领域取得如此成功的地位,可以归功于如下几个方面的原因。

广泛的被认知度,简单的体系结构。

没有知识产权的限制,商业和开源的版本众多,非常适合中小型芯片公司采用。

用庞大的用户群以及相应的生态系统。

成熟且免费的软件工具链支持。

——你似乎感受到RISC-V从其一诞生就符合以上几条的气质。

尽管如此,8051作为一款诞生了接近 40 年的8位CISC(复杂指令集)架构内核,虽然是“老骥伏析,壮心不已”,但是由于其性能低下,寻址范围受限,已经难以适应更多的新兴应用领域。随着IoT的发展和崛起,虽然嵌入式领域对于处理器内核的需求更加井喷,但是更多的是开始采用 32 位架构,且很多传统的 8 位应用领域也在开始向着32位架构迁移。这样ARM的Cortex-M系列有了成长的机会。

然而在20世纪80年代该单片机刚刚问世时,半导体的制造工艺还只能达到um 级,处理器所能达到的时钟频率偏低。而且当时硬件设计语言还处于起步阶段也缺乏自动设计的工具,软件多以手工汇编编程为主。这就导致流水线设计的优势无法得到发挥,并且每条指令需要多个时钟周期才能完成。由于上述原因,当时的指令集设计往往具有以下特点:

(1)尽量在每条指令中实现更多的功能。例如 8051的CJNE 指令,就需要在一条指令中依次实现:

①与累加器做减法

②修改进位标示

③将结果做相等比较

④根据比较结果决定是否跳转

(2)指令集庞大,以实现更多的复杂功能。例如 8051 虽然是 8 位单片机其指令集却包含高达 255 种不同的指令和格式

(3)由于以上两点,导致变长指令的出现,以提高内存利用率。8051的指令就有单字节、双字节与三字节三种不同的种类,而且除了对指令解码以外,没有其他的手段帮助判定指令长度。

(4)寻址方式众多。例如在 8051 指令集中,对数值的操作包括如下方式

①立即数寻址。将常数包含在指令中。

② 直接寻址。将内存地址包含在指令中。

③间接寻址。将内存地址放入寄存器中,然后将寄存器地址包含在指令中.

④寄存器寻址。将操作数放入寄存器中,然后将寄存器地址包含在指令中

【4】8051具备CISC的所有缺点

1)尽量在每条指今中实现更多的功能

为了在实现这些复杂功能的同时保持高吞吐率,流水线的设计者不得不花更多的时间规划流水线的各级。即便如此,有些指令依然无法实现单周期吞吐,例如上文提到的CJNE 指令,就需要两个时钟周期。

另外,现代的8051 处理器开发,早已经采用C语言代替了早期的汇编语言而高级语言的编译器往往很难把这类复杂、多功能机器指令的威力全部发挥出来有违当初指令集的设计初衷。

当然,指令集复杂这个特点也并非一无是处。由于 CISC 指令集的指令复杂也使得其代码密度(Code Density)一般要优于同等字宽的RISC处理器

2)庞大的指令集浪费逻辑资源

庞大的指令集必然导致指令的解码阶段变得更为复杂,需要耗费更多的逻辑资源。指令集被分为两部分对它们各自的解码分别占用了流水线的一级。这样设计的原因之一就是为了在庞大指令集下实现高吞吐率、高时钟频率,而不得不做出的妥协。同样时钟频率的RISC-V处理器,由于指今集比较精简,就无须做这样的妥协,从而大大节省了逻辑资源,简化了流水线设计。

3)变长指令的出现,以提高内存利用率

8051的指令有单字节、双字节和三字节三种不同的种类,除解码(Decode)外没有其他的手段帮助判定指令长度。这种变长的指令结构,导致指令之间的边界很难判定,甚至有可能导致内存的非对齐读取(Unaligned Memory Access),从而对流水线的取指器(Instruction Fetch)设计带来挑战。

8051的内存架构是哈佛架构,其代码与数据在不同的地址空间中分开存放。这就使得代码存储部分可以单独做一些优化设计。

由于8051指令集没有其他辅助手段来帮助判定指令长度,为了确定指令的边界,8051的取指器不得不为此花费比 RISC-V 更多的逻辑资源

4)众多的寻址方式

由于8051存在众多的寻址方式,使得指令集中的许多指令都可以访间内存这导致流水线的数据冲突(Data Hazard)很难判断,有时不得不通过硬件自动插入空操作(Null Operation,NOP)来保持数据的正确和完整。这样既消耗了逻辑资源,又降低了流水线的效率,从而对功耗和性能造成双重打击。

审核编辑:汤梓红

-

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集2024-01-31 857

-

RISC-V基础整数指令集2024-07-27 1011

-

CISC(复杂指令集)与RISC(精简指令集)的区别2024-07-30 313

-

RISC-V指令集的特点总结2024-08-30 1193

-

RISC-V和arm指令集的对比分析2024-09-28 1707

-

RISC-V的指令集位宽的几点学习心得2024-10-31 1829

-

什么是RISC-V?以及RISC-V和ARM、X86的区别2024-11-16 1518

-

RISC-V指令集概述2024-11-30 1137

-

ARM的指令集文章集合2020-09-07 1978

-

cisc&risccisc(复杂指令集)有哪些特点呢2021-12-17 1414

-

精简指令集架构RISC与复杂指令集架构CISC有何区别2021-12-23 2952

-

计算机两种花指令集CISC和RISC的区别2022-03-30 9638

-

简单讲讲RISC-V指令集CPU的参数2022-08-07 5012

-

全面解析:RISC-V异构IoT架构2023-03-21 2134

-

芯经验—指令集、ARM、FPGA、DSP、RISC-V介绍2022-03-31 5608

全部0条评论

快来发表一下你的评论吧 !