PCB板Trace走线较长测试阻抗出现末端上飘的现象

PCB设计

2578人已加入

描述

经常测试阻抗的朋友应该知道,当PCB板Trace走线较长时,测试阻抗结

果会出现末端上飘现象。

原因: 较长走线的DC电阻叠加在阻抗曲线上,看上去曲线后段阻抗偏高,其实并不是走线的真实阻抗。

为了更清楚判断常规上飘的大致位置,做了以下几个实验:

验证如下:

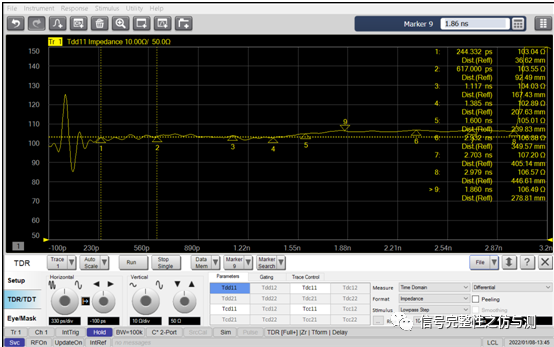

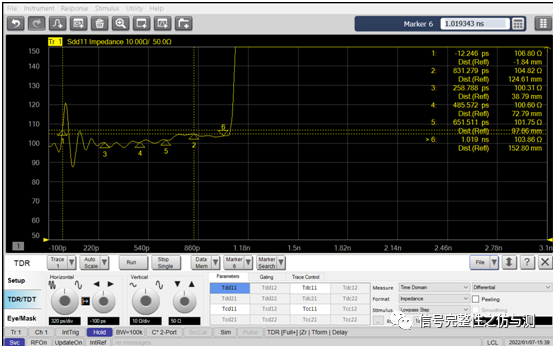

1. 10inch****表层走线

从走线左右端测试点分别测试,Mark9 1.86ns处均开始明显上飘。图1的Mark6对应图2的Mark2,对应不上,说明此处已经上飘。图1的Mark9对应图2的Mark3,反过来亦成立。Mark4和Mark5也成立。说明Mark9是上飘临界点成立。

换算后为约为6inch长度。

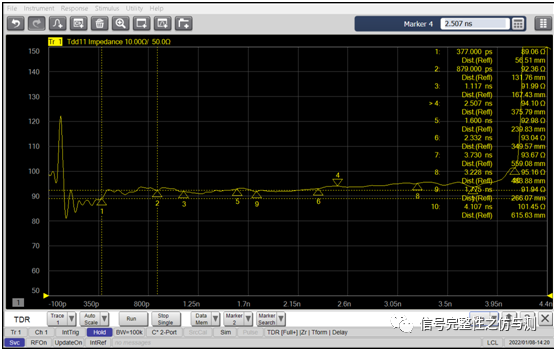

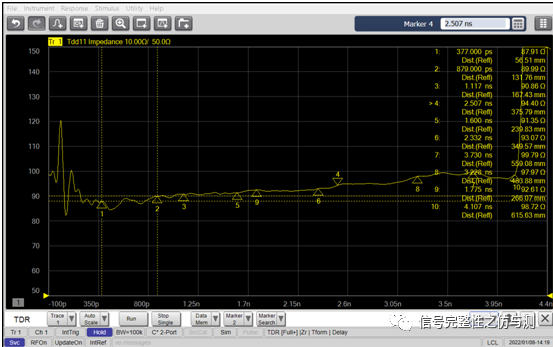

2.13inch****内层走线

同样从左右两端测试,均是Mark6 2.332ns处明显上飘。图1的Mark4与图2的Mark5对应不上,说明此处已经上飘。图1的Mark6对应图2的Mark9,反之亦成立。说明Mark6是上飘临界点成立。

换算后为约为7inch长度。

解决方案:阻抗测试时读数不要读取上飘后的数据,如果需要确认是否是上飘可以从左右两端分别测试,看看阻抗曲线前半部分,验证一下上飘是否是真实的。

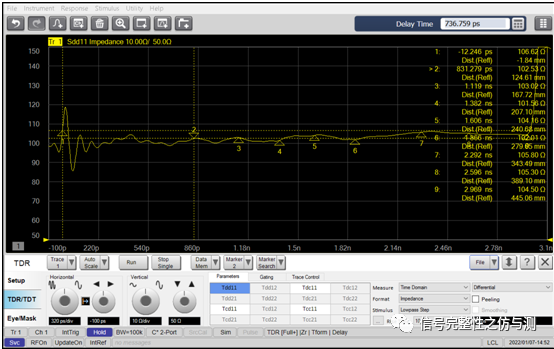

3.全长曲线和切除上飘后的曲线,可以看到上飘不影响前端走线阻抗值。

4.全长曲线、切除上飘后左端测试、切除上飘后右端测试。有时候上飘的位置阻抗确实就是没做好,是真的高。

左端测试

右端测试

当然,这个上飘位置不是绝对的,还跟你用的板材,线宽、铜厚、线长等因素都有关系。只能说给自己留有个判断的依据而已。

其实测的多了,波形上几乎也就看出来了。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- PCB板

-

PCB走线镀锡2011-10-31 2348

-

为什么PCB走线中避免出现锐角和直角?2017-08-12 12279

-

PCB板阻抗板的定义2018-09-18 2474

-

PCB差分走线的阻抗控制技术(二)2019-05-29 2615

-

PCB设计走线的阻抗控制简介2023-04-12 1381

-

PCB板蛇形走线的作用2009-11-27 1173

-

PCB板蛇形走线作用及绘制2011-06-10 2931

-

PCB阻抗测试,是怎么测出来的2011-11-09 20239

-

如何控制PCB走线的阻抗2019-10-04 11693

-

什么是PCB线路板走线阻抗2020-09-21 13992

-

PCB板上多长的走线才是传输线?2020-11-06 6874

-

PCB板蛇形走线有哪些好处2020-11-25 2311

-

TDR阻抗测试上飘问题分析2023-09-07 4281

-

pcb阻抗测试方法有哪些 影响PCB阻抗的六大因素2024-03-20 6117

-

pcb走线厚度:打造更稳定、精准的PCB设计2024-04-15 2232

全部0条评论

快来发表一下你的评论吧 !