利用设计网关的 IP 内核在 Xilinx VCK190 评估套件上加速人工智能应用

电子说

描述

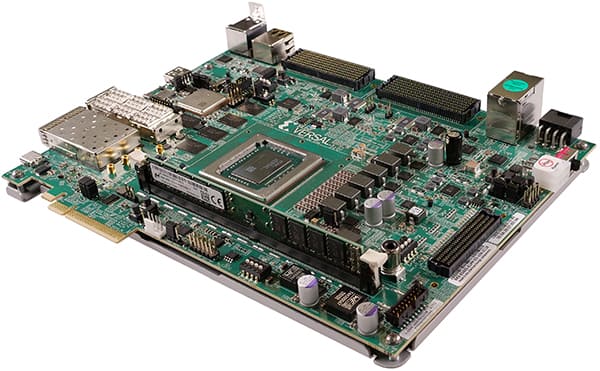

Xilinx 的 Versal AI Core 系列器件旨在解决独特且最困难的 AI 推理问题,方法是使用高计算效率 ASIC 级 AI 计算引擎和灵活的可编程结构来构建具有加速器的 AI 应用,从而最大限度地提高任何给定工作负载的效率,同时提供低功耗和低延迟。

Versal AI Core 系列VCK190 评估套件采用VC1902器件,该器件在产品组合中具有最佳的 AI 性能。该套件专为需要高吞吐量 AI 推理和信号处理计算性能的设计而设计。VCK190 套件的计算能力是当前服务器级 CPU 的 100 倍,并具有多种连接选项,是从云到边缘的各种应用的理想评估和原型设计平台。

图 1:赛灵思 Versal AI 内核系列 VCK190 评估套件。(图片来源:AMD, Inc)

图 1:赛灵思 Versal AI 内核系列 VCK190 评估套件。(图片来源:AMD, Inc)

VCK190 评估套件的主要特性

- 板载 Versal AI 核心系列设备

- 配备 Versal ACAP XCVC1902 量产芯片

- AI 和 DSP 引擎的计算性能比当今的服务器级 CPU 高 100 倍

- 用于快速原型设计的预构建合作伙伴参考设计

- 用于前沿应用开发的最新连接技术

- 内置 PCIe 第 4 代硬 IP,用于高性能设备接口,如 NVMe® 固态盘和主机处理器

- 内置 100G EMAC 硬 IP,用于高速 100G 网络接口

- DDR4 和 LPDDR4 内存接口

- 协同优化工具和调试方法

- Vivado® ML, Vitis 统一软件平台, Vitis™ AI, 用于 AI 推理应用开发的 AI 引擎工具

利用赛灵思 Versal AI 内核系列器件实现 AI 接口加速

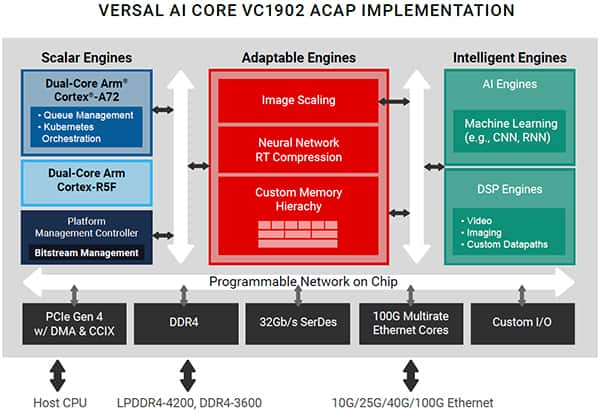

图 2:赛灵思 Versal AI 内核 VC1902 ACAP 器件框图。(图片来源:AMD, Inc)

Versal® AI Core 自适应计算加速平台 (ACAP) 是一款高度集成的多核异构设备,可在硬件和软件级别动态适应各种 AI 工作负载,使其成为 AI 边缘计算应用或云加速器卡的理想选择。该平台集成了用于嵌入式计算的下一代标量引擎、用于硬件灵活性的自适应引擎,以及由 DSP 引擎和用于推理和信号处理的革命性 AI 引擎组成的智能引擎。其结果是一个适应性强的加速器,其性能、延迟和能效超过了传统 FPGA 和 GPU 的性能、延迟和能效,适用于 AI/ML 工作负载。

Versal ACAP 平台亮点

- 适应性强的引擎:

- 自定义内存层次结构优化了加速器内核的数据移动和管理

- 预处理和后处理功能,包括神经网络 RT 压缩和图像缩放

- 人工智能引擎 (DPU)

- 矢量处理器的平铺阵列,使用 XCVC1902 设备(称为深度学习处理单元或 DPU)时,性能高达 133 INT8 TOPS

- 非常适合神经网络,包括CNN,RNN和MLP;硬件可适应不断演变的算法进行优化

- 标量引擎

- 四核ARM处理子系统,用于安全、电源和比特流管理的平台管理控制器

VCK190 人工智能推理性能

与当前服务器级 CPU 相比,VCK190 能够提供超过 100 倍的计算性能。下面是基于 C32B6 DPU 内核的 AI 引擎实现的性能示例,批处理 = 6。有关 VCK190 上各种神经网络样本的吞吐量性能(以帧/秒或 fps 为单位),DPU 以 1250 MHz 运行,请参阅下表。

| no | 神经网络 | 输入大小 | 共和党 | 性能(帧率)(多线程) |

|---|---|---|---|---|

| 1 | face_landmark | 96x72 | 0.14 | 24605.3 |

| 2 | facerec_resnet20 | 112×96 | 3.5 | 5695.3 |

| 3 | inception_v2 | 224×224 | 4 | 1845.8 |

| 4 | medical_seg_cell_tf2 | 128×128 | 5.3 | 3036.3 |

| 5 | MLPerf_resnet50_v1.5_tf | 224×224 | 8.19 | 2744.2 |

| 6 | 精炼Medical_EDD_tf | 320x320 | 9.8 | 1283.6 |

| 7 | tiny_yolov3_vmss | 416×416 | 5.46 | 1424.4 |

| 8 | yolov2_voc_pruned_0_77 | 448×448 | 7.8 | 1366.0 |

表 1:VCK190 AI 推理性能示例。

有关 VCK190 AI 性能的更多详细信息,请参阅 Vitis AI 库用户指南 (UG1354), r2.5.0 athttps://docs.xilinx.com/r/en-US/ug1354-xilinx-ai-sdk/VCK190-Evaluation-Board

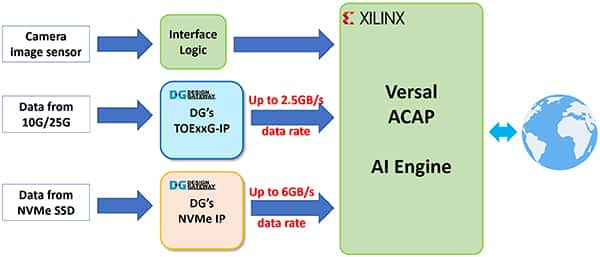

设计网关的 IP 核如何提高 AI 应用程序性能?

设计网关的IP 核设计用于处理网络和数据存储协议,无需 CPU 干预。这使得将CPU系统从复杂的协议处理中完全卸载成为理想的选择,并使它们能够将大部分计算能力用于AI应用程序,包括AI推理,前后数据处理,用户界面,网络通信和数据存储访问,以获得最佳性能。

图 3:具有设计网关 IP 核的示例 AI 应用程序的框图。(图片来源:设计网关)

图 3:具有设计网关 IP 核的示例 AI 应用程序的框图。(图片来源:设计网关)

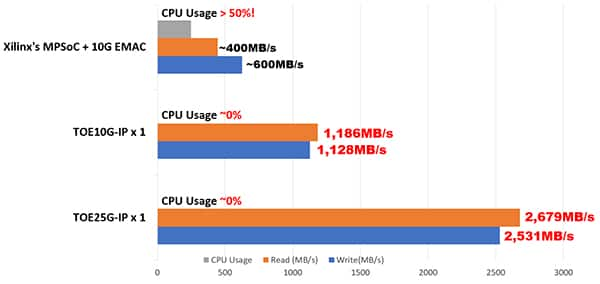

设计网关的 TCP 卸载引擎 IP (TOExxG-IP) 性能

传统 CPU 系统处理超过 10GbE 或 25GbE 的高速、高吞吐量 TCP 数据流需要超过 50% 的 CPU 时间,这会降低 AI 应用程序的整体性能。根据赛灵思MPSoC Linux系统上的10G TCP性能测试,10GbE TCP传输过程中的CPU使用率超过50%,TCP发送和接收数据传输速度可以达到10GbE速度的40%至60%左右或400 MB / s至600 MB / s。

通过实施设计网关的TOExxG-IP 内核,通过 10GbE 和 25GbE 传输的 CPU 使用率可以降低到几乎 0%,同时以太网带宽利用率可以达到接近 100%。这允许通过纯硬件逻辑直接通过 TCP 网络发送和接收数据,并以最小的 CPU 使用率和尽可能低的延迟馈送到 Versal AI 引擎。下面的图 4 显示了 TOExxG-IP 和 MPSoC Linux 系统之间的 CPU 使用率和 TCP 传输速度比较。

图 4:MPSoC Linux 系统和 Design Gateway 的 TOExxG-IP 内核对 10G/25G TCP 传输的性能比较。(图片来源:设计网关)

图 4:MPSoC Linux 系统和 Design Gateway 的 TOExxG-IP 内核对 10G/25G TCP 传输的性能比较。(图片来源:设计网关)

设计网关的 TOExxG-IP for Versal 设备

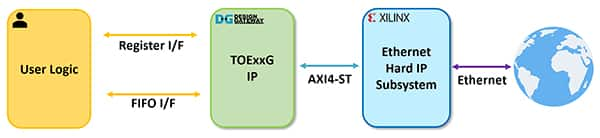

图 5:TOExxG-IP 系统概述。(图片来源:设计网关)

图 5:TOExxG-IP 系统概述。(图片来源:设计网关)

TOExxG-IP 内核实现了 TCP/IP 堆栈(硬线逻辑),并与赛灵思的 EMAC 硬 IP 和以太网子系统模块连接,以实现 10G/25G/100G 以太网速度的下层硬件接口。TOExxG-IP 的用户界面由用于控制信号的寄存器接口和用于数据信号的 FIFO 接口组成。TOExxG-IP 设计用于通过 AXI4-ST 接口与赛灵思以太网子系统连接。用户界面的时钟频率取决于以太网接口速度(例如,156.625 MHz 或 322.266 MHz)。

TOExxG-IP的特点

- 完整的 TCP/IP 堆栈实现,无需 CPU

- 支持一个会话与一个 TOExxG-IP

- 可以使用多个 TOExxG-IP 实例实现多会话

- 支持服务器和客户端模式(被动/主动打开和关闭)

- 支持巨型帧

- 通过标准先进先出接口实现简单的数据接口

- 通过单端口 RAM 接口实现简单的控制接口

XCVC1902-VSVA2197-2MP-ES FPGA 器件上的 FPGA 资源使用情况如下表 2 所示。

| 家庭 | 示例设备 | 最大频率 (兆赫 | 负载均衡注册 | 负载均衡 LUT | 片 | IOB | 布拉姆蒂勒^1^ | 乌兰 | 设计工具 |

|---|---|---|---|---|---|---|---|---|---|

| Versal AI Core | XCVC1902-VSVA2197-2MP-ES | 350 | 11340 | 10921 | 2165 | - | 51.5 | - | 万岁2021.2 |

表 2:Versal 设备的实现统计信息示例。

TOExxG-IP 的更多详细信息在其数据表中进行了描述,可通过以下链接从设计网关的网站下载:

Design Gateway's NVMe Host Controller IP performance

NVMe Storage interface speed with PCIe Gen3 x4 or PCIe Gen4 x4 has data rates up to 32 Gbps and 64 Gbps. This is three to six times higher than 10GbE Ethernet speed. Processing complicated NVMe storage protocol by the CPU to achieve the highest possible disk access speed requires more CPU time than TCP protocol over 10GbE.

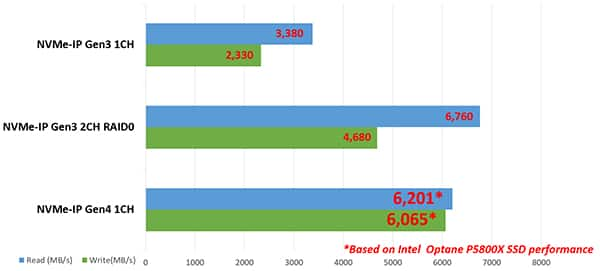

Design Gateway solved this problem by developing the NVMe IP core that is able to run as a standalone NVMe host controller, able to communicate with an NVMe SSD directly without the CPU. This enables a high efficiency and performance of the NVMe PCIe Gen3 and Gen4 SSD access, which simplifies the user interface and standard features for ease of usage without needing knowledge of the NVMe protocol. NVMe PCIe Gen4 SSD performance can achieve up to a 6 GB/s transfer speed with NVMe IP as shown in Figure 6.

Figure 6: Performance comparison of NVMe PCIe Gen3 and Gen4 SSD with Design Gateway's NVMe-IP Core. (Image source: Design Gateway)

Figure 6: Performance comparison of NVMe PCIe Gen3 and Gen4 SSD with Design Gateway's NVMe-IP Core. (Image source: Design Gateway)

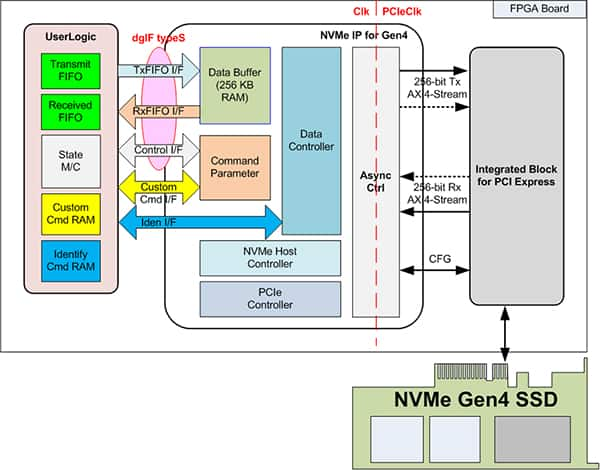

Design Gateway's NVMe-IP’s for Versal devices

Figure 7: NVMe-IP systems overview. (Image source: Design Gateway)

Figure 7: NVMe-IP systems overview. (Image source: Design Gateway)

NVMe-IP’s features

- Able to implement application layer, transaction layer, data link layer, and some parts of the physical layer to access the NVMe SSD without a CPU or external DDR memory

- Operates with Xilinx PCIe Gen3 and Gen4 Hard IP

- 能够利用BRAM和URAM作为数据缓冲区,而无需外部存储器接口

- 支持六个命令:识别、关机、写入、读取、SMART 和刷新(提供可选的附加命令支持)

XCVC1902-VSVA2197-2MP-E-S FPGA 器件上的 FPGA 资源使用情况如表 2 所示。

| 家庭 | 示例设备 | 最大频率 (兆赫) | 负载均衡注册 | 负载均衡 LUT | 片 | IOB | 布拉姆蒂勒^1^ | 乌兰 | 设计工具 |

|---|---|---|---|---|---|---|---|---|---|

| Versal AI Core | XCVC1902-VSVA2197-2MP-ES | 375 | 6280 | 3948 | 1050 | - | 4 | 8 | 万岁2022.1 |

表 3:Versal 设备的实现统计信息示例。

有关 Versal 器件的 NVMe-IP 的更多详细信息,请参见其数据表,可通过以下链接从 Design Gateway 的网站下载:

结论

TOExxG-IP 和 NVMe-IP 内核都可以通过将 CPU 系统从计算和内存密集型协议(如 TCP 和 NVMe 存储协议)中完全卸载来帮助加速 AI 应用程序性能,这对于实时 AI 应用程序至关重要。这使得赛灵思的 Versal AI Core 系列器件能够执行 AI 推理和高性能计算应用,而不会出现网络和数据存储协议处理的瓶颈或延迟。

VCK190 评估套件和 Design Gateway 的网络和存储 IP 解决方案可在 Xilinx 的 Versal AI Core 器件上以尽可能低的 FPGA 资源使用量和极高的能效在 AI 应用中实现最佳性能。

- 相关推荐

- 热点推荐

- 测试

-

FPGA在人工智能中的应用有哪些?2024-07-29 8247

-

VCK190评估板用户指南2023-09-13 430

-

如何将人工智能应用到效能评估系统软件中去解决2023-08-30 784

-

在Versal VCK190评估套件上使用器件固件升级(DFU)执行USB辅助启动模式测试2023-07-10 1862

-

利用Design Gateway的IP Core加速Xilinx VCK190评估套件上的AI应用2023-07-07 2712

-

【产品测试】利用设计网关的 IP 内核在 Xilinx VCK190 评估套件上加速人工智能应用2022-11-29 3793

-

利用设计网关的 IP 内核在 Xilinx VCK190 评估套件上加速人工智能应用2022-11-25 2982

-

如何更改VCK190单板启动模式2022-08-26 2159

-

在VCK190板子上使用DDR4-DIMM的ECC2022-08-17 2222

-

嵌入式人工智能简介2021-10-28 1910

-

赛灵思宣布两款Versal ACAP评估套件现已上市2021-03-12 4105

-

赛灵思Versal评估套件助力开发者迈入解锁ACAP功能的高速路2021-01-14 3050

-

人工智能是什么?2015-09-16 6401

全部0条评论

快来发表一下你的评论吧 !