多电源IC的上电时序控制你搞明白了么?

描述

人们常常想当然地为PCB的电路上电,殊不知这可能造成破坏以及有损或无损闩锁状况。这些问题可能并不突出,直到量产开始,器件和设计的容差接受检验时才被发现,但为时已晚,项目和产品的时间及交货将会受到极大影响,成本大幅攀升。为了解决这一阶段中发现的错误,将需要进行大量修改,包括PCB布局变更、设计更改和额外的异常现象等。

本应用笔记讨论设计工程师在新设计中必须考虑的某些更微妙的电源问题,特别是当IC需要多个不同的电源时。目前,一些较常用的电源电压是:+1.8V、+2.0V、+2.5V、+3.3V、+5V、−5V、+12V和−12V。

同样,数字输入电压范围为−0.3V至DVDD +0.3V。这说明,数字输入必须小于DVDD +0.3V。因此,在上电时,DVDD必须先于微处理器/逻辑接口电路或与之同时上电。与上述模拟内核情况相似,这些引脚上的ESD二极管也可能变为正偏,使数字内核上电到未知状态。

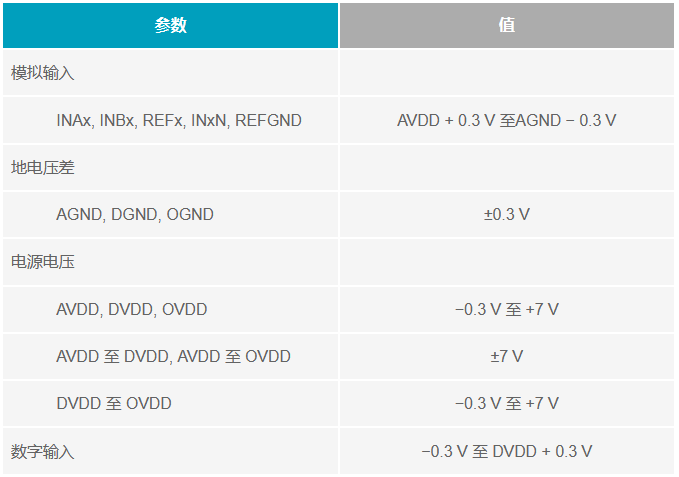

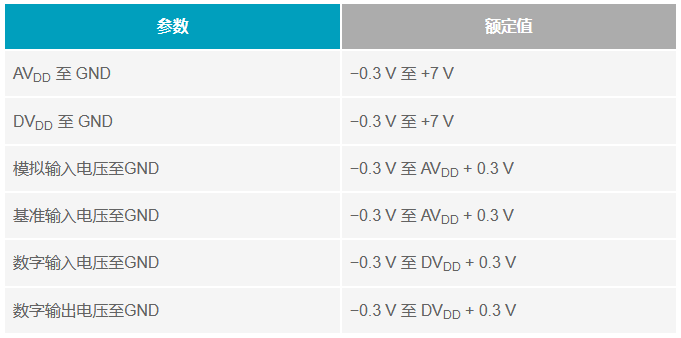

AD7621、AD7622、AD7623、AD7641和AD7643等PulSAR ADC速度更快,是该系列的新型器件,采用更低的2.5V电源(AD7654则采用5V电源)。AD7621和AD7623具有明确规定的上电序列。表2摘自AD7621 (Rev.0)数据手册的“绝对最大额定值”部分。

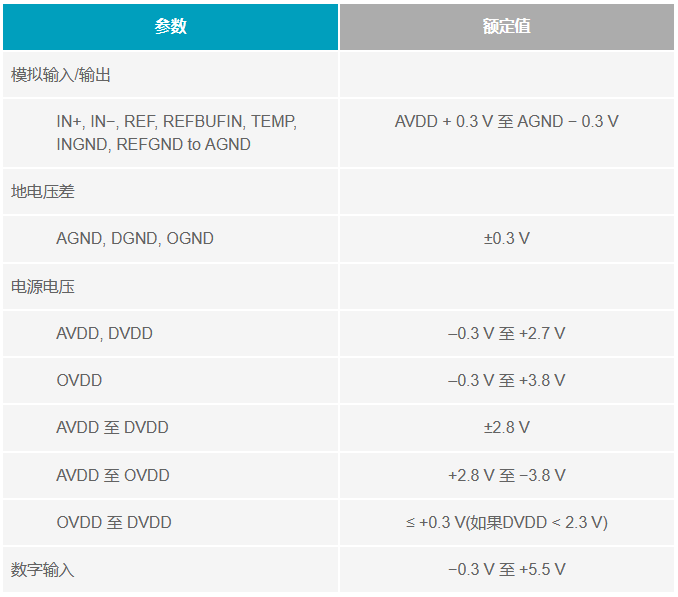

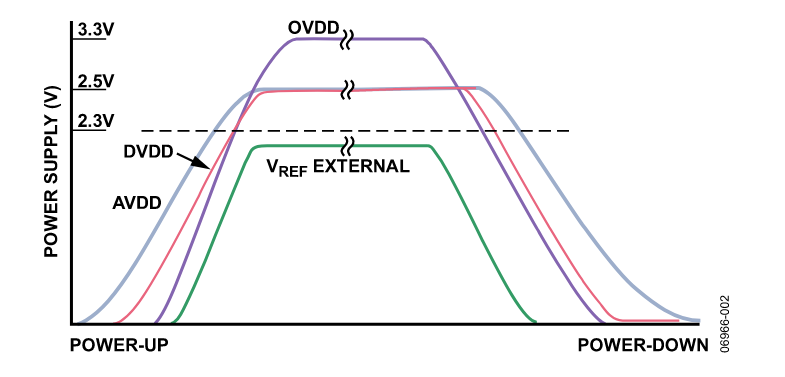

AD7794 Σ-Δ型24位ADC是另一个很好的例子。表3摘自AD7794 (Rev. D)数据手册的“绝对最大额定值”部分。

该ADC的问题与基准电压有关,它必须小于AVDD + 0.3 V。因此,AVDD必须先于基准电压或与之同时上电。

如今大部分要求高速和低功耗的电路PCB上都需要多个电源,例如:+1.8V、+2.0V、+2.5V、+3.3V、+5V、−5V、+12V和−12V。为PCB上的这些电源供电并不是一件轻而易举的事情。必须仔细分析,设计一个正确可靠的上电和关断序列。采用分立设计变得越来越困难,解决之道就是采用电源时序控制IC,只要改变一下代码就能改变上电顺序,而不用变更PCB布局布线。

原文标题:多电源IC的上电时序控制你搞明白了么?

文章出处:【微信公众号:亚德诺半导体】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- 亚德诺

-

多电源系统的监控和时序控制2018-10-19 2734

-

轻松实现复杂电源时序控制2018-10-23 3547

-

模拟时序控制解决方案:可靠的上电和关断时序2021-04-12 2343

-

如何简化并实现复杂的电源时序控制2014-08-05 4736

-

基于电源时序控制IC(参数选择细节)2017-12-02 5478

-

多电源系统的时序控制与监控控制性能分析2019-04-09 4676

-

曾经分不清的RAM知识 你现在搞明白了吗?2020-02-25 4463

-

AN-1080: 利用简单时序控制器ADM108x进行上电和关断时序控制2021-03-21 905

-

使用通用电源IC实现电源时序控制的电路2022-01-18 6624

-

多电源IC的上电时序控制你搞明白了么?2022-12-16 2490

-

多电源IC的上电时序控制你搞明白了么2022-12-19 2632

-

使用通用电源IC实现电源时序控制的电路 —总结—2023-02-23 2577

-

多电源系统监控和时序控制介绍2023-11-22 516

-

电源时序控制的正确方法,你掌握了吗?2023-12-15 2555

-

你知道激光钻孔技术有多牛吗?看完这篇文章你就明白了2024-02-29 2173

全部0条评论

快来发表一下你的评论吧 !