FPGA User Guide之report_cdc

可编程逻辑

1397人已加入

描述

report_cdc 可以报告设计中所有的 cdc 路径并将其分类(前提是时钟被约束好),我们可以基于该报告来检查设计中是否有不安全的 cdc 路径。

本文主要是总结几个不常见的 CDC 类别。

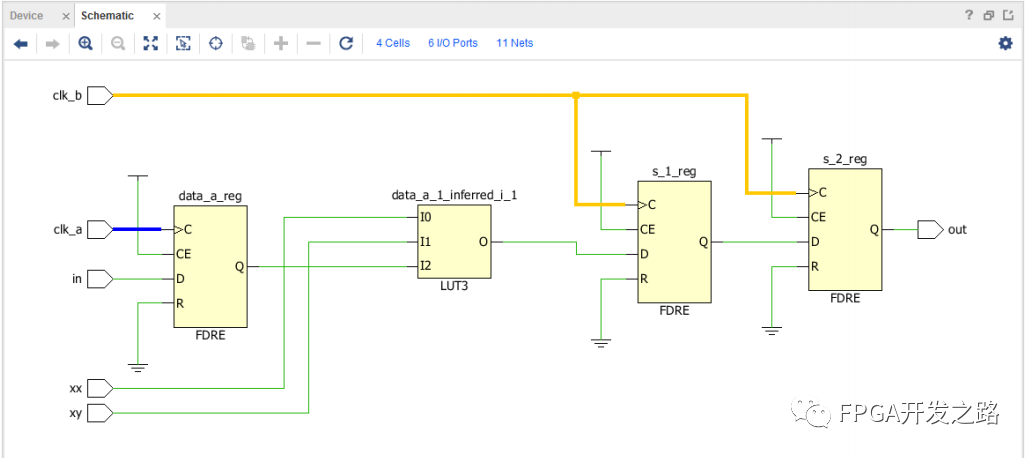

Combinatorial Logic

图1所示,LUT3是位于两个时钟域之间的组合逻辑。这样的设计一般是不建议的,因为组合逻辑的毛刺可能会被同步器抓到并传到后级电路,毛刺也更容易导致亚稳态的发生。

图1

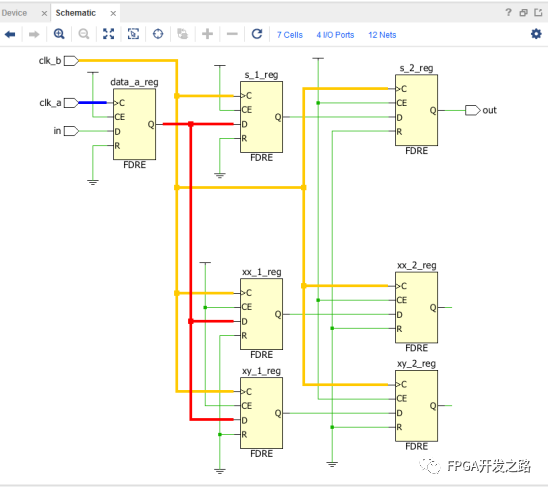

Fanout

图2所示,在 clk_b 时钟域有三个同步器采样同步同一个信号。这样的设计也是不建议的,因为会导致数据一致性的问题。我们知道,同步器只能避免亚稳态但不同保证数据值正确,所以三个同步器的输出值可能会不一样。

图2

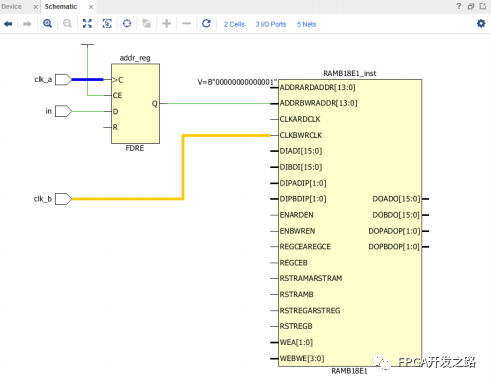

Non-FD Primitive

如图3所以,在寄存器 FDRE 和 RAMB 之间是有 CDC 路径的。RAMB 内部没有同步器,所以这个 CDC 路径会被认为是不安全的。

图3

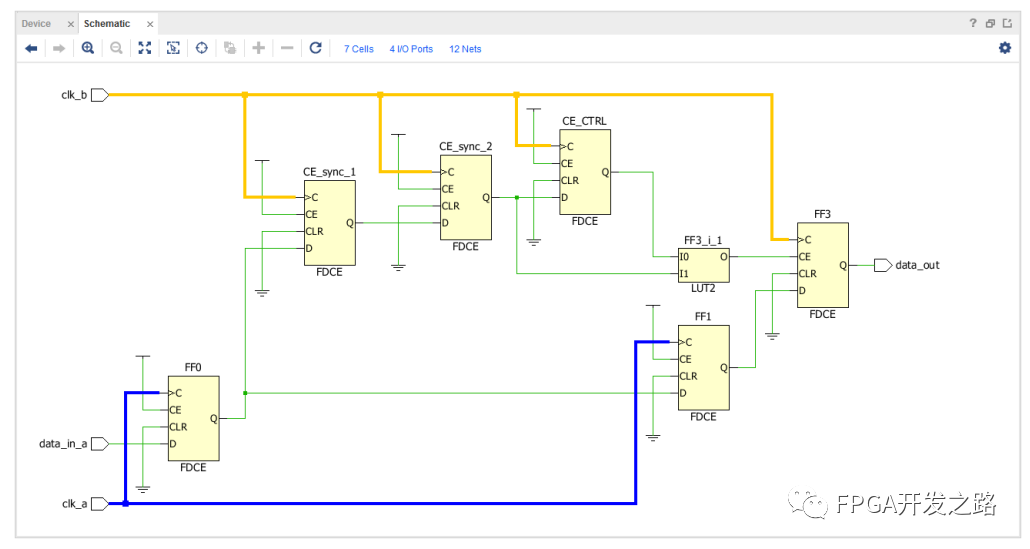

CE-Controlled CDC

如图4所示,clock enable 信号经过两级寄存器已经被同步到 clk_b 时钟域,vivado会认为其是一条安全的cdc path。用户需要自己约束从clk_a到FF3的CDC path,一般是用 set_max_delay -datapath_only。

图4

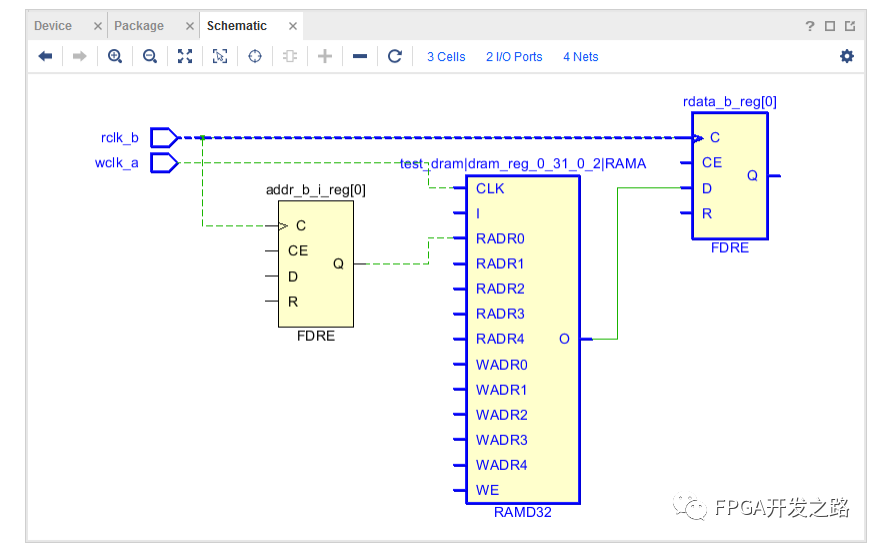

LUTRAM Read/Write Potential Collision

如图5所示,LUTRAM 读写使用不同时钟,当 读写地址刚好相同时,会有 CDC path,即从 RAM 的 CLK pin 到 rdata_b_reg 的 D pin。

图5

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

评论(0)

发评论

-

陆小凤16

2022-11-30

0 回复 举报很好 1条回复 收起回复

陆小凤16

2022-11-30

0 回复 举报很好 1条回复 收起回复 -

陆小凤16

0

非常好

陆小凤16

0

非常好

-

heminlites041

2022-11-30

0 回复 举报有用的 1条回复 收起回复

heminlites041

2022-11-30

0 回复 举报有用的 1条回复 收起回复 -

heminlites041

0

棒棒的

heminlites041

0

棒棒的

-

ADRV9026 System Development User Guide2021-01-31 1313

-

ADZS-AD2428MINI User Guide2021-01-28 1040

-

如何使用report_cdc命令分析、调试和修复CDC问题2018-11-21 5696

-

Freescale P4080 PCIe User Guide2017-10-24 1392

-

Stellaris Peripheral Driver Library User's Guide2017-10-11 1171

-

JTAG ICE User Guide2017-09-21 1136

-

Spartan-6 FPGA Configuration User Guide2017-09-19 2134

-

Panasonic KXTDA User Guide2017-09-09 978

-

Panasonic KX-TDA User Guide2017-09-08 1213

-

The OpenCV User Guide2016-08-26 940

-

REB233-XPRO User Guide2016-07-08 766

-

i.MX_6_WaylandWeston_User_Guide2015-12-29 1382

-

Virtex-6 FPGA GTX收发 User Guide2009-12-31 917

-

MegaCore Function User Guide2006-03-25 999

全部0条评论

快来发表一下你的评论吧 !