逻辑综合与物理综合

电子说

描述

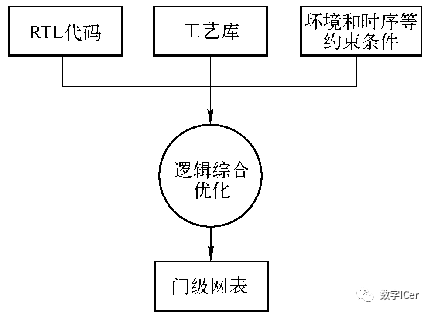

1.逻辑综合

利用工具将RTL代码转化为门级网表的过程称为逻辑综合。综合一个设计的过程,从读取RTL代码开始,通过时序约束关系,映射产生一个门级网表。

1 流程介绍

1.用硬件描述语言进行设计

读入的设计,通常是采用硬件描述语言(HDL)编写的,如Verilog和VHDL。

2.指定工艺库

在根据约束条件进行逻辑综合时,对于选择的流片工艺,工艺库将提供综合工具所需要的标准单元的全部信息,即工艺库含有特定工艺下的标准单元的逻辑功能、单元的面积、输入到输出的时序关系、输出的扇出限制和对单元时序检查所需的信息等。

3.读入设计

把HDL描述的设计,即RTL代码输入给综合工具,由综合工具进行编译,综合工具在综合时会首先检查代码的可综合性。

4.定义环境约束条件

定义本设计要综合时的环境,包括设计的工艺参数(温度、制造工艺、电压)、I/O端口属性等。

5.设定设计的约束条件

约束条件将指定综合工具按照什么样的原则来综合电路,该电路所要达到的指标是什么。

2 定义时钟

定义芯片所需的内部时钟信号。

通常时钟网络在综合过程中是不做处理的,会在后续的布局布线中插入时钟树,减小其时钟偏斜。

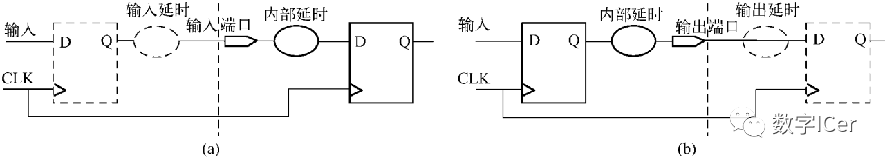

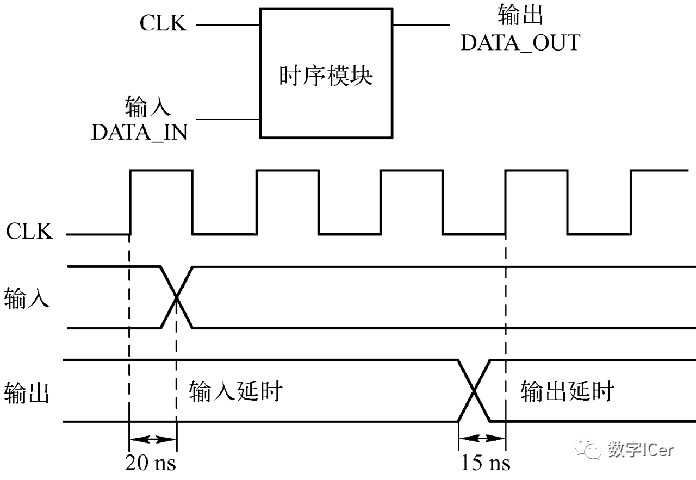

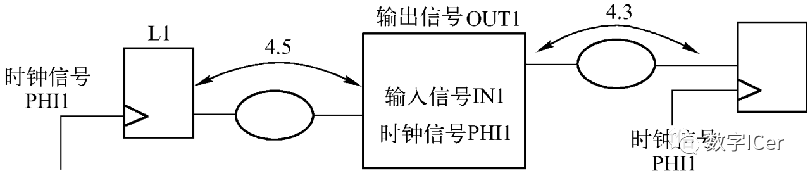

输入/输出延时

为保证片外的触发器可以正确地输入/输出,不仅要保证片内的延时要满足时序要求,而且要保证片内外延时总和要满足时序要求 。

输入/输出延时示意

输入/输出延时示意

3 设定设计规则约束

设定设计规则约束包括节点上信号最大跳变时间(Max Transition)、最大扇出(Max Fanout)、最大电容(Max Capacitance)等。合理的设定这些约束条件将有利于控制功耗,保证信号完整性。

这3个约束可以设置在输入端口、输出端口及当前设计上。通常这些约束在工艺库内已经设定,由工艺参数决定大小。如果库内设定的值不够恰当或者过于乐观,可以根据设计需要专门设置。

4 面积约束

面积约束是指定设计的最大面积值,如果设计超过了这一面积就违反了约束。

在将设计实体转换成门级电路时,通常要加面积约束条件。这一设计指标,也是逻辑综合过程中进行优化的依据之一。多数的逻辑综合工具允许设计者按工艺库中门级宏单元所用的单位来指定面积的约束条件。

5 优化设计

优化的主要目的是在满足时序要求的前提下尽量减小芯片面积。与工艺无关的优化缺乏非常准确的时序信息,因而注意力往往集中在优化面积上。等到映射之后时序信息比较准确时再进行修正更有效。

架构优化:如选择DesignWare实现所需功能等。

逻辑优化:重构(优化面积)与展平(优化速度)。

门级优化:映射、延时优化、设计规则修正、面积优化。

SoC设计中常用的综合策略

有两种基本的综合策略可以选择,即自顶向下(Top-down)与自底向上(Bottom-up)。

在自顶向下综合策略里,顶层设计与其子模块同时编译,仅需要施加顶层约束。

自底向上的综合策略是指先单独地对各个子模块进行约束与综合,完成后,赋予它们不再优化(Dont_touch)属性,将它们整合到上一层模块中,进行综合,重复这一过程,直至综合最顶层的模块。

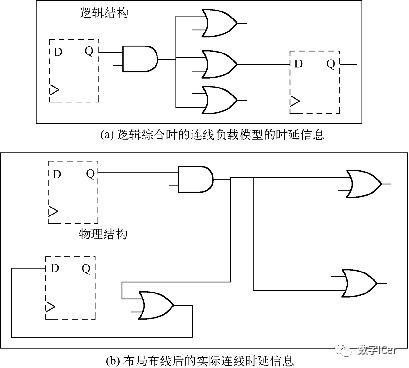

2.物理综合

传统的逻辑综合方法是依赖于连线负载模型(Wire-load Model)的,随着工艺尺寸的不断缩小及芯片复杂性的增加,整个电路的延时信息更多取决于互连线延时。

在物理综合时,就考虑布局布线的问题了。

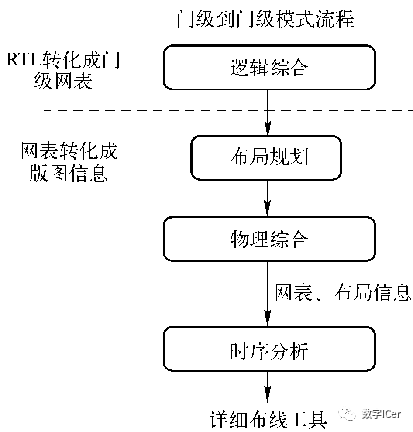

操作模式

物理综合要求的约束条件通常有芯片尺寸、引脚位置、线上负载信息、版图规划信息等。一般使用以下两种操作模式。

RTL到门级模式:在RTL到门级模式下,物理综合的输入信息是RTL级的设计电路、版图规划信息及含有版图信息的物理综合的库文件。

门级到布局后门级模式 :在这一模式下,与RTL到门级模式的唯一区别是物理综合的输入信息是门级网表,而不是RTL级的设计电路。

相对而言,RTL到门级模式所花费的时间要比门级到门级模式的时间长。

物理综合的流程图

物理综合的流程图

更多请查看 : 综合与时序分析

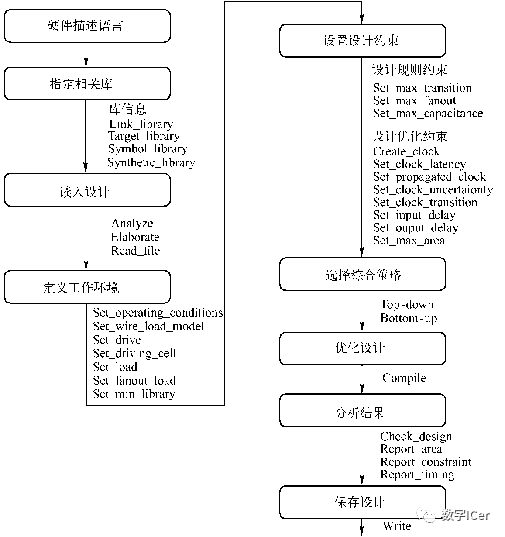

实例:用Design Compiler 进行逻辑综合

在综合的各个步骤中所经常用到的命令

在综合的各个步骤中所经常用到的命令

(1)指定库文件

在综合之前,需要用一个名为“.synopsys_dc.setup”的初始化文件建立综合的环境。在该文件中,通过向相关环境变量赋值,来定义工艺库的位置及综合所需要的参数。

synopsys的安装目录下:对于UNIX系统来说,它通常位于“$SYNOPSYS/admin/setup”目录下。用于卸载synopsys工艺独立库及别的参数,不包含设计相关的数据。

用户根目录下:这里的setup文件包含用户对于自己DC工作环境的参数设置。

启动DC的当前目录:这里的setup文件包含因项目与设计而异的变量设置。

Setup文件的内容

search_path:由目录列表组成。当DC搜索某个未指定路径的文件(如库、设计文件等)时,将由search_path中定义的路径中去搜索该文件。通常将其定义为某个主要的库文件所在的目录路径。

target_library:指定对设计进行综合时采用的工艺库,由厂家提供。该库中的器件被DC用于逻辑映射。本变量指定的库文件名,应该也包含在link_library所列出的内容中,用于供DC读取门级网表。

link_library:该变量指定的库文件中的器件将不会被DC用来进行综合,如RAM、ROM及I/O。在RTL设计中,将以实例化的方式进行引用。

symbol_library:该变量指定的库文件包含有工艺库中器件的图形化信息,用于生成图形化原理图。

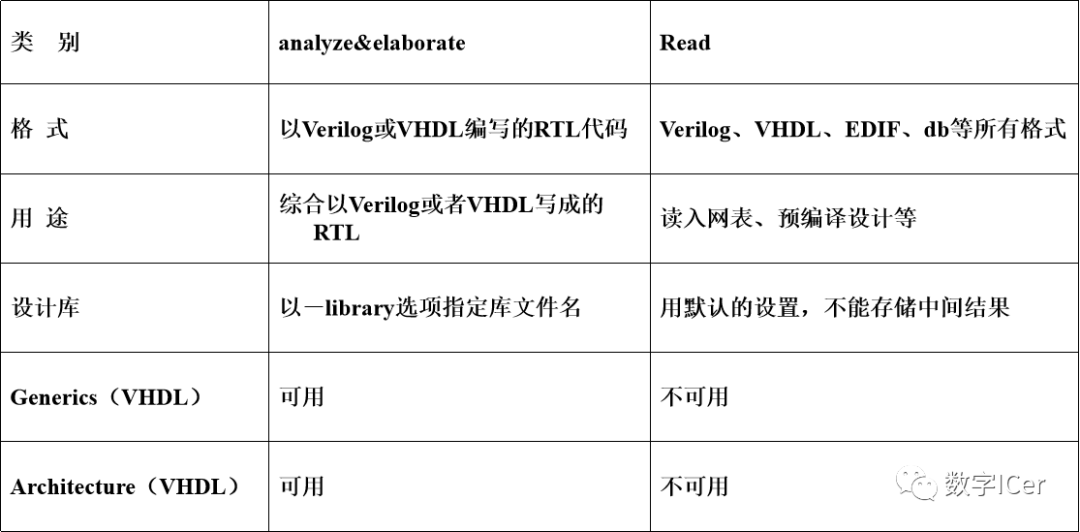

(2)读入设计

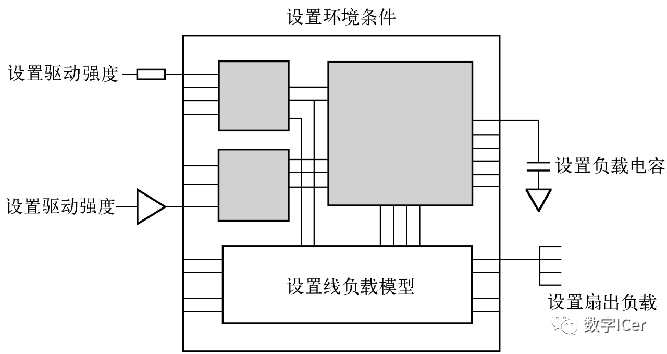

(3)定义工作环境

设置环境条件(set_operating_conditions)

设置线负载模型(set_wire_load_model)

设置驱动强度(set_drive与set_driving_cell)

设置电容负载

设置扇出负载(set_fanout_load)

(4)设置约束条件

设置设计规则约束(set_max_transition、set_max_fanout、set_max_capacitance)

例如:set_max_transition 0.3 current_design

例如:set_max_capacitance 1.5[get_ports out1]

例如:set_max_fanout 3.0[all_outputs]

时钟定义的相关命令

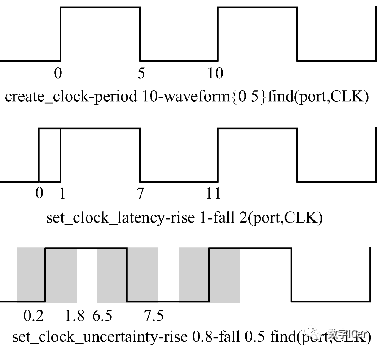

create_clock用来定义一个时钟的周期和波形

set_clock_latency定义时钟网络的延时

set_clock_uncertainty定义时钟偏斜值

时钟定义

create_generated_clock定义一个内部生成的时钟。可以将内部分频或者倍频产生的时钟定义为初级时钟的函数。

例如:create_generated_clock -name GENCLK -source CLKIN -divide_by 2[get_pins idiv/ div_reg/Q]

对于只含有组合逻辑的模块,为了定义该模块的延时约束,可以创建一个虚拟时钟,再相对于虚拟时钟定义输入/输出延时。

设置输入/输出端口的延时

输入延时定义了信号相对于时钟的到达时间,指一个信号在时钟沿之后多少时间到达。

输出延时则定义输出信号相对于时钟所需要的到达时间,指一个信号在时钟沿之前多少时间输出。

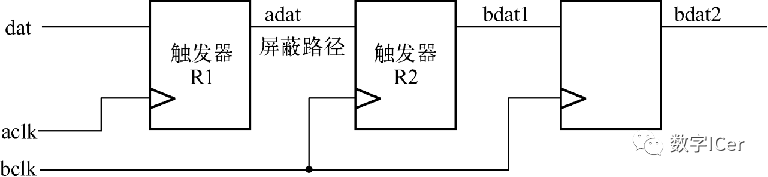

特别路径的约束

虚假路径(set_false_path)是指由于逻辑功能、数据顺序或操作模式等原因,从来不会激活或者不需要考虑的路径。

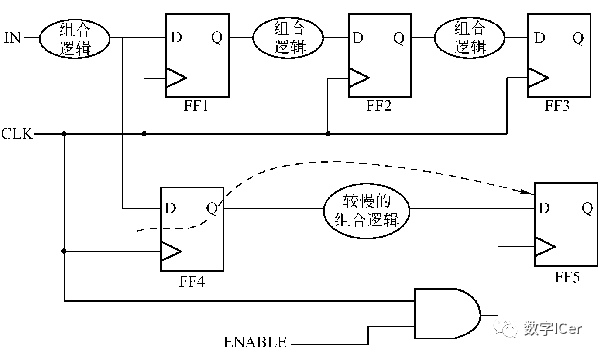

设置多周期路径

设置多周期路径(set_multicycle_path),指设计中从发送数据到采样到数据的时间允许多于一个时钟周期的路径。虚线标出了多周期路径。

(5)设定综合优化策略

通过使用compile命令调用DC,对设计进行综合与优化。该命令有许多选项可以选择,其中,映射努力(map_effort)即要求工具优化的程度,可以设置为低、中、高。

在初次编译时,如果需要对整个设计的性能和面积等有一个大致的了解,可以将map_effort设置为低。默认的map_effort级别为中,而在最后一次编译中,可以将map_effort设置为高。通常,将map_effort设置为中即可。

审核编辑:汤梓红

-

【「龙芯之光 自主可控处理器设计解析」阅读体验】--LoongArch逻辑综合、芯片设计2026-01-18 844

-

什么是逻辑综合?逻辑综合的流程有哪些?2023-09-15 8300

-

逻辑综合的流程和命令简析2023-08-09 2053

-

芯片设计之逻辑综合过程2022-08-12 4725

-

什么是逻辑综合?2021-11-02 3393

-

Tcl与Design Compiler (八)——DC的逻辑综合与优化 精选资料分享2021-07-30 1252

-

DC逻辑综合详解2021-07-29 1193

-

如何使用DCNXT实现物理综合?2021-06-23 4257

-

怎么借助物理综合提高FPGA设计效能?2021-05-07 1720

-

请问如何通过物理综合与优化去提升设计性能?2021-04-14 1776

-

求一套手工逻辑综合的方法和综合步骤?2021-04-08 1284

-

ASIC逻辑综合及Synopsys Design Compiler 的使用资料说明2019-10-23 1053

-

浅谈IC设计中逻辑综合2013-05-16 6004

-

DC逻辑综合2011-12-29 905

全部0条评论

快来发表一下你的评论吧 !