I2C总线上拉电阻设计要点

接口/总线/驱动

描述

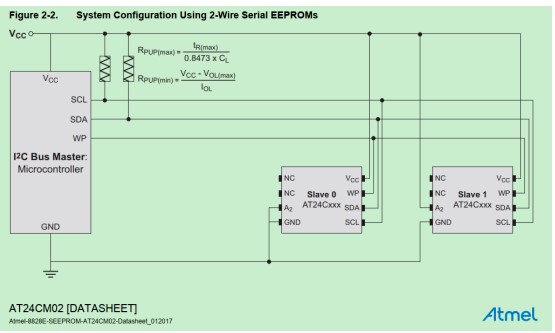

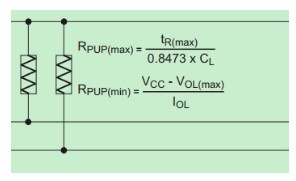

上周翻了下AT24CM02芯片的数据手册,里面提到了I2C上拉电阻的设计要点,只有两个公式就简洁地把上拉电阻阻值范围确定了,非常实用,详细见图1。实际上,以前我从来没有注意过I2C上拉电阻设计,总是随便选一个(如4.7K或者10K),软件测试正常就不再管了,但居然没有出现过问题,可能有些侥幸吧。想起几年前听别人说他认识一个工作在消费类电子行业的硬件工程师,即使是I2C都会测试的特别细致,因为出货量非常大,几万数量级,所以每个细节都必须做好;否则可能风险会比较大。而本文主要是对AT24CM02数据手册中提到的I2C上拉电阻的两个公式进行说明(公式是通用的)。

图1 I2C上拉电阻设计要点

第一,I2C上拉电阻最小值确定

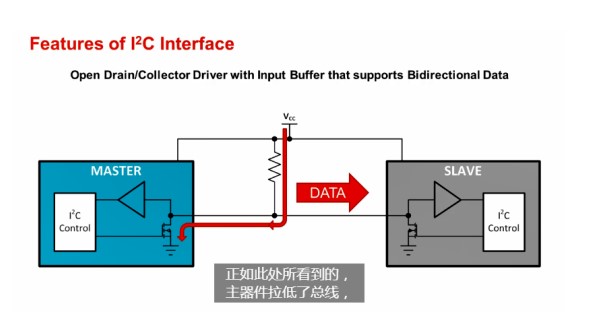

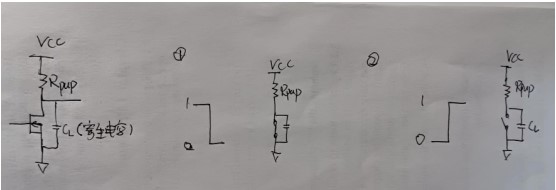

为什么I2C需要上拉电阻才能通讯呢?因为SDA和SCL是开路漏极或者开路集电极输出,所以如果没有上拉电阻,芯片是无法输出高电平的,可参见图2。

图2 I2C硬件框图

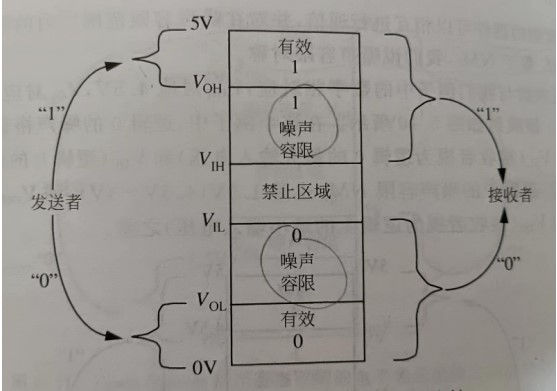

要理解I2C上拉电阻的最小值考虑,需要回顾下数字电路的静态协议,参见图3。从图2中可以看到,当master输出拉低时,它是在输出低电平即VoL。从图3中可以看到,发送者的VoL要低于接收者的ViL,这样才能有噪声容限(数字电路设计相对模拟电路简单也跟噪声容限大有关如0.7V)。ViL固定,那么VoL越低则噪声容限越大,这样就越不容易受到外界环境干扰。

图3 数字电路的静态协议

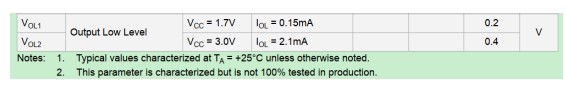

如AT24CM02芯片,它的手册中是写到了VoL具体值的,参见图4。而厂家测试Vol值时也会有个测试条件即IoL和Vcc。所以这两个值确定好后就可以计算出I2C上拉电阻的最小值了。

图4 AT24CM02数据手册DC特征中的VoL(这里如VoL2的0.4V是最大值)

我们算一下Rpup(min)好了。Vcc=3V时,VoL=0.4V,IoL=2.1mA代入图5中的公式,得到Rpup(min)≈ 1.238kΩ(如果小于这个值那么VoL会变大,会减小噪声容限)。

图5 I2C上下拉电阻计算公式

实际应用时更可能会是3.3V,而不是3V,那么IoL应该会比2.1mA大(参见图4中Vcc=1.7V和Vcc=3V时IoL的区别)。这可能跟mos管的特性有关系,因为芯片供电电压高,mos管的驱动电压也会高的,导通后的Rds(on)会更小,所以IoL更大。

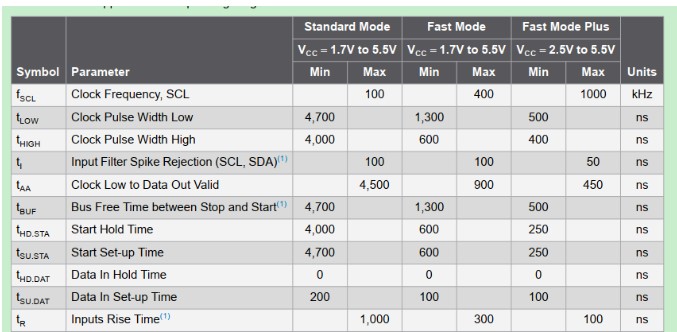

第二,I2C上拉电阻最大值确定

上拉电阻的最大值是什么决定的呢?是由于芯片I2C通信速率决定的,因为电路板会有寄生效应如寄生电容,它和上拉电阻正好形成了串联RC电路,会有时间延迟,而这个延迟必须要小于电平低有效到高有效的时间,否则芯片读到的电平是错误的。

从图2中I2C硬件架构可以知道,芯片从0到1的实现方式是把mos管或者三极管关断,而从1到0是把mos管或者三极管打开。从1到0时间是非常快的,因为mos管或者三极管导通后电阻很小、相当于导线,所以上面压降非常小(V=I*R)。而从0到1时间会受到RC的影响,因为电容两端的电压即ViH。这也是I2C上拉电阻不能太大的原因。

图6 I2C逻辑电平0~1和1~0的简化原理图

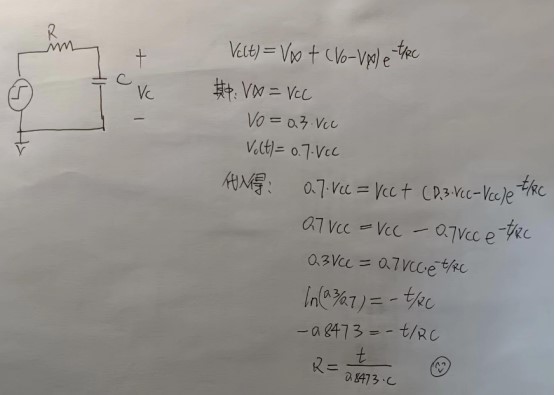

从图5公式中我们可以看到,这里有tr,CL和Rpup,所以这个公式应该是出自电路课本里面一阶电路的暂态响应。这里的0.8473是怎么来的呢?详细参见图7。

图7 Rpup(max)计算公式的推导

最后,实际算下Rpup(max)。图5中求Rpup(max)公式中的CL,不仅包括芯片的寄生电容,还有走线的寄生电容。假设CL(total)=50pf,tr=100ns,代入公式后得到Rpup(max)≈ 2.3604kΩ。因此Rpup取值在 1.238kΩ~2.3604kΩ之间都是可以的。虽然上拉电阻阻值大体选好了,但最好要实测小I2C总线波形是否正常等,因为假设了一些东西比如CL=50pf,实际参数不一定是这样的。至于I2C总线如何测试,我暂时还不清楚。

补充,我试了下,如果CL过大比如100pf,那么公式计算出来的Rpup(max)≈ 1.1802kΩ,它是小于前面计算出来的Rpup(min)≈ 1.238kΩ。可能I2C总线layout时候要特别注意下寄生电容,否则就不能保证VoL更小了。

图7 tr在Vcc=3V时候为100ns

-

I2C总线上拉电阻的计算实例2023-06-02 2554

-

聊聊I2C总线上拉电阻2023-07-14 6820

-

I2C总线上拉电阻阻值如何确定?2024-12-27 3223

-

开发板I2C总线上为什么没有上拉电阻呢2022-01-05 1921

-

I2C总线上拉电阻设计要点2022-11-29 8256

-

I2C总线应用中的几个问题2009-09-13 1542

-

I2C总线一定要接上拉电阻?上拉电阻阻值怎么确定?2021-06-21 16943

-

I2C上拉电阻设计2022-01-14 1413

-

I2C总线的常见通信方式2022-06-29 8045

-

上拉电阻在I2C电路中的作用 I2C上拉电阻的计算方法2023-07-25 4962

-

关于I2C总线的6个问题分析2023-12-25 3188

-

I2C总线上拉电阻的必要性2024-09-09 2966

-

I2C总线上拉电阻计算2024-10-08 633

-

I2C总线为什么要接上拉电阻2024-11-20 2485

-

如何选择I2C总线拉电阻2025-01-17 1930

全部0条评论

快来发表一下你的评论吧 !