荣湃隔离RS-485收发器

描述

RS-485收发器

RS-485收发器是由美国的电子工业协会(EIA)于1983年发布的一个平衡差分信号传输的标准。RS-485收发器标准(即TIA/EIA-485-A)定义了 RS-485收发器 接口的物理层,仅定义了驱动器和接收器的电气特性,很多更高级别的协议标准将RS-485收发器作为物理层标准,例如Profibus, Modbus等。

RS-485收发器优点

01

平衡差分信号传输可以抑制共模噪声,便于在有噪声的工业环境中实现远距离通信

02

支持–7V至12V宽共模电压范围,允许有一定地电位差的节点之间进行多点数据传输

03

短距离的数据速率可高达 50Mbps,较低数据速率下的通信距离可长达1000米

RS-485收发器模式

半双工模式VS全双工模式

RS-485收发器分为两种网络配置:半双工模式及全双工模式。

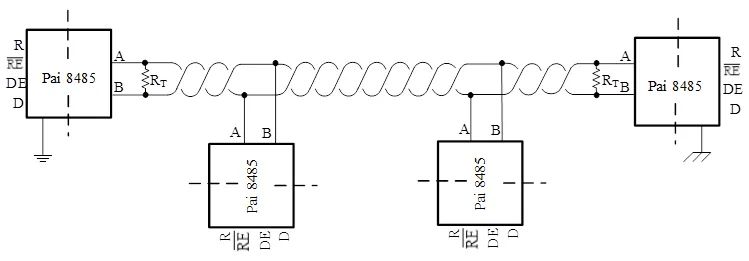

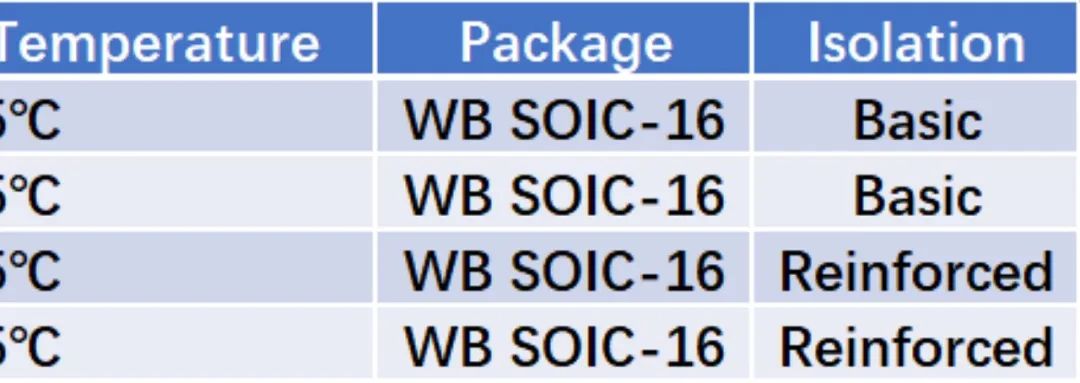

△半双工模式配置图△

在半双工模式下,多个收发器由一对线缆连接,在同一时刻,收发器只能发送或接收信号,而不能同时进行信号的发送和接收,并且只能有一个收发器处于发送信号状态,如有多个收发器在发送状态会导致数据错误,并有可能引起收发器的损坏。

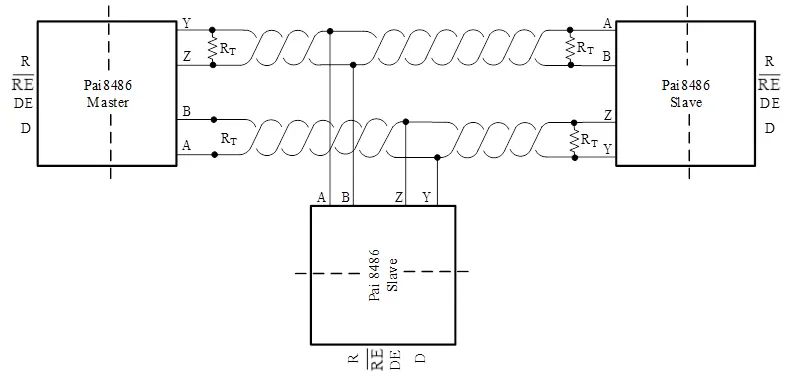

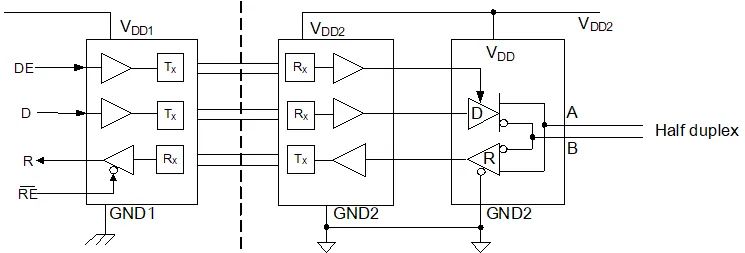

△全双工模式配置图△

全双工配置通常为主从模式,在这种模式下,需要两对线缆,主收发器的发送端与从收发器的接收端通过一对线缆连接,从收发器的发送端与主发送器的接收端通过另一对线缆连接。在全双工模式下,主从收发器之间可以同时进行数据的发送和接收。

一般而言,半双工模式由于只需一对线缆成本较低,比较常见于一般应用,全双工模式多用于数据带宽较高的应用场景。

RS-485收发器标准要求

RS-485收发器标准规定Driver在54欧姆的负载上提供不小于1.5V的差分输出,Receiver可检测到低至200mV的差分输入,即使在信号严重衰减的情况下,这两个值仍能为高可靠性的数据传输提供充足的余量。

荣湃隔离RS-485收发器产品参数

荣湃隔离RS-485收发器产品是基于智能分压技术设计而成。智能分压技术又称为iDivider 技术,是荣湃半导体创新发明一项专利技术,具有功耗低、延时短、速率高以及EMC性能好等优点。

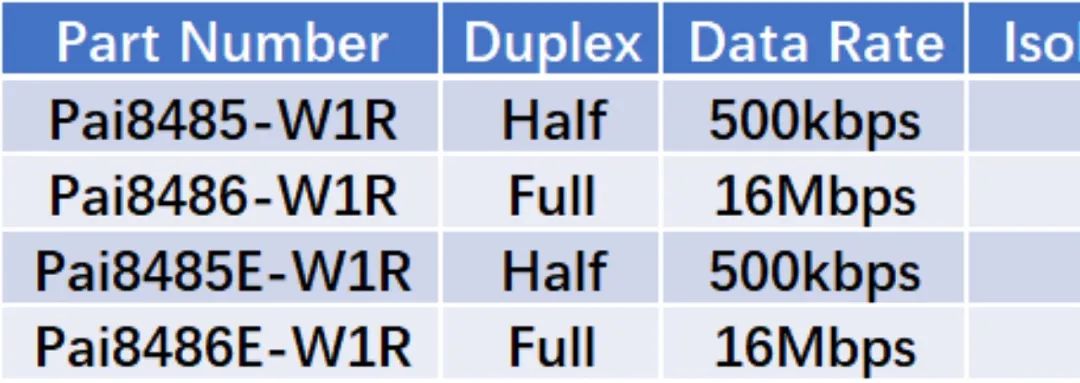

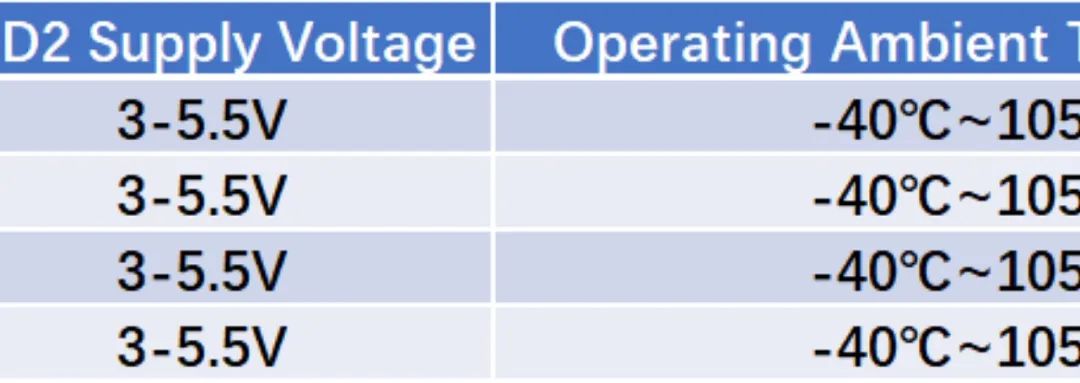

左右滑动查看更多参数

△荣湃隔离RS-485收发器参数示例△

荣湃将会推出四款隔离RS-485收发器产品,包括半双工隔离RS-485收发器、Pai8485/Pai8485E和全双工隔离RS-485收发器、Pai8486/Pai8486E,四款产品均为8mm爬电距离的WB SOIC-16封装,隔离耐压均为5kV rms。

△荣湃隔离半双工RS-485收发器功能框图△

△荣湃隔离全双工RS-485收发器功能框图△

由图可见,荣湃隔离RS-485收发器内部集成了一个类似三通道的数字隔离器和一个RS-485收发器。

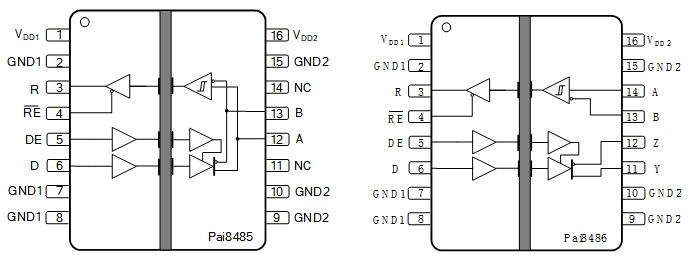

△荣湃隔离半双工RS-485收发器和

隔离全双工RS-485收发器PIN脚配置图△

由图可见,荣湃隔离半双工RS-485收发器与隔离全双工RS-485收发器 在Side1侧的PIN脚配置完全一致,Side1侧的PIN3(R脚)为Receiver的输出,PIN4(/RE脚)为Receiver的使能脚,这里Receiver为低电平使能。PIN6(D脚)为Driver的输入,PIN5(DE脚)为Driver的使能脚,Driver为高电平使能。

荣湃隔离RS-485收发器产品性能

01

满足TIA/EIA-485-A的标准规范

02

隔离半双工RS-485收发器的数据速率可达500kbps,隔离全双工RS-485收发器的数据速率高达16Mbps

03

隔离耐压高达5000V RMS,适用于高隔离耐压场合

04

逻辑侧(即Side1侧)供电电压范围为2.5V至5.5V

05

总线侧(即Side2侧)供电电压范围为3V至5.5V

06

总线引脚ESD能力:

1)总线引脚对GND2 IEC61000-4-2 同侧ESD接触放电>12kV

2)总线引脚对GND1 IEC61000-4-2 异侧ESD接触放电>8kV

3)总线引脚对GND2 HBM ESD 为±30kV除总线引脚,其他引脚HBM ESD为±8kV。荣湃隔离RS-485收发器产品的总线引脚ESD能力强

07

总线上的共模电压范围为-7V至12V

08

高CMTI,典型值为85kV/us,抗共模干扰能力强

09

具有总线安全保护功能,当总线开路、短路或处于自由状态时,Receiver输出高电平保护

10

1/8单位负载,总线上可支持多达256个节点

11

工作温度从-40℃到105℃,工作温度范围宽

12

封装为宽体SOIC-16封装,与市面上的绝大多数隔离RS-485收发器PIN 2 PIN兼容

13

隔离栅寿命>40年,寿命时间长

荣湃隔离RS-485收发器使用注意事项

以荣湃隔离半双工RS-485收发器为例,在使用隔离RS-485收发器时,VDD1和GND1之间以及VDD2和GND2之间均需要0.1μF去耦电容,而且去耦电容在PCB布局时离电源引脚越近越好。

审核编辑 :李倩

-

隔离式 RS-485 收发器参考设计2024-09-11 590

-

RS-485窄体隔离收发器2022-10-31 1230

-

隔离式RS-485收发器概述、特性及应用2022-02-18 3228

-

隔离式RS-485收发器的应用及特性介绍2021-12-03 2724

-

有关隔离式RS-485收发器的7大设计问题2020-08-19 3386

-

均方根信号和电源隔离RS-485收发器2020-05-13 1990

-

RS-485收发器怎么保证户外的正常通信?2019-07-31 1863

-

隔离型RS-485收发器设计问题总结2019-07-29 1604

-

有关隔离RS-485收发器的7个设计问题2018-08-11 4943

-

EMC COMPLIANT RS-485 收发器保护电路2015-11-02 969

-

EMC COMPLIANT RS-485收发器保护电路2014-05-26 2709

-

电表应用中RS-485收发器的设计考虑2010-12-11 782

-

嵌入式隔离RS-485收发器原理及应用2010-03-06 1240

全部0条评论

快来发表一下你的评论吧 !