可测性设计DFT

电子说

描述

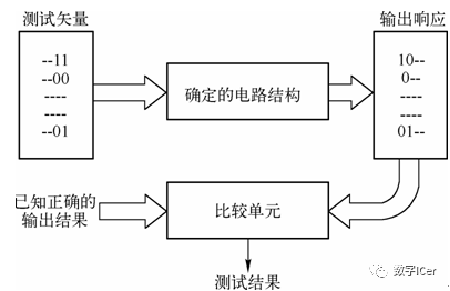

1.测试概念和原理

测试包含了三方面的内容:

已知的测试矢量

确定的电路结构

已知正确的输出结果

试方式的分类

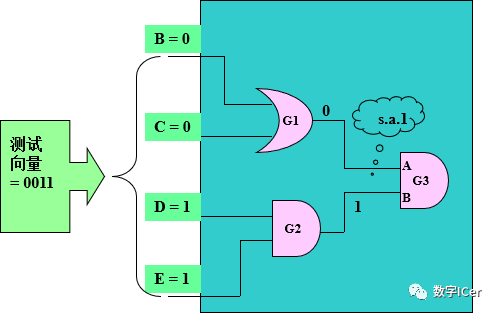

测试矢量

穷举测试矢量是指所有可能的输入矢量。

测试矢量

功能测试矢量主要应用于验证测试中,目的是验证各个器件的功能是否正确。

测试矢量

这是一种基于故障模型的测试矢量,它的最大好处是可以利用电子设计自动化(EDA)工具自动对电路产生测试向量,并且能够有效地评估测试效果。

向量举例说明

例如,如果要测试74181ALU,其有14个输入端口

穷举测试向量,就需要214=16384个测试矢量,对于一个有38个输入端口的16位的ALU来说,以10 MHz的速度运行完所有的测试矢量需要7.64个小时.

功能测试向量,要448个测试矢量,但是目前没有算法去计算矢量是否覆盖了芯片的所有功能。

结构测试向量,要47个测试矢量。这类测试矢量的缺点是有时候工具无法检测所有的故障类型。

测试的目的

寻找最小的测试向量集去覆盖更多的芯片以及板级的故障

衡量标准:故障覆盖率

2.可测性设计

可测性设计基础

所谓可测性设计是指设计人员在设计系统和电路的同时,考虑到测试的要求,通过增加一定的硬件开销,获得最大可测性的设计过程。

目前,主要的可测性设计方法有:

扫描通路测试(Scan)

内建自测试(BIST)

边界扫描测试(Boundary Scan)

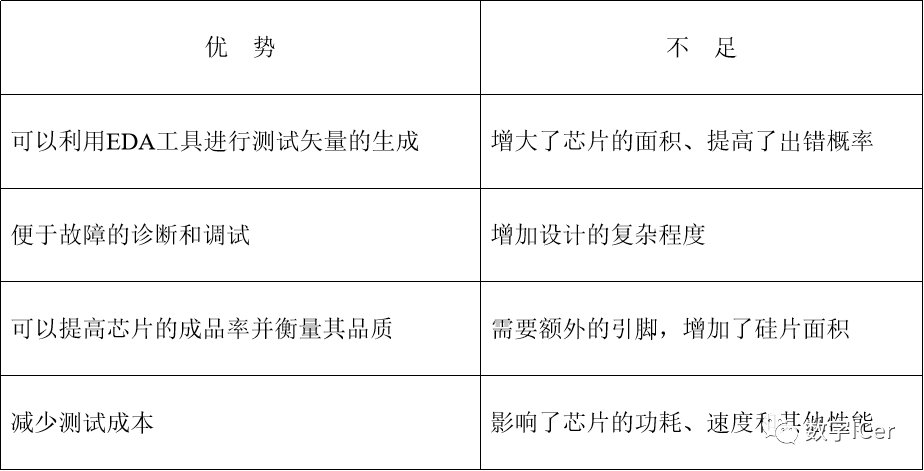

可测性设计的优势和不足

3.可测性方法(SCAN、BIST、 Boundary SCAN)

扫描通路测试 Scan

可测试性

Scan的基本概念

扫描测试设计规则

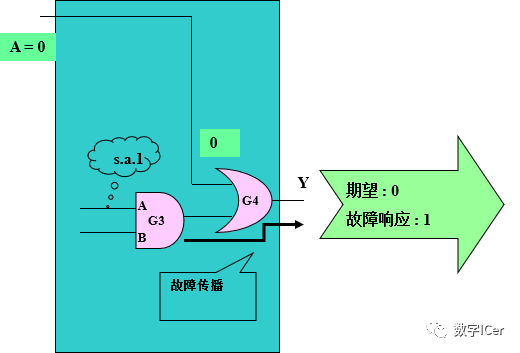

可控制性:把激励施加到被测单元的能力

可观察性:故障传播到原始输出端的能力

扫描测试的基本概念

扫描测试是目前数字集成电路设计中最常用的可测性设计技术,这里说的是内部扫描,不同于边界扫描。

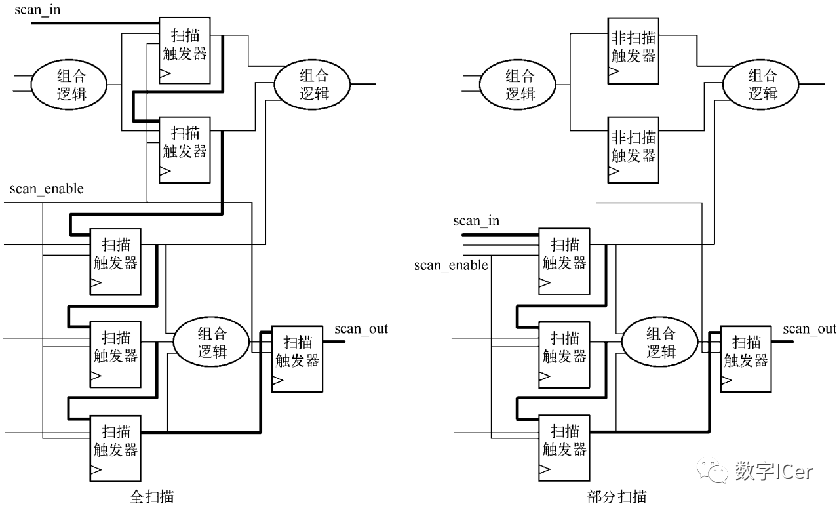

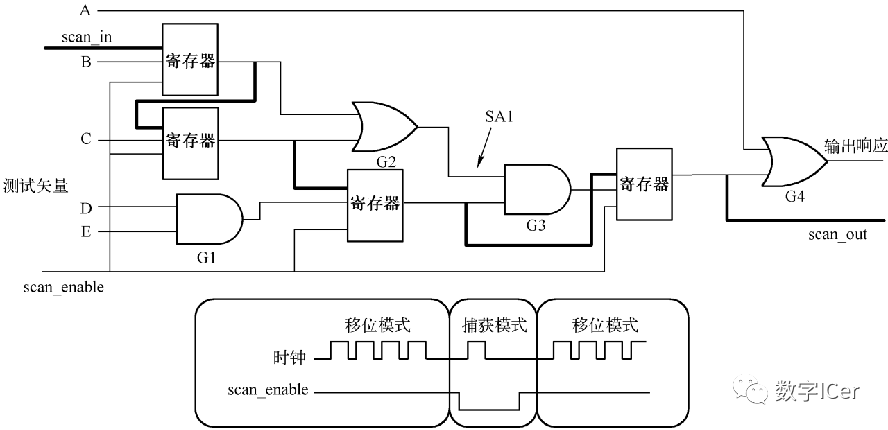

扫描时序分成时序和组合两部分,从而使内部节点可以控制并且可以观察。

测试矢量的施加及传输是通过将寄存器用特殊设计的带有扫描功能的寄存器代替,使其连接成一个或几个长的移位寄存器链来实现的。

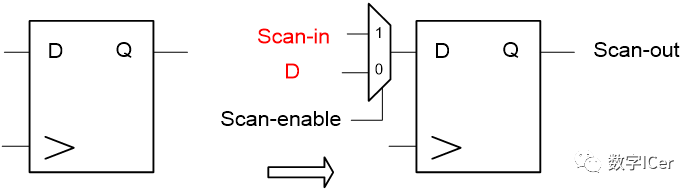

带多路选择器的D型触发器

正常工作模式:scan_enable为0,此时数据从D端输入,从Q端输出。

扫描移位模式:scan_enable为1,此时数据从scan_in输入,从scan_out端输出。

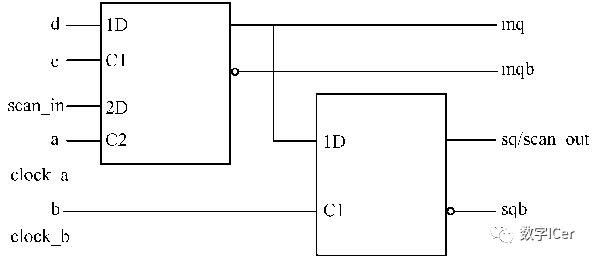

带扫描端的锁存器

全扫描和部分扫描

扫描测试原理

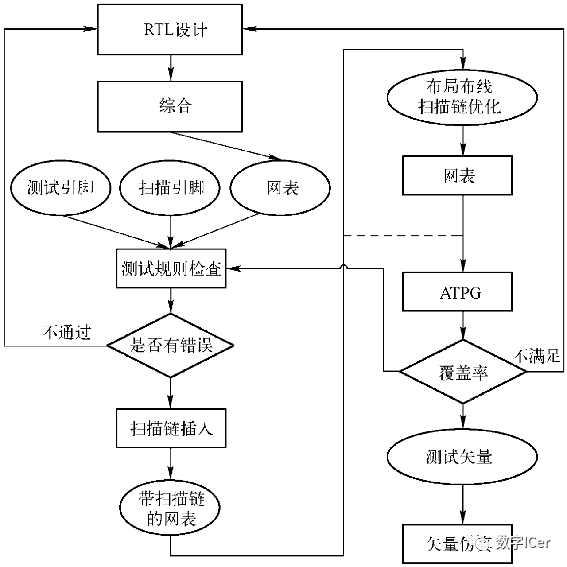

扫描设计规则

扫描测试要求电路中每个节点处于可控制和可观测的状态,只有这样才能保证其可替换为相应的扫描单元,并且保证故障覆盖率。

为了保证电路中的每个节点都符合设计需求,在扫描链插入之前会进行扫描设计规则的检查。

基本扫描规则

使用同种类扫描单元进行替换,通常选择带多路选择器的扫描触发器;

在原始输入端必须能够对所有触发器的时钟端和异步复位端进行控制;

时钟信号不能作为触发器的输入信号;

三态总线在扫描测试模式必须处于非活跃状态;

ATPG无法识别的逻辑应加以屏蔽和旁路。

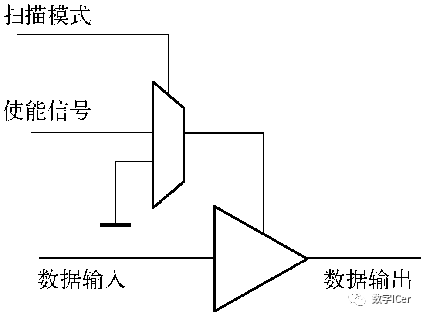

三态总线

为了避免扫描模式(scan_mode)下的总线竞争,必须控制其控制端,通常的做法是在控制端加入多路选择器,使其固定在逻辑0或者逻辑1

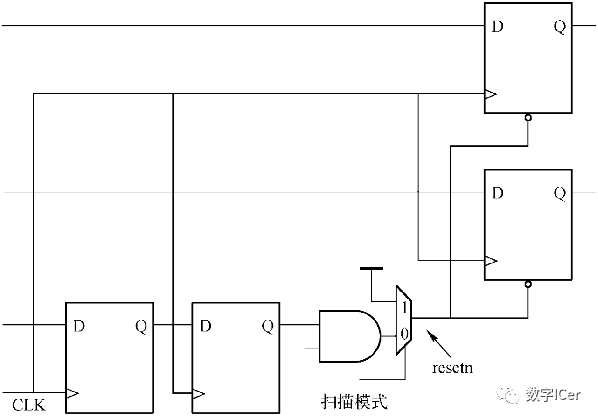

门控时钟或者门控异步输入端

为了避免扫描模式下resetn不可控制,处理方法和三态总线一样,加入额外逻辑,让异步输入端处于非有效状态

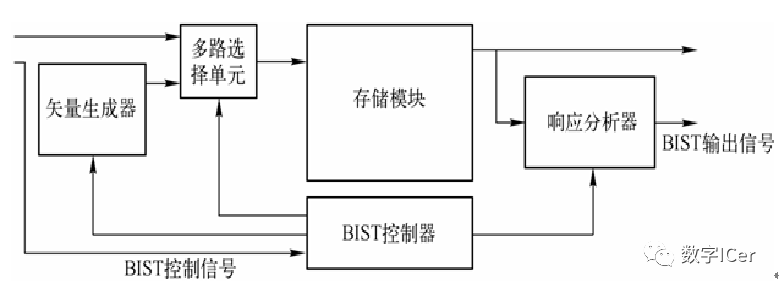

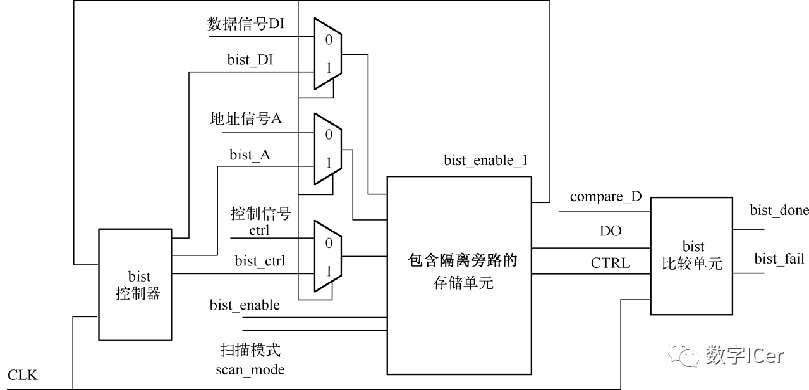

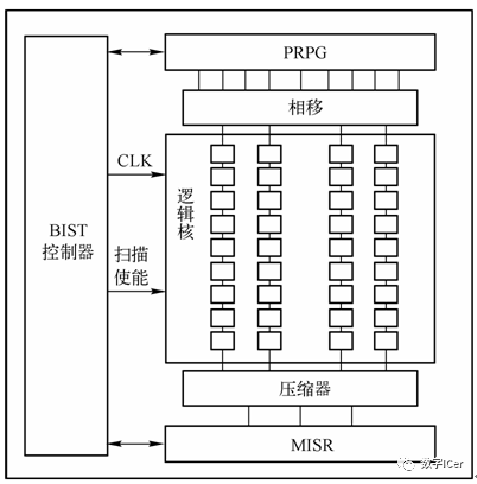

内建自测试BIST

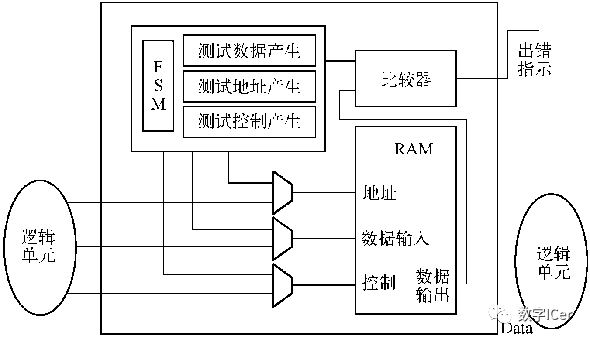

内建自测必须附加额外的电路,包括向量生成器、BIST控制器和响应分析器

BIST测试引脚:

BIST_MODE:测试模式选择信号,控制电路进入BIST状态。

BIST_RESET:初始化BIST控制单元。

BIST_CLK:BIST测试时钟。

BIST_DONE:输出信号,标志自测结束。

BIST_FAIL:输出信号,标志自测失败,说明存储器有制造故障。

BIST模块在设计中的集成

BIST电路作为逻辑电路的一部分通常在RTL级插入,并且需要与其他逻辑一起进行综合。数据、地址和一些控制信号在进入存储器之前需要经过多路选择器。

许多EDA工具可以在RTL级自动生成BIST电路并集成到设计中,其中最常用的是Mentor的mBISTArchitect和Synopsys的SoCBIST

边界扫描测试

IEEE 1149.1标准

边界扫描是欧美一些大公司联合成立的一个组织——联合测试行动小组(JTAG),为了解决印制电路板(PCB)上芯片与芯片之间互连测试而提出的一种解决方案。由于该方案的合理性,它于1990年被IEEE采纳而成为一个标准,即IEEE 1149.1。

该标准规定了边界扫描的测试端口、测试结构和操作指令。

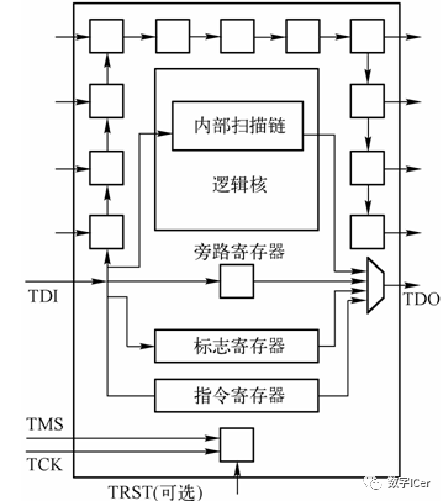

IEEE 1149.1结构

主要包括TAP控制器和寄存器组。

寄存器组包括边界扫描寄存器、旁路寄存器、标志寄存器和指令寄存器

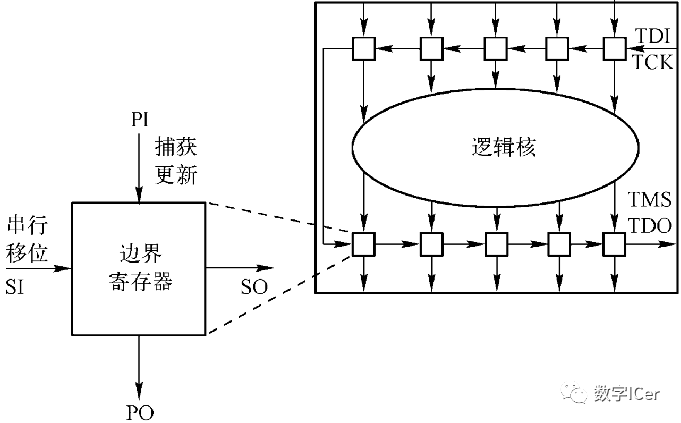

JTAG的基本原理

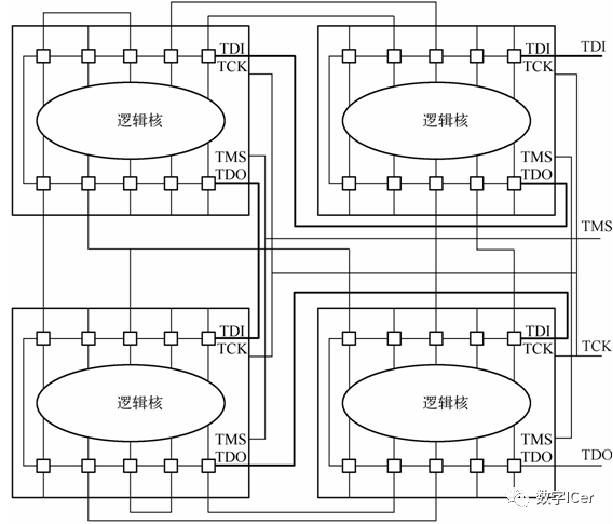

是在器件内部定义一个TAP(Test Access Port,测试访问口)通过专用的JTAG测试工具对内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。

端口定义

TCK:Test Clock边界扫描设计中的测试时钟是独立的,因此与原来IC或PCB上的时钟是无关的,也可以复用原来的时钟。

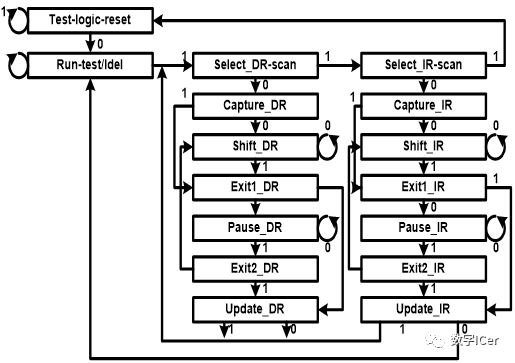

TMS:Test Mode Select由于在测试过程中,需要有数据捕获、移位、暂停等不同的工作模式,因此需要有一个信号来控制。在IEEE 1149.1中,仅有这样一根控制信号,通过特定的输入序列来确定工作模式,采用有限状态机来实现。该信号在测试时钟TCK的上升沿采样。

TDI:Test Data In以串行方式输入的数据TDI有两种。一种是指令信号,送入指令寄存器;另一种是测试数据(激励、输出响应和其他信号),它输入到相应的边界扫描寄存器中去。

TDO:Test Data Out以串行输出的数据也有两种,一种是从指令寄存器移位出来的指令,另一种是从边界扫描寄存器移位出来的数据。

除此之外,还有一个可选端口TRST,为测试系统复位信号,作用是强制复位。

边界扫描的原理

在核心逻辑电路的输入和输出端口都增加一个寄存器,通过将这些I/O上的寄存器连接起来,可以将数据串行输入被测单元,并且从相应端口串行读出。

首先是芯片级测试,即可以对芯片本身进行测试和调试,使芯片工作在正常功能模式,通过输入端输入测试矢量,并通过观察串行移位的输出响应进行调试。

其次是板级测试,检测集成电路和PCB之间的互连。实现原理是将一块PCB上所有具有边界扫描的IC中的扫描寄存器连接在一起,通过一定的测试矢量,可以发现元件是否丢失或者摆放错误,同时可以检测引脚的开路和短路故障。

最后是系统级测试,在板级集成后,可以通过对板上CPLD或者Flash的在线编程,实现系统级测试。

板级芯片的互连测试

TAP控制器

TAP控制器的作用是将串行输入的TMS信号进行译码,使边界扫描系统进入相应的测试模式,并且产生该模式下所需的各个控制信号。

边界扫描寄存器

边界扫描寄存器

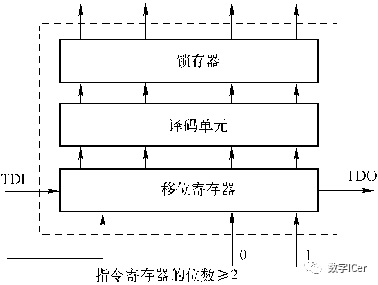

指令寄存器

指令寄存器由移位寄存器和锁存器组成,长度等于指令的长度。IR可以连接在TDI和TDO的两端,经TDI串行输入指令,并且送入锁存器,保存当前指令。

在这两部分中有个译码单元,负责识别当前指令。由于JTAG有3个强制指令,所以该寄存器的宽度至少为2位。

边界扫描测试策略

利用边界扫描IEEE 1149.1进行板级测试的策略分以下3步。

根据IEEE 1149.1标准建立边界扫描的测试结构

利用边界扫描测试结构,对被测部分之间的连接进行矢量输入和响应分析。这是板级测试的主要环节,也是边界扫描结构的主要应用。可以用来检测由于电气、机械和温度导致的板级集成故障

对单个核心逻辑进行测试,可以初始化该逻辑并且利用其本身的测试结构。

逻辑单元BIST

Logic BIST是SoC设计中芯片可测性设计的发展方向。

大多数的ASIC使用基于扫描的DFT技术。对于规模越来越大的芯片来说,扫描测试的策略面临着巨大的挑战。

整体DFT实现及性能上考虑

尽量避免异步时钟设计;

限制不同时钟域的数量;

对于多时钟域的设计,处于同一时钟域的触发器最好连在同一根扫描链上;

注意扇出比较多的端口,如scan_enable信号,尤其在综合的时候需要特别注意;

对于存储器、模拟电路等不可综合的逻辑加入适当的隔离旁路结构;

避免过长的扫描链;

考虑到测试模式下功耗过高所造成的问题,可将扫描测试分成数个部分,分开进行插入,在不同的扫描测试模式下,测试不同的部分;

尽量减少额外逻辑带来的面积、功耗的增大;

通过复用外围引脚,减少扫描测试对引脚的要求。

扫描设计流程

审核编辑 :李倩

-

芯片测试覆盖率99%就够了吗?给DFT设计提个醒2026-02-06 1226

-

DFT和BIST在SoC设计中的应用2011-12-15 6784

-

dft可测试性设计2021-07-22 1318

-

PADS DFT审核确保设计的可测试性2019-05-21 4270

-

DFT基本原理解析2020-07-06 10707

全部0条评论

快来发表一下你的评论吧 !