一个典型设计的DFT组件

描述

现代设计规模庞大,而且非常复杂。事实上,许多 SOC比几年前的完整子系统都要复杂。设计团队面临一个艰巨的挑战,如何在紧张的设计进度内开发完整的设计。半导体开发团队采用全面的并行设计方法来分割和并行开展大规模的开发工作。就半导体测试而言,传统的DFT 策略考虑的是整体器件。而现在,这种可能已经不复存在了。现代 SoC 的 DFT 需要有方法能够借助即插即用原则和自动化来解决设计规模扩大的问题。

DFT 团队越来越频繁地发现,由于经常需要等待部分设计的完成,自己会处在流片阶段的关键路径中。这些额外的流片进度风险源于管理数百个模块内的 DFT 逻辑所需的大量(多达上千个)DFT 集成步骤。要想获得任何成功的机会,采用完善定义的基础结构和自动化的 DFT方法是至关重要的。要增强这些步骤的可靠性并消除修正 DFT 集成步骤所需的难以逾越的迭代数量,自动化极其重要,否则这些集成步骤可能让项目进度完全失控。

在本篇白皮书中,我们介绍了一个典型设计的 DFT 组件,并提出了多种可大幅改善 DFT 项目进度的智能 DFT 方法。我们展示了如何将结构化 DFT 和即插即用原则用于 DFT 基础结构,来支持与其他设计开发工作相似的并行 DFT 开发和集成。自动化用于连接和管理 DFT 基础结构,以大幅降低风险,使许多必要的流程步骤都能成功运行。设计规模的持续扩大,给设计和测试团队增加了新的挑战。这里介绍的 DFT 方法旨在通过即插即用原则和自动化,来解决持续的设计规模扩大问题。

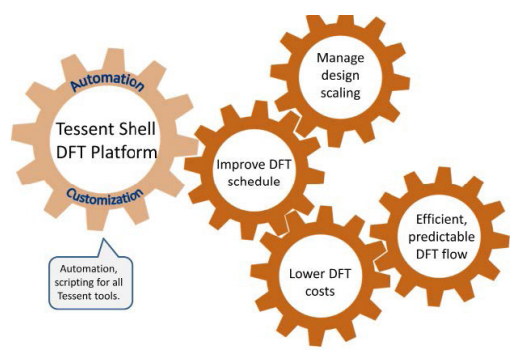

图1:DFT自动化与Tessent Shell DFT平台相结合,降低了风险并提高了DFT流程的可预测性。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DFT在信号处理中的应用 DFT与FFT的区别2024-12-20 4226

-

fft和dft的区别联系2023-09-07 9235

-

解析什么是DFT友好的功能ECO?2023-05-05 2873

-

什么是DFT友好的功能ECO呢?2023-03-06 3401

-

请问DFT是什么原理?2021-06-17 1578

-

请教一个关于fft算法的问题,DFT算法与FFT算法在应用上有什么区别?2016-06-02 4036

-

请问一个关于DFT的问题,跪求啊2013-05-30 2377

-

如何在labview中实现二维DFT?2012-06-27 3573

-

DFT和BIST在SoC设计中的应用2011-12-15 6666

-

DFT的快速算法-FFT2011-09-07 1364

-

什么是DFT,DFT是什么意思2010-06-07 31551

-

DFT性质一览表2009-07-25 4347

全部0条评论

快来发表一下你的评论吧 !