了解FPGA比特流结构

可编程逻辑

描述

比特流是一个常用词汇,用于描述包含FPGA完整内部配置状态的文件,包括布线、逻辑资源和IO设置。大多数现代FPGA都是基于SRAM的,包括Xilinx Spartan 和Virtex 系列。在FPGA上电或随后的FPGA重新配置期间,比特流从外部诸如闪存这样的非易失性存储器中读取,通过FPGA配置控制器的处理,加载到内部的配置SRAM中。

在有些情况下,设计者需要很好地了解FPGA比特流的内部结构。例如,使用FPGA物理实现工具的参数不能访问自定义的低级比特流、实现复杂的配置回溯方案、通过内部配置端口(ICAP)产生用于FPGA重新配置的短命令序列、读配置状态等。

比特流格式

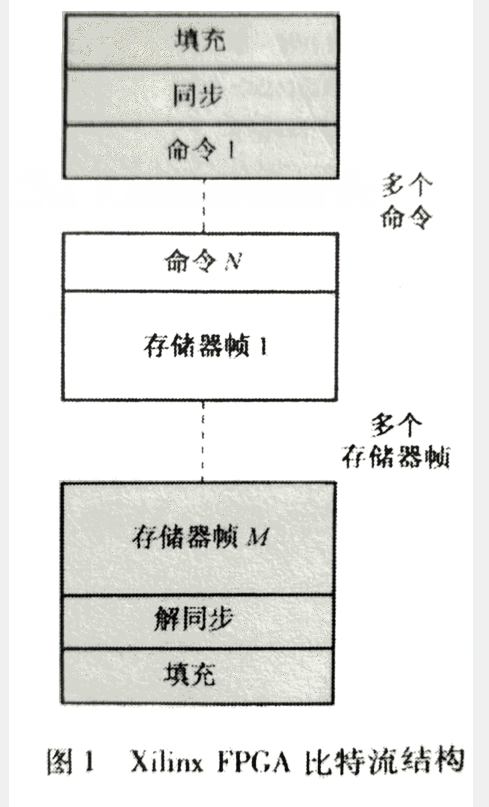

Xilinx FPGA的比特流结构如图1所示。

比特流包括以下组成部分:填充、同步字、用于访问配置寄存器的命令、存储器帧和解同步字。

填充

填充的数据是全0或全1序列,被FPGA配置控制器忽略。填充数据用于非易失性存储器中分离比特流。一般使用全 1填充较为方便,因为执行擦除后闪存的状态也是全1。

同步字

同步字是一个特殊值(0xAA995566), 通知FPGA配置控制器处理后续的比特流数据。

解同步字

解同步字通知FPGA配置控制器比特流的末端位置。解同步字之后,所有的比特流数据被忽略,直到遇到下一个同步字。

命令

命令用于读和写FPGA配置控制器寄存器。每个比特流中出现的一些命令, 有的是ID-CODE,用于标识比特流属于哪个FPGA器件。帧地址寄存器(FAR)、帧数据寄存器(FDRI)和无操作( NOOP)将被忽略。

存储器帧

存储器帧是配置Xilinx FPGA的比特流基本单元。帧的大小与具体的PPGA系列有关,系列不同,帧的大小也不同。Virtex-6 器件的帧有2592位。每个Virtex-6 器件具有的帧数不同,从最小7491(对于LX7ST)到最大5ss 548(对于LX550T)。帧用于多个逻辑片、I0、

BRAM及其他FPGA的配置。每帧都有一个地址,对应于FPGA配置空间的位置。比特流使用FAR和FDRI命令序列来配置帧。

Virtex-6 FPGA配置用户指南包含足够的关于比特流和访向FPGA配置控制器寄存器命令的文档。然而,关于存储器帧的详细文档不仅对于Xilinx FPGA无法获得,而且对于其他供应商的FPGA也是如此。

Xilinx的BITGEN实用程序

BITGEN是Xilinx的实用程序,利用本地电路描述( NCD)格式的布局布线后文件,创建用于FPGA配置的比特流。BITGEN 是一个高度可配置的工具,具有100多个命令行选项(在命令行工具用户指南2中描述)。有些选项用于确定比特流输出格式、启用压缩处理减少比特流大小、提高FPGA配置速度、使用CRC来确保数据完整性、对比特流加密等。

示例

以下示例用于根据差异部分配置的短比特流,通过脚本语言描述比特流命令。脚本采用Perl编写,在配套的网站上提供。

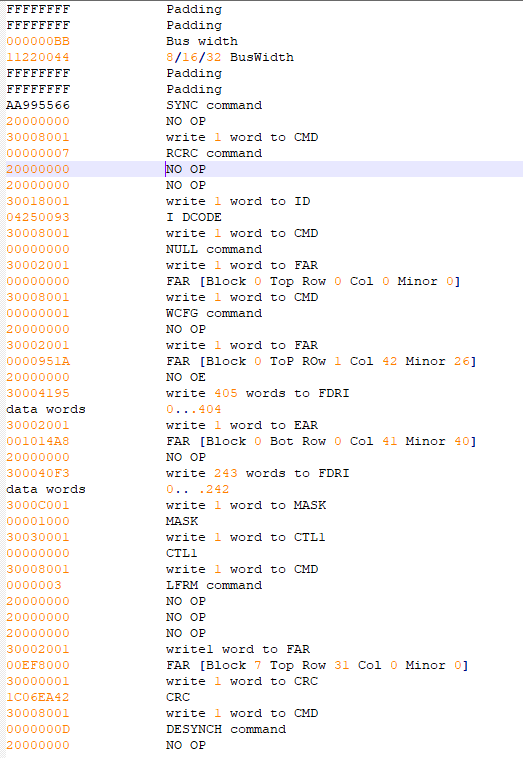

仔细观察比特流,能区分出同步和解同步命令、属于Virtex.6 LX240T PPGA的IDCODE,以及两个405个和243个字的帧。

-

DAC1280 TDATA引脚输入的比特流,怎么产生这个比特流,算法是什么?2025-01-06 447

-

一文了解FPGA比特流的内部结构2024-07-16 22652

-

使用加密保护7系列FPGA比特流2023-09-13 453

-

在artix7上使用ICAP进行部分比特流编程问题的解决办法?2020-08-06 2242

-

是否需要在flash上切换黄金比特流和多重比特流的位置?2020-06-09 2479

-

如何使用Vivado生成特定的部分比特流2020-05-05 3980

-

怎么在Virtex-7 FPGA上下载比特流?2020-04-02 1858

-

比特流是什么2019-08-23 5412

-

怎么在我的比特流中攻击BRAM2019-03-19 2945

-

中途向ICAP中止写入部分比特流2019-02-14 1855

-

如何使用IMPACT在FPGA xilinx中下载比特流2019-01-15 3408

-

无法生成比特流2018-11-09 3779

-

Zynq开发板FPGA比特流文件下载方式2017-02-08 1699

-

匹配位置对比特流随机性的影响研究2009-08-04 567

全部0条评论

快来发表一下你的评论吧 !