基于OpenAMP框架的双核ARM通信案例

移动通信

描述

ZYNQ 是赛灵思公司(Xilinx)推出的新一代全可编程片上系统(APSoC),它将处理器的软件可编程性与 FPGA 的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。

前言:

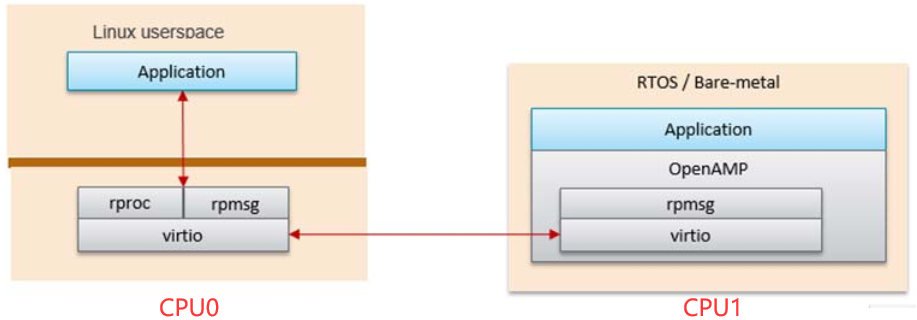

本文主要介绍基于OpenAMP框架的双核ARM通信案例的使用说明,CPU0(Master)运行Linux系统,CPU1(Remote)运行裸机或FreeRTOS程序。CPU0使用remoteproc加载CPU1程序,并对CPU1进行配置。

图 1

OpenAMP详细开发说明可查阅官方文档:

https://china.xilinx.com/content/dam/xilinx/support/documentation/sw_manuals/xilinx2021_2/ug1186-zynq-openamp-gsg.pdf。

本文基于创龙科技 Xilinx Zynq-7010/7020平台进行案例测试。

图 2

echo_test案例

1.1 案例功能

案例功能:CPU0使用RPMsg向CPU1发送数据,CPU1接收到数据后再使用RPMsg向CPU0回传数据。CPU0对回传的数据进行验证,并输出验证结果。

1.2 操作说明

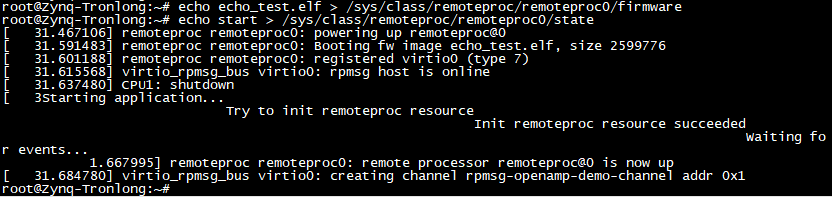

将CPU1裸机或FreeRTOS可执行文件复制到评估板文件系统“/lib/firmware/”目录下,并执行如下命令加载CPU1程序。

Target# echo echo_test.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

图 3

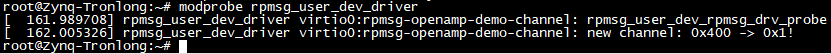

执行如下命令加载RPMsg驱动,并在“/dev/”目录下生成RPMsg设备节点。

Target# modprobe rpmsg_user_dev_driver

图 4

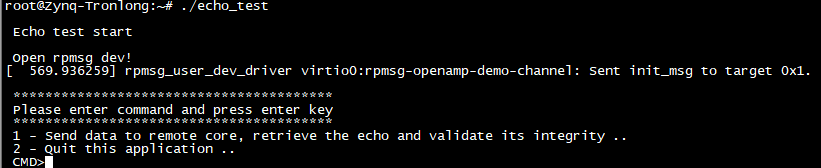

将CPU0应用程序可执行文件复制到评估板文件系统,并执行如下命令通过RPMsg与CPU1进行通信。

Target# ./echo_test

图 5

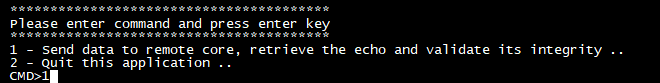

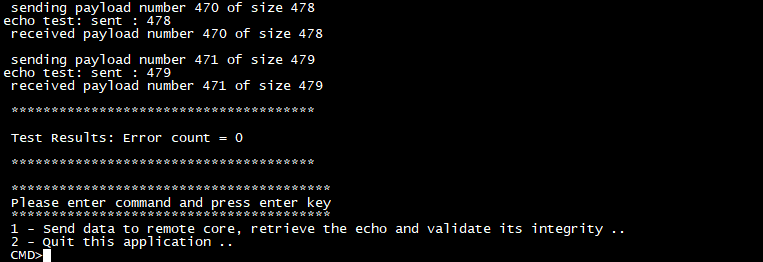

输入1,并按回车键进行测试。

图 6

图 7

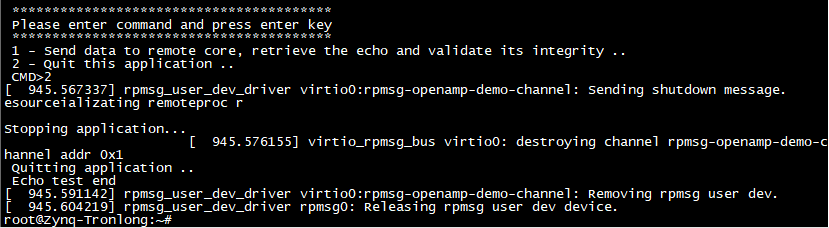

输入2,并按回车键退出测试。

图 8

执行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

图 9

2 1

matrix_multiply案例

2.1 案例功能

案例功能:CPU0随机生成两个矩阵并使用RPMsg向CPU1发送数据,CPU1接收到数据后进行矩阵乘法运算,再使用RPMsg向CPU0回传运算结果,然后CPU0通过串口终端输出运算结果。

2.2 操作说明

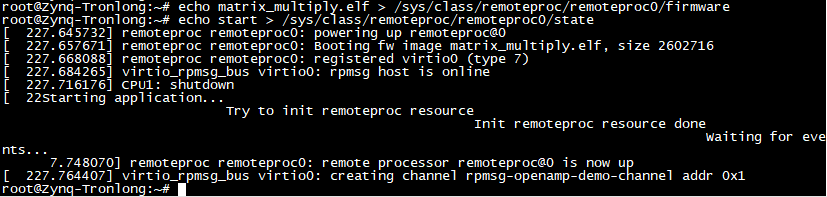

将CPU1裸机或FreeRTOS可执行文件复制到评估板文件系统“/lib/firmware/”目录下,并执行如下命令加载CPU1程序。

Target# echo matrix_multiply.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

图 10

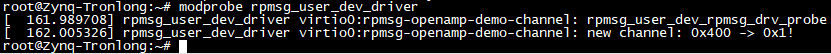

执行如下命令加载RPMsg驱动,并在“/dev/”目录下生成RPMsg设备节点。

Target# modprobe rpmsg_user_dev_driver

图 11

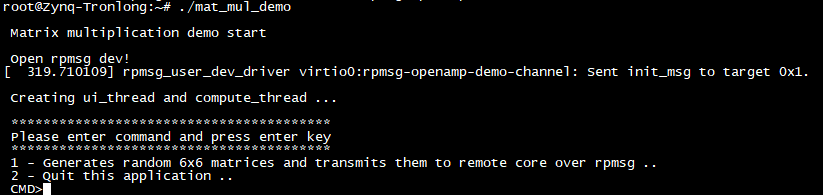

将CPU0应用程序可执行文件复制到评估板文件系统,并执行如下命令通过RPMsg与CPU1进行通信。

Target# ./mat_mul_demo

图 12

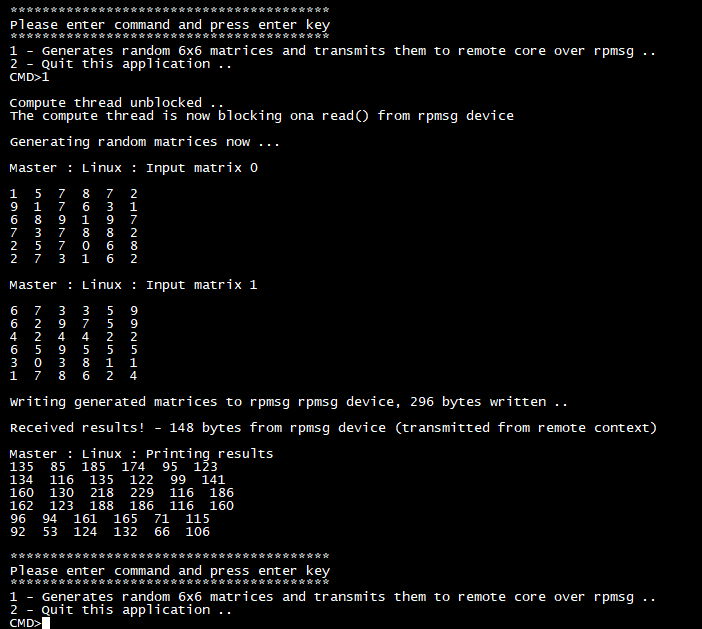

输入1,并按回车键进行测试。

图 13

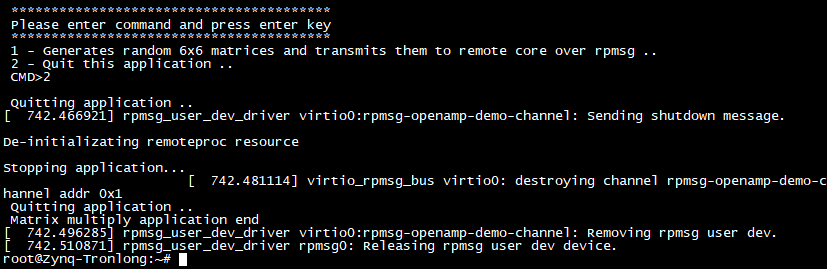

输入2,并按回车键退出测试。

图 14

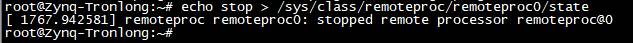

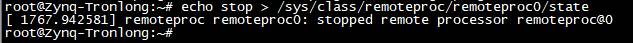

执行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

图 15

3 01

内存分配说明

512MByte DDR容量版本核心板的内存地址分配如下:

表 1

| 名称 | 地址范围 | 范围大小 |

| PS Linux | 0~0x17FF FFFF | 384MByte |

| PL MicroBlaze | 0x1800 0000~0x18FF FFFF | 16MByte |

| OpenAMP-remote app | 0x1900 0000~0x19FF FFFF | 16MByte |

| PL | 0x1A00 0000~0x1FFF FFFF | 96MByte |

1GByte DDR容量版本核心板的内存地址分配如下:

表 2

| 名称 | 地址范围 | 范围大小 |

| PS Linux | 0~0x17FF FFFF | 384MByte |

| PL MicroBlaze | 0x1800 0000~0x18FF FFFF | 16MByte |

| OpenAMP-remote app | 0x1900 0000~0x19FF FFFF | 16MByte |

| PL | 0x1A00 0000~0x1FFF FFFF | 96MByte |

| PS Linux | 0x2000 0000~0x3FFF FFFF | 512MByte |

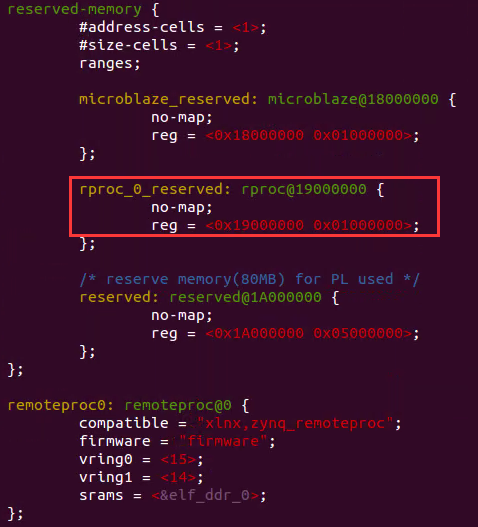

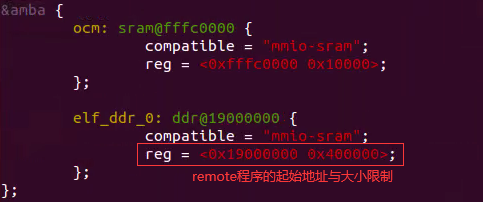

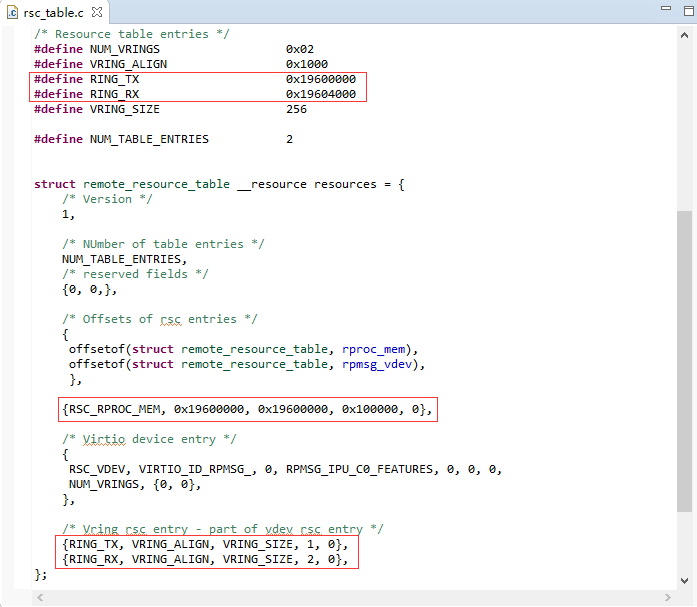

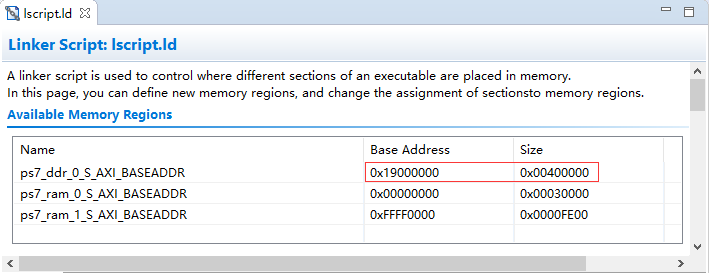

如需修改CPU1程序(OpenAMP-remote app)内存地址空间范围,可通过更改设备树文件tlz7x-easyevm-s.dts、资源表rsc_table.c及链接文件lscript.ld对内存地址空间进行重新分配。三者需同步修改并保持一致,以确保固件程序链接地址与设备树配置的elf_ddr_0对应。所使用的资源(内存和virtio设备资源)不能超出设备树文件配置的内存范围。

图 16设备树文件tlz7x-easyevm-s.dts配置

图 17设备树文件tlz7x-easyevm-s.dts配置

图 18 CPU1程序资源表rsc_table.c配置

图 19 CPU1程序链接文件lscript.ld配置

编辑:黄飞

-

用cubemx建立的工程描述说找不到Image$$__OpenAMP_SHMEM__$$Base怎么解决?2024-03-25 221

-

怎么在CCS上设计dsplink双核通信2016-12-02 4356

-

OMAPL138的双核通信组件DSPLINK开发和双核通信演示教程2018-06-21 2176

-

搞定单CPU内双核间的通信和双CPU间的通信2018-08-19 3378

-

怎么实现ARM/DSP双核系统的通信接口的设计?2021-05-26 1354

-

用于STM32H74xxx和STM32H75xxx双核OpenAMP应用STM32Cube的软件扩展2022-11-25 568

-

Arm+RISC-V双核异构前景如何?2023-04-14 1233

-

DSP/ARM双核系统的通信接口设计2009-12-21 2053

-

ARM与DSP双核系统中的通信接口设计_赵学亮2016-07-01 576

-

在OMAPL138的ARM核与DSP核上实现TL IPC双核通信开发2020-08-06 1937

-

ZYNQ OpenAMP双核ARM通信案例开发手册2021-07-06 1422

-

基于ARM7和DSP双核控制的逆变电源设计2021-09-22 956

-

ZYNQ双核ARM分别运行不同的操作系统(基于OpenAMP)2022-12-05 6758

-

Xilinx ZYNQ双核ARM通信开发实例2021-12-27 3606

-

分享!基于NXP i.MX 8M Plus平台的OpenAMP核间通信方案2025-02-27 1251

全部0条评论

快来发表一下你的评论吧 !