如何使用NXP的PLU配置工具

工业控制

描述

简介

本篇文章介绍如何使用NXP的PLU配置工具。 本篇文章来自How to use the PLU configuration tool - NXP Community,原作者soledad。 PLU是NXP的LPC804和LPC5500系列MCU具有的特殊外设,英文Programmable Logic即可编程逻辑单元,它相当于一个简单的FPGA,可以应付相对复杂一些的组合逻辑需求,具有灵活的输入输出用法。NXP提供的PLU的配置工具,可以让设计流程支持Verilog模式,示意图设计模式以及直接使用配置LUT的模式。 LPC80x 15 MHz|Arm Cortex-M0+|32-bit Microcontrollers (MCUs) | NXP Semiconductors LPC5500 Series: Arm Cortex-M33 based Microcontrollers for the general embedded market | NXP | NXP Semiconductors PLU 编程工具上位机软件有助于简化配置 和使用PLU的工作量 , 您可以从以下链接下载它: PLU配置工具下载链接

PLU配置工具可以接受实现的功能的 Verilog RTL 描述文件,输出提供以下功能: 注意:LUT是Lookup Table的缩写即查找表

生成可以配置到所有LUT INPUT MUX寄存器的数据

生成可以配置到所有LUT TRUTH寄存器的数据

生成可以配置到所有OUTPUT MUX寄存器的数据

出错告警使用者描述的逻辑网络不能生成(可能是由于过多的逻辑单元或者使用了四个以上的flip-flop触发器)

实际设计的时序参数

PLU配置工具仅连接LUTs到PLU的输入和输出,使用者仍然要通过软件配置SwitchMatrix的功能实现连接PLU的输入,输出以及PLU的clk_in到相应的物理引脚。

如何使用PLU配置工具

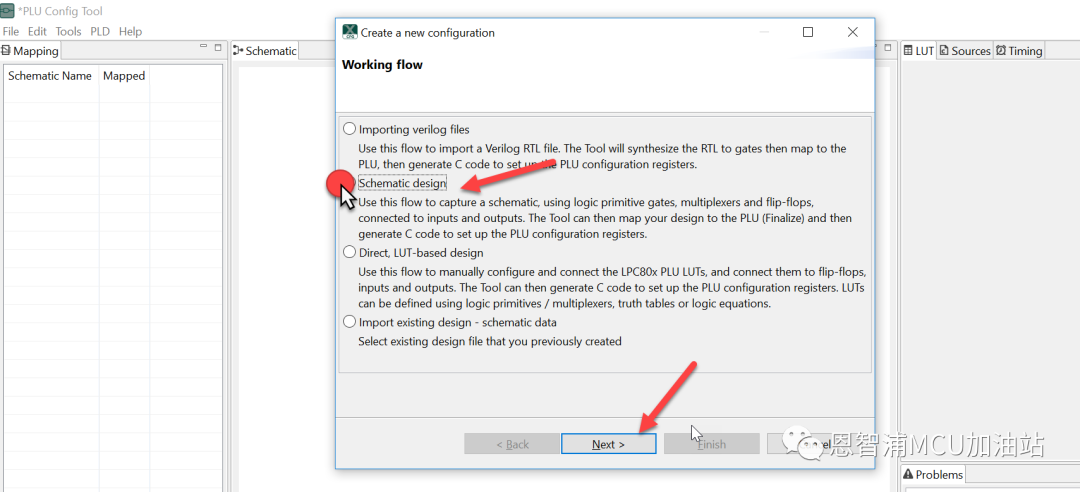

PLU配置工具有如下3种方式设计逻辑网络:

-- 导入Verilog文件

使用此流程可以导入Verilog RTL文件,PLU配置工具将RTL综合到门级并映射到PLU上,然后生成设置PLU寄存器的C代码。

-- 逻辑示意图设计

使用此流程可以设计逻辑示意图,使用连接到输入和输出的逻辑单元,多路复用器(MUX)和触发器(FF, flip-flop)。然后PLU配置工具可以把设计映射到PLU(Finalize),最后生成PLU寄存器配置的C代码。

-- 直观模式,基于LUT设计

使用者手动配置LPC80x的PLU LUT设置,并且手动配置到触发器,输入和输出。PLU工具可以协助产生配置PLU寄存器的C代码,LUT可以使用逻辑图元、多路复用器、真值表或者逻辑公式来定义。 使用者需要手动将LUT/门映射到PLU的输入/输出功能,最后由PLU配置工具产生设置PLU寄存器的C代码。

示意图设计

这种方式直接易用,设计过程直接使用标准逻辑门和多路复用器实现需求,也便于移植。缺点是很难准确的看到设计是如何映射到LUT硬件的(使用者应该设置寄存器来实现功能操作),同时和Verilog相比也很难实现状态机。 实现步骤如下: 1、打开PLU配置工具。 2、选择示意图设计(Schematic Design)并点击下一步(Next):

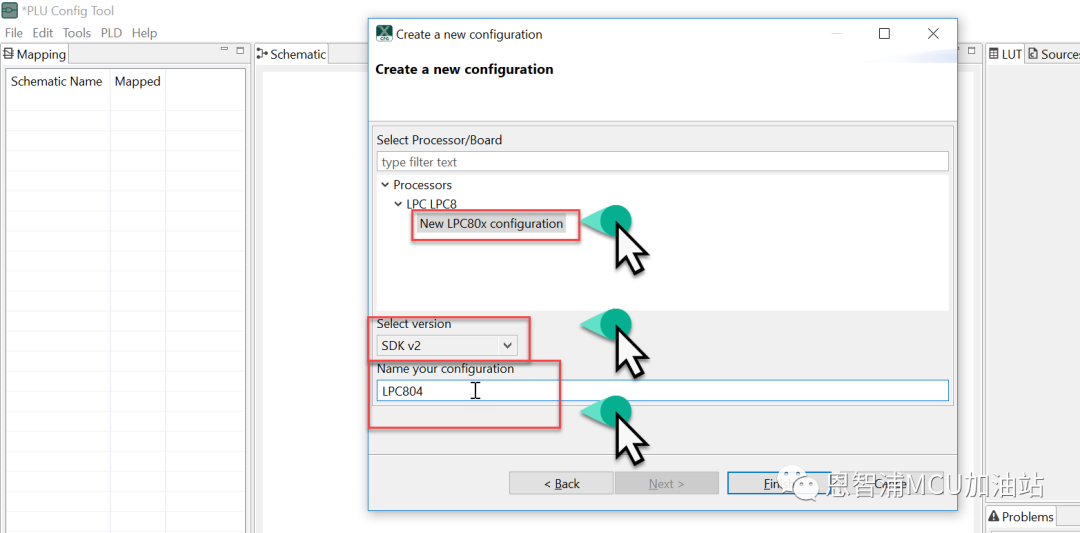

3、选择MCU,SDK的版本以及配置工程的名字,然后点击下一步(Next)结束:

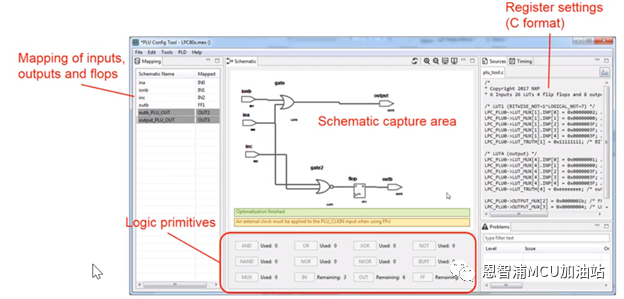

4、到此,你可以开始你的设计,你可以把逻辑门,多路复用器和触发器添加到你的示意图区域中。

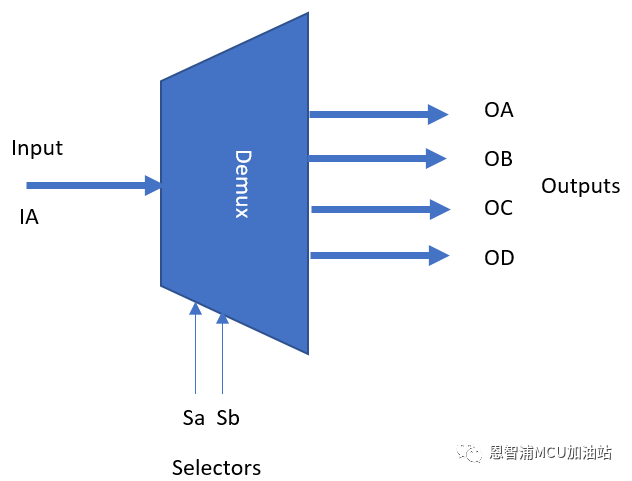

举个栗子,让我们来设计一个分用器(demultiplexer)。分用器需要1个单独的数据输入接口然后同一时间只能切换到任意一个独立的输出接口。

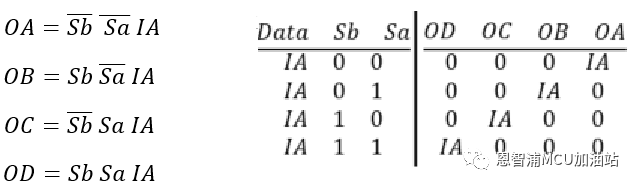

1到4的分用器的输出OA到OD以及数据线Sa和Sb关系的逻辑表达式以及真值表如下,

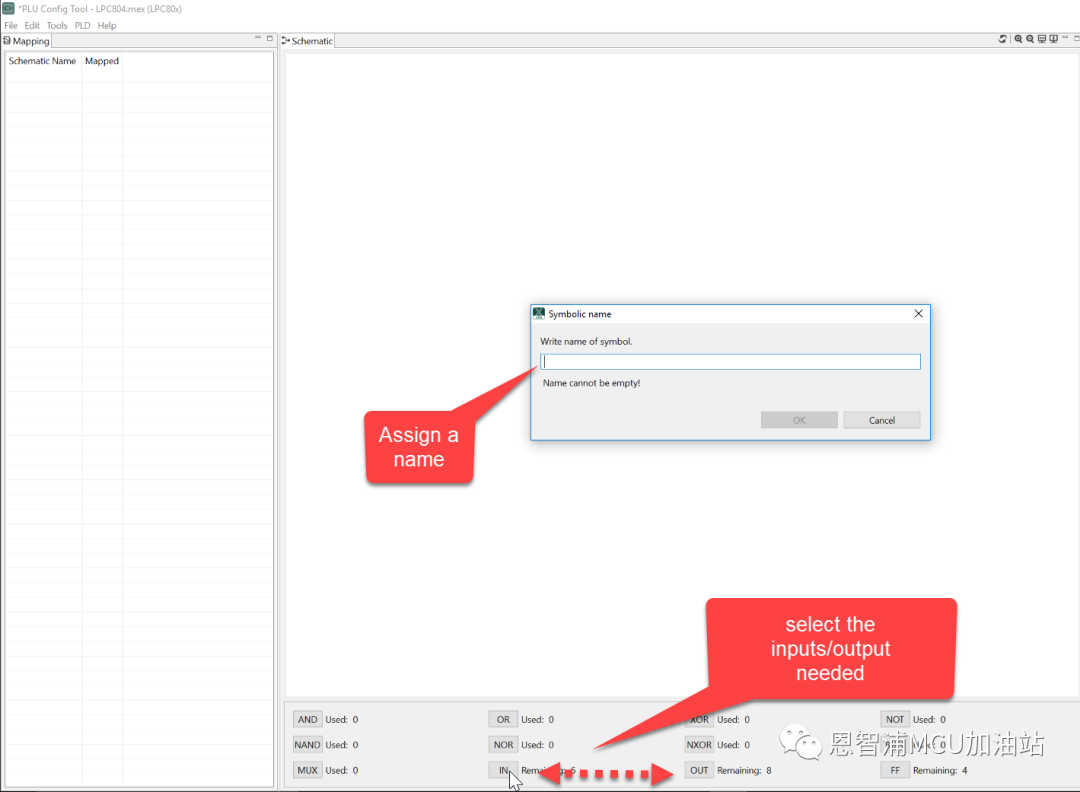

使用PLU配置工具,先选择所有需要用到的输入和输出信号并且为它们命名。

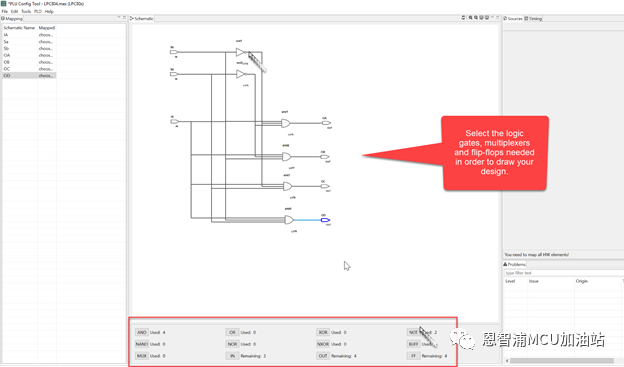

选择需要的逻辑功能门,复用器和触发器来实现你的设计。

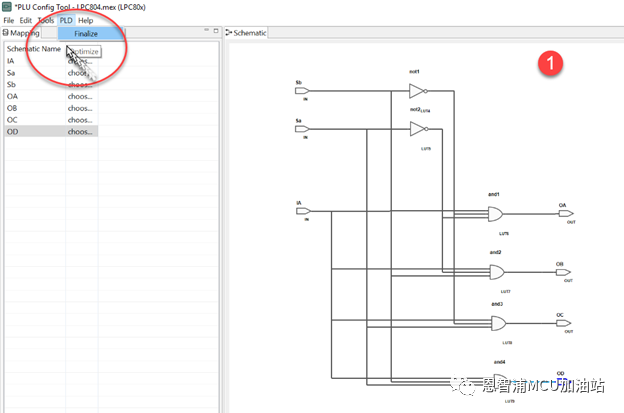

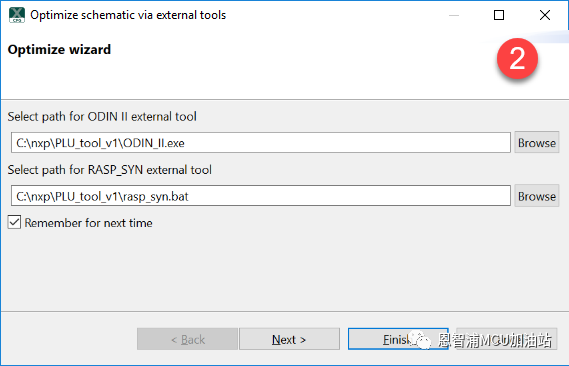

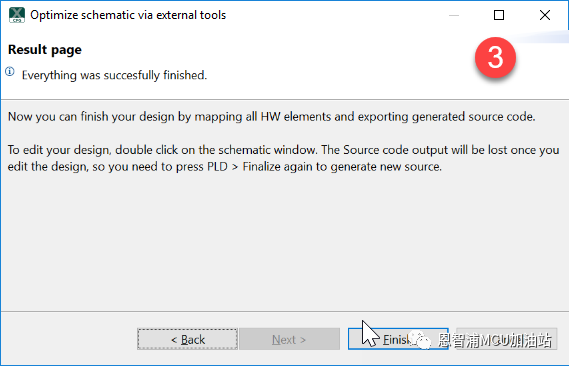

5、完成逻辑示意图设计后,需要点击“PLD->Finalize”实现综合设计。之后,配置工具显示一个新的窗口,其中包含有关优化的外部工具的位置信息,如果单击下一步(Next),将出现一个新的窗口,其中包含有关生成过程中已经成功的信息。

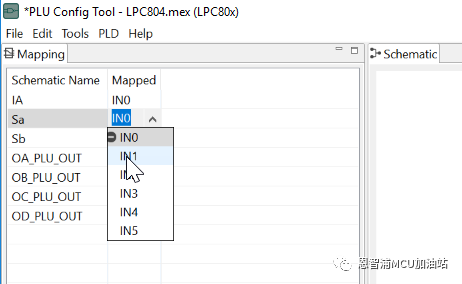

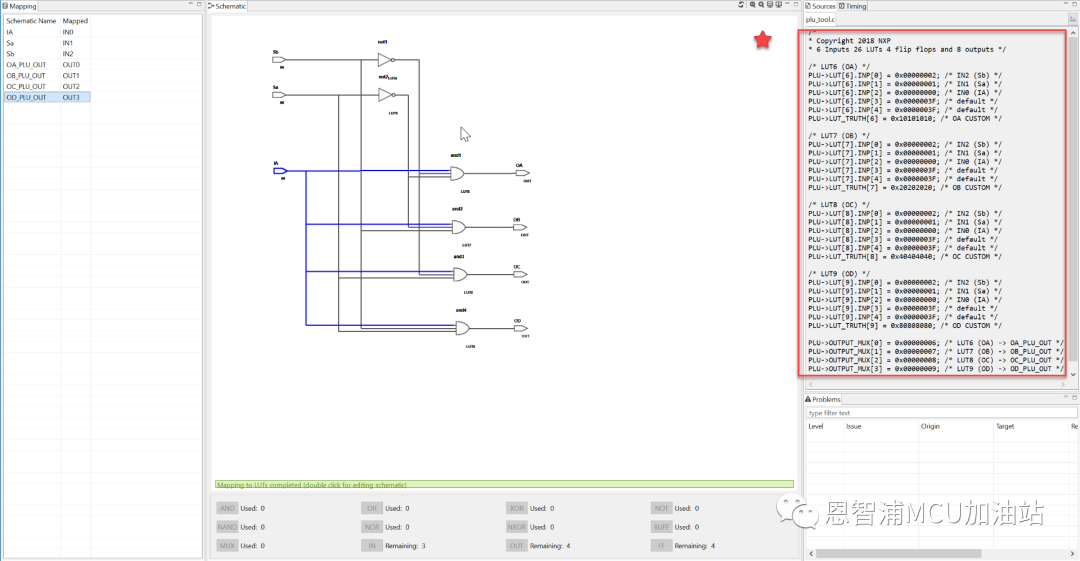

6、为了生成C代码,需要在映射区域中手动将LUT/逻辑门映射到PLU的输入/输出。

指定连接后,C代码将自动出现在代码区域中。

复制并粘贴C代码到你的LPC80x的工程中,需要注意的是PLU配置工具仅将LUT连接到PLU的输入后和输出,用户仍然需要通过软件中的SWM将PLU输入、输出、PLU clk_in连接到物理引脚。

编辑:黄飞

-

NXP遥控机械臂还没吃饭 2023-06-24

-

NXP在线引脚配置工具使用说明V1.00.pdf2016-09-19 3539

-

NXP在线引脚配置工具使用说明V1.002016-09-21 4825

-

【NXP LPC54110试用体验】2.MCUXpresso配置工具简单介绍2017-10-14 10785

-

请问NXP在线调试工具FreeMaster怎么使用?2021-10-11 1769

-

如何开启NXP-MCUBootUtility工具的HAB签名功能?2022-02-28 1370

-

MCUXpresso PLU LPC55原理图错误是怎么回事?2023-03-23 600

-

如何在项目之间共享PLU原理图?2023-03-30 739

-

NXP codewarrior开发工具2016-12-23 1461

-

NXP无人机开发套件及工具2017-02-10 1588

-

NXP毫米波雷达开发工具2017-03-03 1155

-

NXP(恩智浦)V2X通信软件和工具2017-03-10 1522

-

NXP新能源汽车BMS开发套件及工具2017-03-24 2053

-

雷达前沿配置工具2021-03-23 569

-

MCUXpresso配置工具快速入门指南2022-12-19 733

全部0条评论

快来发表一下你的评论吧 !