可创建小型组合与时序逻辑电路的PLU可编程逻辑单元

描述

在进行MCU开发时,有时需要用到一些简单的数字逻辑电路,LPC804与LPC55XX系列集成了PLU(Programmable Logic Unit),即可编程逻辑单元,可创建小型组合与时序逻辑电路,降低成本。

有些客户在使用PLU时,对PLU的概念以及使用方法有些许疑问,本文对此进行讲解。

1、PLU简介

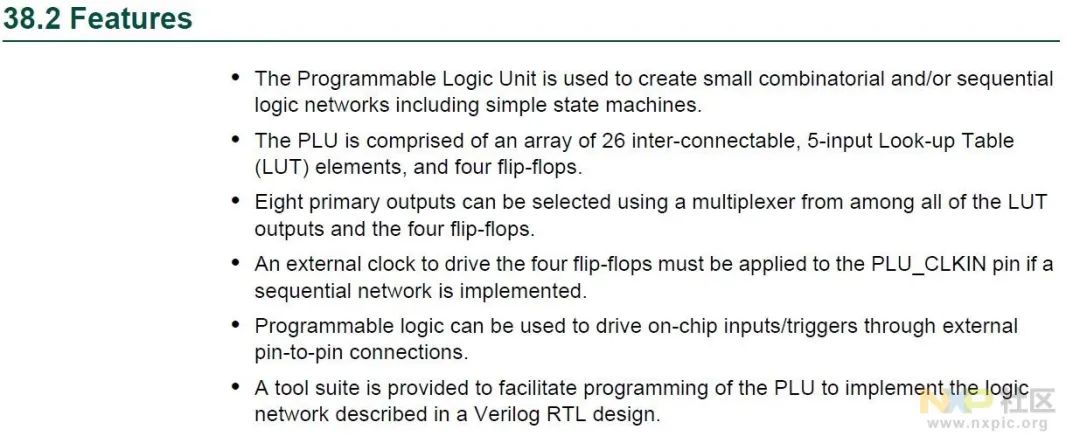

LPC804与LPC55XX的PLU在使用上是完全相同的。包含了6个输入、8个输出、26个5输入查找表(LUT)、4个触发器(state Flip-Flops),其中26个PLU是相互连接的,输出与查找表、触发器之间采用多路复用,如下:

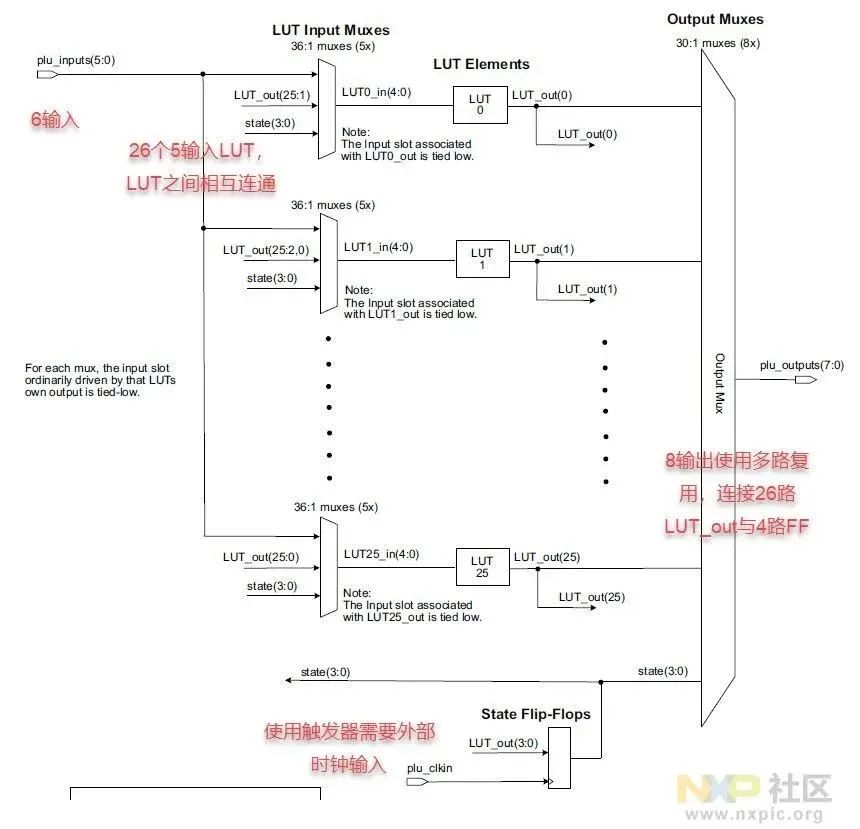

数字逻辑电路分为组合逻辑电路与时序逻辑电路,只有时序逻辑电路需要使用触发器。当使用触发器时,需要外部向PLU_CLKIN提供时钟输入,即使用组合逻辑电路无需外部提供时钟,使用时序逻辑电路时需要外部时钟。如下:

2、PLU配置

测试最简单的组合逻辑电路与时序逻辑电路,如下:

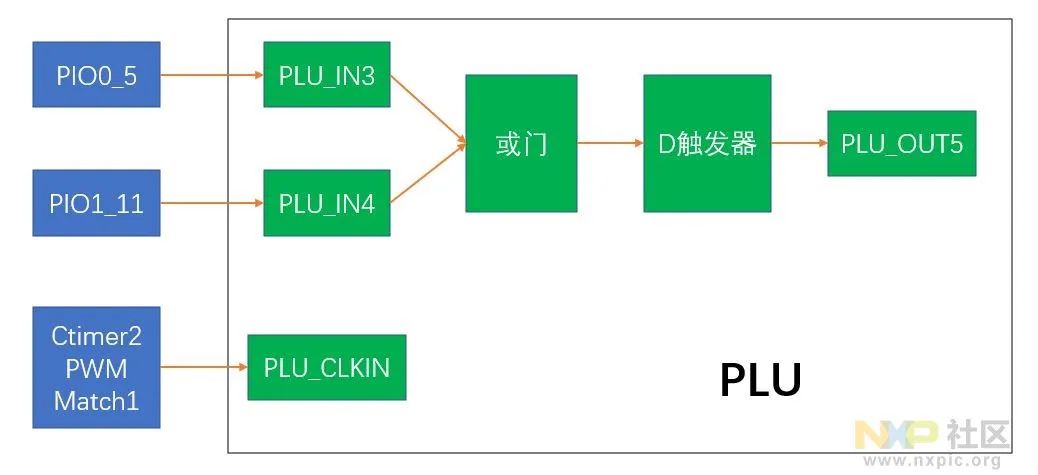

根据LPC55S69-EVK引出的引脚,如下:

配置引脚,如下:

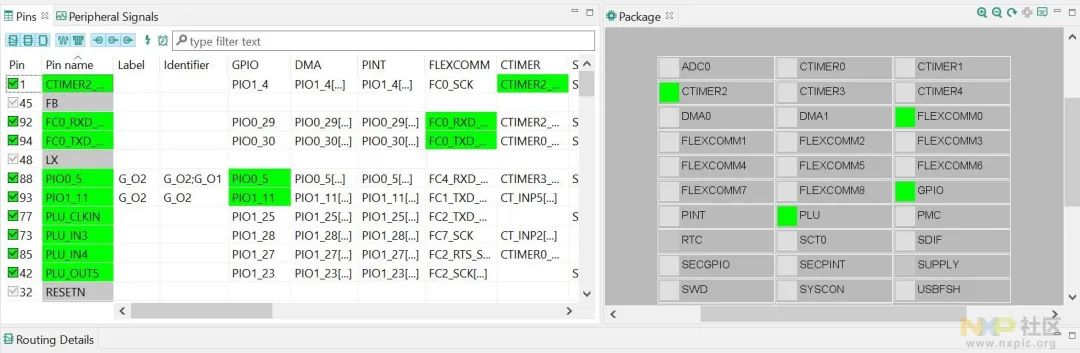

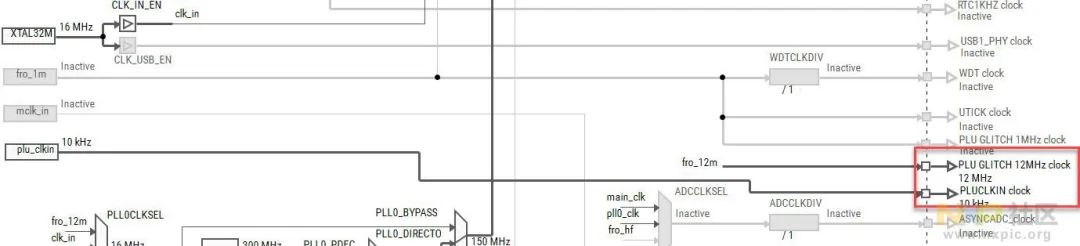

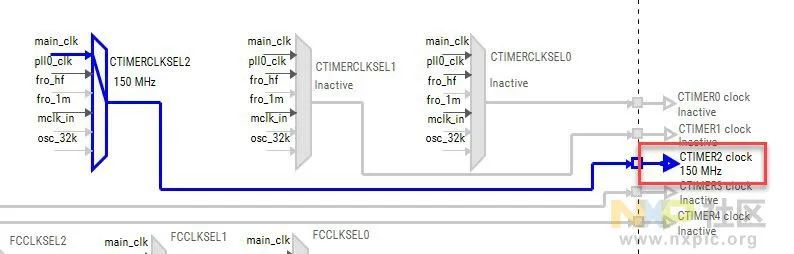

配置时钟,PLU的CLKIN时钟设置为10K输入,如下:

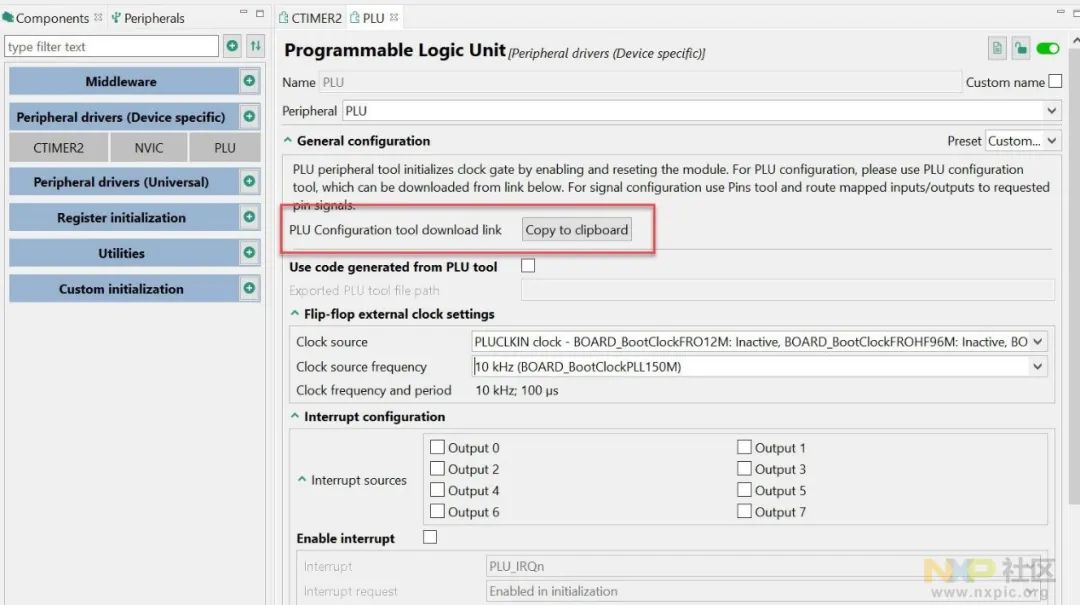

配置PLU外设,如下:

配置PWM外设,设置PWM为50%占空比,10K频率,如下:

3、PLU Configuration tool 配置

NXP开发了PLU Configuration tool,此工具可以根据数字逻辑电路生成对应代码,去配置PLU及其真值表,下载链接可以在PLU外设配置界面复制,链接如下:

https://www.nxp.com/mcu-plu-config-tool

3.1 原理图配置

打开PLU配置工具,选择原理图设计,做一个简单的或运算与D触发器实验,如下:

点击菜单栏File-》Export-》PLU source file将其导出为C文件,将C文件的内容复制到main函数中,如下:

/* LUT0 (or01) */

PLU->LUT[0].INP_MUX[0] = 0x00000003; /* IN3 (IN3) */

PLU->LUT[0].INP_MUX[1] = 0x00000004; /* IN4 (IN4) */

PLU->LUT[0].INP_MUX[2] = 0x0000003F; /* default */

PLU->LUT[0].INP_MUX[3] = 0x0000003F; /* default */

PLU->LUT[0].INP_MUX[4] = 0x0000003F; /* default */

PLU->LUT_TRUTH[0] = 0xeeeeeeee; /* or01 (or01) STD 2 INPUT OR */

PLU->OUTPUT_MUX[5] = 0x0000001a; /* FF0 (FF01) -> OUT5 */

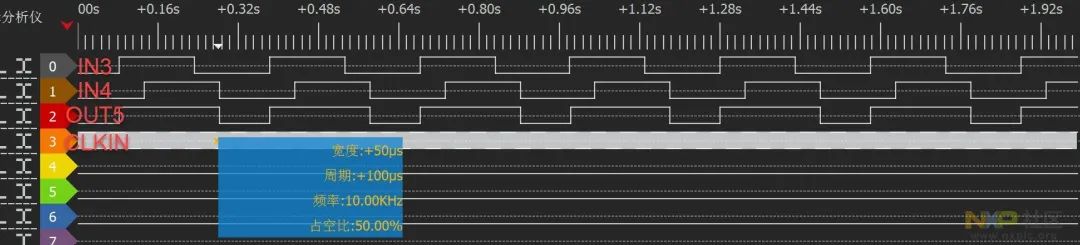

逻辑分析仪检测结果如下:

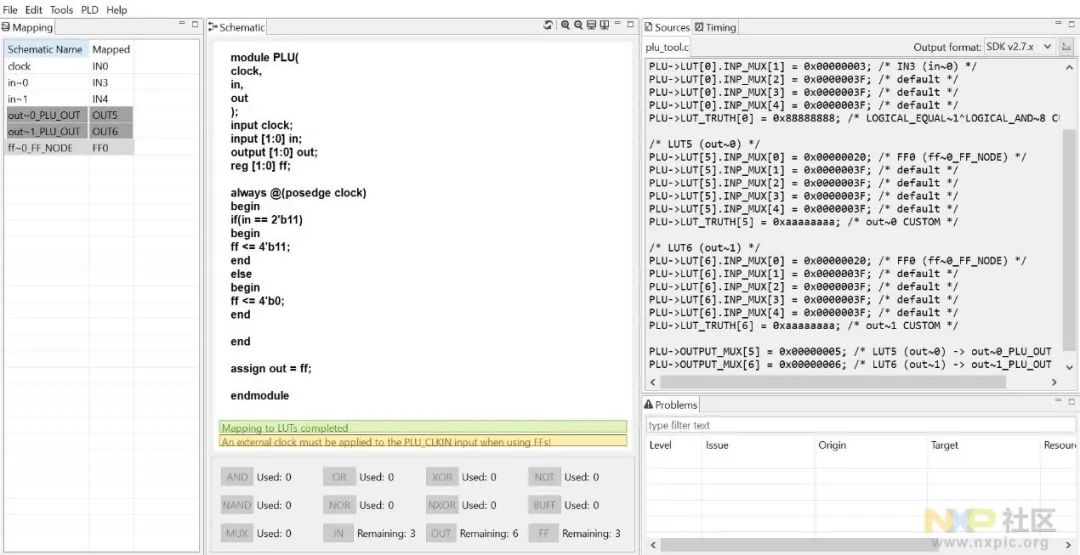

3.2 Verilog配置

打开PLU配置工具,选择导入verilog文件,将写好的.v文件导入,做一个简单的与运算实验,如下:

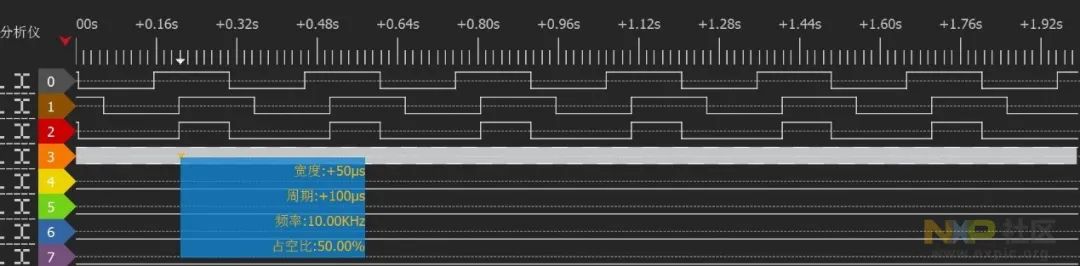

注意只有在verilog文件中声明posedge clock才会使用到触发器,而且不能使用negedge sys_rst_n用来复位。always语句中的posedge clock将由CLKIN引脚的时钟输入代替,所以clock引脚是不起作用的。将生成的代码复制到main函数中,用逻辑分析仪测试的结果如下:

审核编辑:郭婷

-

逻辑电路芯片-组合逻辑电路芯片-时序逻辑电路芯片2024-09-30 1047

-

时序逻辑电路有记忆功能吗2024-08-29 2143

-

什么是组合逻辑电路和时序逻辑电路?它们之间的区别是什么2024-03-26 6473

-

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别2024-02-06 13447

-

组合逻辑电路和时序逻辑电路的区别和联系2023-03-14 8537

-

时序逻辑电路设计2019-05-16 8962

-

什么是时序逻辑电路2019-02-26 32710

-

组合逻辑电路实验原理2018-01-30 67721

-

什么是组合逻辑电路,组合逻辑电路的基本特点和种类详解2017-05-22 76972

-

时序逻辑电路概述2010-08-12 796

-

时序逻辑电路2010-08-10 876

-

时序逻辑电路的设计实验2009-03-18 2036

全部0条评论

快来发表一下你的评论吧 !