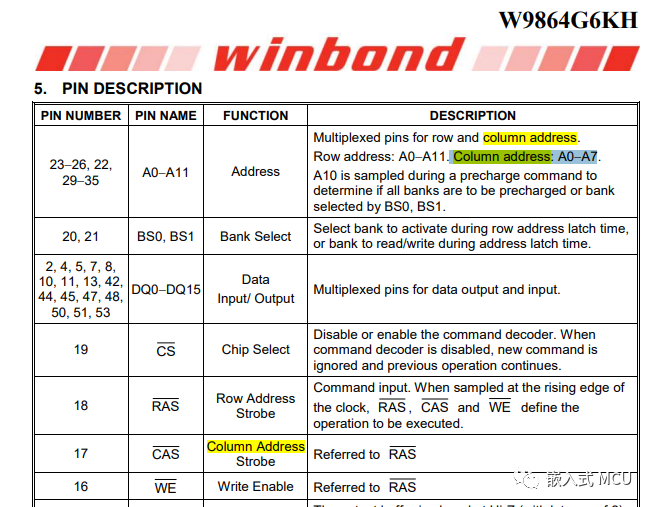

MIMXRT1176支持8位列地址的SDRAM器件W9864G6

电子说

描述

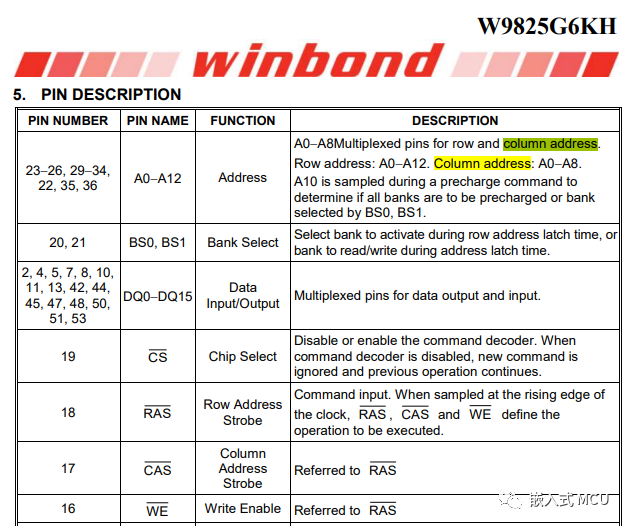

MIMXRT1176的开发板配套的 SDRAM是W9825G6KH,对应的列地址是9位的。

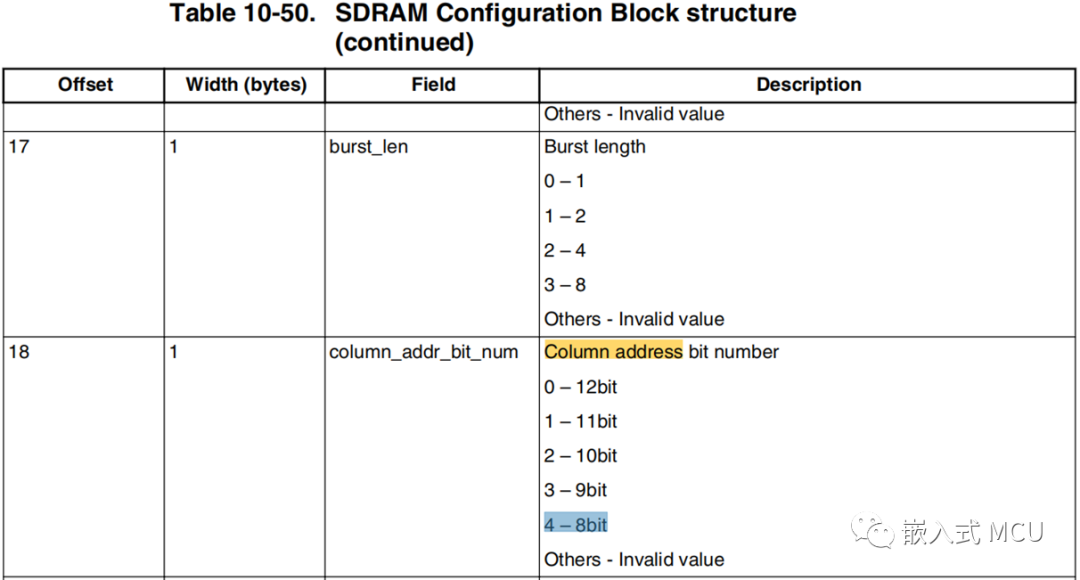

MIMXRT1176支持的列地址是 8/9/10/11/12位。

SDRAM 替换成 W9864G6后,Column地址变为 8位的。

SDK中例程目录 evkmimxrt1170driver_examplessemcsdramcm7,修改semc_sdram.c文件配置如下。

status_t BOARD_InitSEMC(void)

{

semc_config_t config;

semc_sdram_config_t sdramconfig;

uint32_t clockFrq = EXAMPLE_SEMC_CLK_FREQ;

/* Initializes the MAC configure structure to zero. */

memset(&config, 0, sizeof(semc_config_t));

memset(&sdramconfig, 0, sizeof(semc_sdram_config_t));

/* Initialize SEMC. */

SEMC_GetDefaultConfig(&config);

config.dqsMode = kSEMC_Loopbackdqspad; /* For more accurate timing. */

SEMC_Init(SEMC, &config);

/* Configure SDRAM. */

sdramconfig.csxPinMux = kSEMC_MUXCSX0;

sdramconfig.address = 0x80000000;

sdramconfig.memsize_kbytes = 1 * 8 * 1024; /* 8MB*/

sdramconfig.portSize = kSEMC_PortSize16Bit;

sdramconfig.burstLen = kSEMC_Sdram_BurstLen8;

sdramconfig.columnAddrBitNum = kSEMC_SdramColunm_8bit;

sdramconfig.casLatency = kSEMC_LatencyThree;

sdramconfig.tPrecharge2Act_Ns = 15; /* tRP 15ns */

sdramconfig.tAct2ReadWrite_Ns = 15; /* tRCD 15ns */

sdramconfig.tRefreshRecovery_Ns = 70; /* Use the maximum of the (Trfc , Txsr). */

sdramconfig.tWriteRecovery_Ns = 2; /* tWR 2ns */

sdramconfig.tCkeOff_Ns =

42; /* The minimum cycle of SDRAM CLK off state. CKE is off in self refresh at a minimum period tRAS.*/

sdramconfig.tAct2Prechage_Ns = 40; /* tRAS 40ns */

sdramconfig.tSelfRefRecovery_Ns = 70;

sdramconfig.tRefresh2Refresh_Ns = 60;

sdramconfig.tAct2Act_Ns = 2; /* tRC/tRDD 2ns */

sdramconfig.tPrescalePeriod_Ns = 160 * (1000000000 / clockFrq);

sdramconfig.refreshPeriod_nsPerRow = 64 * 1000000 / 8192; /* 64ms/8192 */

sdramconfig.refreshUrgThreshold = sdramconfig.refreshPeriod_nsPerRow;

sdramconfig.refreshBurstLen = 1;

sdramconfig.delayChain = 6; /* For all tempeatures. */

return SEMC_ConfigureSDRAM(SEMC, kSEMC_SDRAM_CS0, &sdramconfig, clockFrq);

}

static void SEMC_SDRAMReadWrite8Bit(void)

{

uint32_t index;

uint32_t datalen = SEMC_EXAMPLE_DATALEN;

uint8_t *sdram = (uint8_t *)EXAMPLE_SEMC_START_ADDRESS; /* SDRAM start address. */

bool result = true;

PRINTF(" SEMC SDRAM Memory 8 bit Write Start, Start Address 0x%x, Data Length %d ! ", sdram, datalen);

memset(sdram_writeBuffer, 0, sizeof(sdram_writeBuffer));

memset(sdram_readBuffer, 0, sizeof(sdram_readBuffer));

/* Prepare data and write to SDRAM. */

for (index = 0; index < datalen; index++)

{

sdram_writeBuffer[index] = index % 0x100;

sdram[index] = sdram_writeBuffer[index];

}

PRINTF(" SEMC SDRAM Read 8 bit Data Start, Start Address 0x%x, Data Length %d ! ", sdram, datalen);

#if defined(CACHE_MAINTAIN) && CACHE_MAINTAIN

DCACHE_InvalidateByRange(EXAMPLE_SEMC_START_ADDRESS, 4U * SEMC_EXAMPLE_DATALEN);

#endif

/* Read data from the SDRAM. */

for (index = 0; index < datalen; index++)

{

sdram_readBuffer[index] = sdram[index];

}

PRINTF(" SEMC SDRAM 8 bit Data Write and Read Compare Start! ");

/* Compare the two buffers. */

while (datalen--)

{

if (sdram_writeBuffer[datalen] != sdram_readBuffer[datalen])

{

result = false;

break;

}

}

if (!result)

{

PRINTF(" SEMC SDRAM 8 bit Data Write and Read Compare Failed! ");

}

else

{

PRINTF(" SEMC SDRAM 8 bit Data Write and Read Compare Succeed! ");

}

}

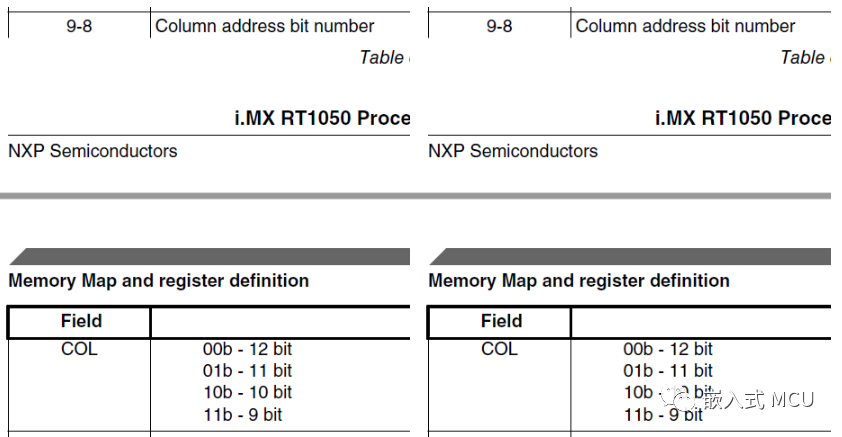

备注:在 MIMXRT1050 MCU 上只支持9/10/11/12位,不支持 8位的。

SDRAM 配置参考文档:

https://www.nxp.com.cn/docs/en/nxp/application-notes/AN12026.pdf

审核编辑 :李倩

-

w7支持proterDXP2004吗????2012-03-01 4403

-

请问6455支持对16位flash操作吗?2019-01-22 4259

-

使用ST的HAL库进行开发W9825G6KH-62021-08-04 1617

-

sdphost无法与mimxrt1176 bootrom对话是怎么回事?2023-03-28 639

-

为MIMXRT1176编程外部闪存时引导加载程序错误的原因?2023-04-06 728

-

是否可以用MIMXRT117H替换MIMXRT1176?2023-04-18 574

-

MIMXRT1175xxxxx是否像MIMXRT1176xxxxx一样支持多核启动?2023-04-25 621

-

从MIMXRT1176DVMAA更改为MIMXRT1176AVM8A时出现的问题怎么解决?2023-04-26 747

-

i.MXRT1024可以从A0配置8位SDRAM的地址引脚吗?2023-04-28 888

-

可以在不使用外部SDRAM的情况下运行i.MXRT1176 (MIMXRT1176DVMAA) 控制器吗?2023-05-04 628

-

为MIMXRT1176生成的.bin文件加载到MIMXRT1171处理器中,无法从MCUExpresso IDE加载代码怎么解决?2023-05-18 480

-

W9864G6IH datasheet pdf资料(1M*42010-03-27 1108

-

TOP2004支持器件列表2006-07-03 3640

-

使用MIMXRT1176 MCU创建双核的C++应用项目工程2022-10-27 3108

-

软件代码配置进入MIMXRT1176 ISP模式2023-01-30 2527

全部0条评论

快来发表一下你的评论吧 !