5个特殊寄存器改变了当今的SoC

描述

在本文中,我们将介绍五个广泛使用的特殊寄存器,即;别名、影子、间接、锁定和触发缓冲区寄存器。

在当今的SoC中,我们已经看到了系统架构、节点大小、互连、安全性、编程语言和开发工具领域的许多创新。有时,我们低估了我们在日常工作中使用的简单创新的重要性和影响,这些创新是我们作为 SoC 架构师、验证工程师、硬件设计师或软件/固件开发人员。

特别是,让我们研究与硬件/软件接口层相关的创新 - 软件应用程序与硬件外设通信。具体来说,在寄存器空间中,硬件外围设备(如视频编解码器、蓝牙或 Wi-Fi)从处理器上执行的软件应用程序接收配置、控制和功能。十年前,在设计寄存器时,我们只需要RO、WO、RW、RC、RS、WS等的组合。但是今天的SoC已经变得如此复杂,以至于我们不得不进行创新,并思考更具创造性的方式来设计寄存器。在本文中,我们将介绍五个广泛使用的特殊寄存器,即;别名、影子、间接、锁定和触发缓冲区寄存器。

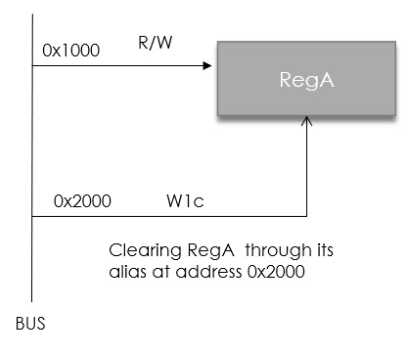

别名寄存器

这是一种可从同一地址映射中的多个地址访问的寄存器类型,但实际上它是一个寄存器。别名寄存器中的字段根据用于访问它们的地址具有不同的行为。如图 1 所示的示例,RegA 中的字段在使用0x1000地址访问时是可读和可写的,但在从0x2000地址访问时是写 1 到清除的。创建别名寄存器时应应用的一些准则:别名寄存器的硬件访问为 NA;字段不能是已别名字段的别名;并且别名字段的父寄存器不能是外部的。

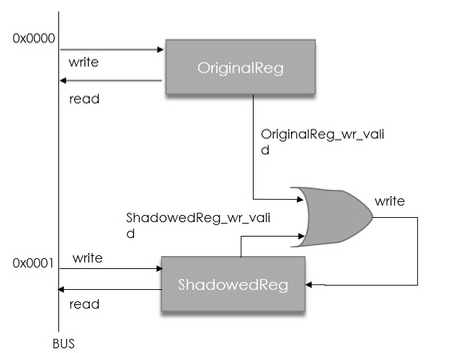

影子寄存器

当您的软件应用程序需要覆盖所有寄存器但稍后需要恢复数据时,解决方案是使用影子寄存器。通过寄存器总线写入寄存器的数据应自动复制或隐藏到地址映射中的另一个寄存器。如图 2 中的示例所示,OriginalReg 中的数据被复制到 ShadowReg。可以从总线访问ShadowReg,但对原始寄存器没有影响。多个影子寄存器可以影子单个原始寄存器。

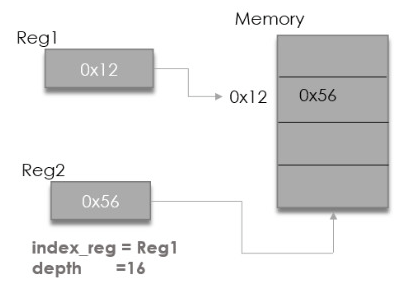

间接寄存器

某些寄存器或存储器位置不能通过专用地址直接访问,它们被称为间接寻址寄存器或简称间接寄存器。两个寄存器用于访问间接寄存器。

若要将值存储到间接寄存器数组中,请使用基本寄存器来保存实际地址。该指令检查基本寄存器,将其值解释为寄存器数组中的地址位置,并将数据寄存器中的值放入该位置。要从间接寄存器数组加载值,还使用了基本寄存器。此基本寄存器保存实际地址。该指令检查基本寄存器,将其值解释为地址,获取存储在该位置的值,然后将其加载到数据寄存器中。

如图 3 中的示例所示,Reg1 指定内存数组中的索引。Reg2 指定要写入的数据或存储从内存中读取的值。Reg2 需要一个间接寄存器大小的“深度”属性。

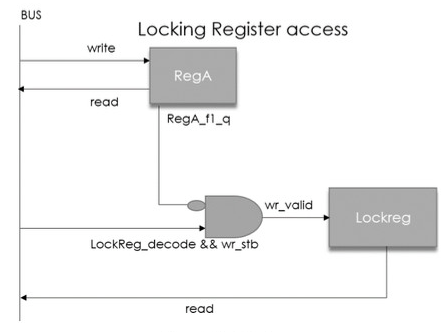

锁定寄存器

如果状态机受保护在寄存器后面,而该状态机只能由存储在另一个寄存器中的密钥启动,则 Lock 寄存器可能是解决方案。任何可写寄存器或字段都可以根据其他寄存器的字段值进行保护/锁定。此类寄存器称为锁定寄存器。锁定寄存器和保护/密钥寄存器可以位于不同的寄存器组中,但不能位于不同的块中。如图 4 中的示例所示,由属性 “lock” 指定的 Lock 寄存器由一个简单的表达式lock=RegA.f1 定义,这意味着寄存器 Lockreg 被锁定,具体取决于寄存器“RegA”(密钥寄存器)的字段“f1”的值。锁定机制也可以通过更复杂的表达式来定义,例如 lock = regA.FldA || regB.Lock_fld == 8‘b00000001&& regA.FldA == 4’b0011。此复杂表达式由不同的寄存器字段组成。在这种情况下,如果锁定表达式中的每个条件在运行时计算结果为 true,则寄存器的软件写访问权限将被锁定。

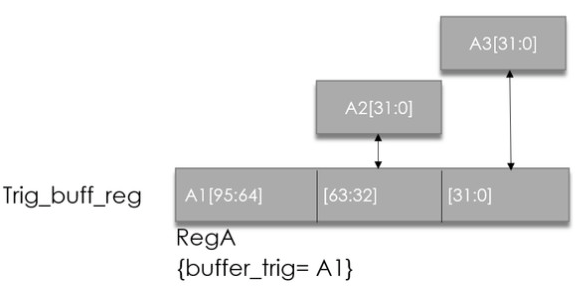

触发缓冲寄存器

有时需要从硬件端将大小大于总线宽度的寄存器作为一个原子单元写入和读取。这种寄存器从软件端按顺序写入/读取。这可以通过在与触发事件关联的内存空间中创建 N 寄存器缓冲区来实现。当触发事件发生时,写入/读取发生在缓冲区到硬件端可用的实际寄存器。触发事件可以是对最低有效位或最高有效位寄存器的读/写。例如,如图5所示,RegA是宽硬件寄存器,宽寄存器Reg.A1的MSB是触发器。Reg.A2 和 Reg.A3 是对应于宽硬件寄存器字段的缓冲区。

下一步是学习如何在IP-XACT或SystemRDL中定义这些特殊寄存器。还需要学习如何在RTL中对它们进行编码,并创建UVM寄存器模型和完整的UVM测试平台以进行验证。我们将在点播网络研讨会 5 对当今 SoC 有用的特殊寄存器中详细介绍后续步骤。在本次网络研讨会中,我们将提供这五个特殊寄存器的详细信息、它们的优势、用例和示例。我们还提供有关如何自动验证它们的最佳实践,以实现 100% 的功能覆盖率。

审核编辑:郭婷

-

特殊功能寄存器的解释整理汇总2024-05-09 512

-

SoC芯片上的寄存器设计与验证2023-10-20 4192

-

AArch64寄存器介绍2022-08-24 7761

-

五个广泛使用的特殊寄存器2022-06-08 5852

-

特殊寄存器与普通寄存器的区别2021-12-20 1662

-

51单片机的21个特殊功能寄存器的详细资料说明2019-09-10 2564

-

51单片机的一些特殊寄存器资料说明2019-07-26 1470

-

51单片机的21个特殊功能寄存器详细资料概述2019-07-09 4944

-

【硬见小百科】单片机的特殊功能寄存器2019-01-16 6340

-

浅谈ARM寄存器组织2017-10-18 1473

-

LPC2106的特殊寄存器及固件程序2016-10-14 688

-

寄存器,寄存器是什么意思2010-03-08 22415

全部0条评论

快来发表一下你的评论吧 !