ADC仿真时最大噪声频率设置

模拟技术

描述

前言

ADC仿真时,有时候需要在tran仿真的基础上添加噪声以评估热噪声及闪烁噪声对ADC精度的影响。在Spectre中,支持设置最大和最小噪声频率,其中最小噪声频率受到仿真时间的限制,在无特别需求的情况下默认设置为仿真时间分之一。而最大噪声频率的设置,虽然理论上设置得越大,仿真和实际情况相比越准,但越大的噪声频率也意味着越小的仿真步长和越长的仿真时间,影响研发进度。

由于电路本身带宽的限制,超出电路带宽范围的噪声天然地被电路抑制,因此不会产生影响,因此噪声最大频率设置得大于电路带宽即可完整地仿真出噪声的影响。

那么,如何找到这个影响噪声的带宽?如果噪声最大频率设置不足,对电路仿真会产生怎样的影响?本文将针对这两个问题进行简单地分析。

开关电容采样噪声理论回顾

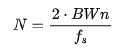

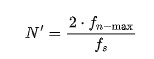

在笔者之前的文章中,对基于采样和噪声交叠产生的开关电容噪声进行了分析,本文中进行简单的回顾:总积分噪声为kT/C,等效带宽为BWn的RC网络产生的热噪声,在被满足fs<

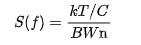

原本RC网络热噪声的等效谱密度为式(2):

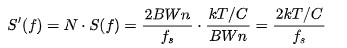

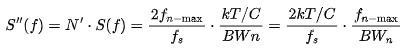

噪声采样交叠后的谱密度为式(3)

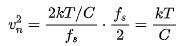

在奈奎斯特带宽fs/2内,总积分噪声可以表示为式(4):

如何设置最大噪声频率

如果仿真设置的最大噪声频率大于等效噪声带宽,那么多于等效噪声带宽的部分会被RC网络滤除,电路的噪声表现仍然符合上一小节的表述以及式(1)-(4),对仿真结果不会产生影响。

假设噪声最大频率fn-max设置不足,但仍远大于fs,即fs<

RC网络噪声等效谱密度不变,因此噪声采样交叠后的谱密度变为式(6):

将式(6)与式(3)对比可知,由于最大噪声频率设置不足导致仿真的噪声比实际的噪声变小。这种情况下仿真得到的ADC性能是不准确的,且略好于实际情况。

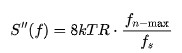

在这种情况下,还会出现违背电路理论的情况。由于BWn=1/4RC,因此根据式(6)可以进一步得到式(7):

此时,噪声谱密度,连同总积分噪声和电容C无关,这与实际理论的热噪声只和电容值C有关的理论相违背,导致电路设计者即使改变电容值(其他条件如开关尺寸,所设置的最大噪声频率保持不变),噪声也不会发生变化,因此设计者无法根据仿真结果评估自己的电容大小设置是否合理,也无法仿真出增大电容可以减小热噪声这一理论现象,从而影响设计者的判断。

如何确定最大噪声频率

如上文分析,最大噪声频率要设置得大于RC网络的等效带宽,才可以保证仿真结果符合实际电路的噪声表现。然而,电路中存在多个形成热噪声的RC网络,这就需要设计者准确得找到贡献噪声的RC网络,并根据它的等效噪声带宽设定最大噪声频率。

以下级板采样为例:采样结束时,电容上级板会先断开,之后下极板断开,因此上极板开关断开时的噪声注入会存储在采样电容上,之后采样电容上电荷保持不变,不会再注入噪声。由于线性度要求,下极板开关导通电阻通常远小于上极板开关,因此噪声等效带宽以及噪声谱密度主要由上极板确定,因此通过仿真确定上级板开关导通电阻和采样电容形成RC网络的等效噪声带宽,在仿真时将最大噪声频率设置得略大于其值即可。

在每个课题组,都有一个口口相传的最大噪声频率设计方法,例如20倍采样频率,100倍采样频率等,在一些情况下这样的经验确实奏效,但是这种不知理论的设计经验在某些特殊场景下也会出错,例如,如果某个电路中,如果开关导通电阻设计得足够小,导致如果20倍采样频率或者100倍采样频率仍然小于开关导通电阻和采样电容组成的RC网络的等效噪声带宽呢?

经验固然有用,但也不是总奏效!

总结

本文简单分析了ADC仿真时,最大噪声频率设置不当对仿真结果的影响,并给出了一些最大噪声设置的建议,希望可以对读者在ADC噪声仿真时提供一些参考,提高读者的噪声仿真精准度和效率。若文中有不当之处,烦请多多指教。

-

运放有哪些噪声源?什么是噪声频率曲线?2022-12-12 2749

-

什么是运放噪声频率曲线?怎么算噪声值?只需要3个公式!multisim仿一下(有仿真文件)2023-04-18 3578

-

multisim怎么仿真运放噪声频率曲线?怎么算噪声有效值?只需要3个公式!有仿真文件2023-10-10 5943

-

噪声频率可以设置吗2013-05-06 2234

-

噪声频谱密度比信噪比更有用吗?2018-10-29 1843

-

如何利用噪声频谱密度评估软件定义系统中的ADC2020-12-29 1526

-

一文教你如何利用噪声频谱密度评估软件定义系统中的ADC2020-12-31 2491

-

K波段低相位噪声频率综合器的设计与实现_郑永华2017-01-08 755

-

滤波电容容值与所滤噪声频率的关系2018-01-14 17095

-

LTC6946低相位噪声频率合成器在RF中的设计应用2019-08-26 4462

-

ADC噪声:时钟输入如何提供帮助2023-06-30 1603

-

用噪声频谱密度评估软件定义系统中的ADC2023-11-22 393

-

什么是运放噪声频率曲线?怎么算噪声有效值?2023-12-01 1639

-

噪声系数分析仪噪声频率范围设为多少2024-10-09 1542

-

LMX2541 超低噪声频率合成器技术文档总结2025-09-18 902

全部0条评论

快来发表一下你的评论吧 !