SPI通讯速度与容错率

SPI通讯速度与容错率

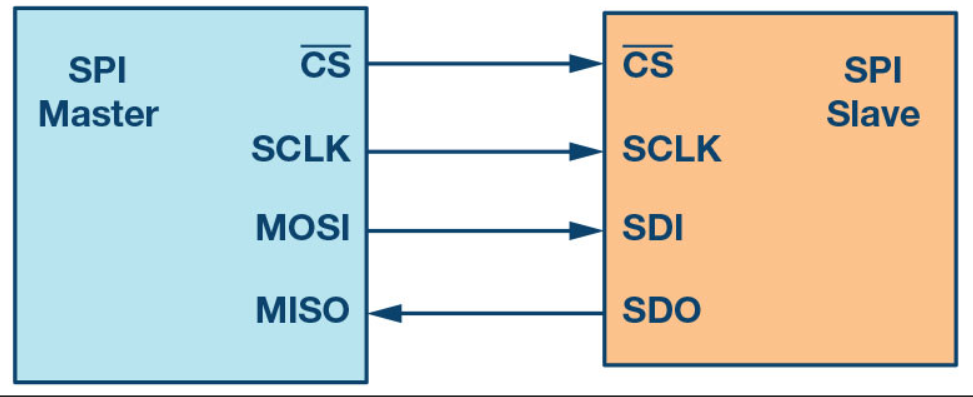

描述

通讯速率

对于SPI通信并没有规范最高的通信速率,在我的开发经验中有见过达到50Mbit/s的应用场景,但通常比较常见的还是10Mbit/s左右。

具体选用多快的通信速度,还得在实际项目中根据情况具体设计,比如:

1、当前主从机的主频和项目的具体应用都与SPI数据的处理能力有着直接关系,一般SPI通信的时钟频率都是来源于主频分频,这就在一定程度上限制了其通信速率上限。

即使能够达到较高速的速率,而处理器还需要处理更多的业务逻辑,再去处理SPI数据也是不够及时的,此时高速率并没有太大的意义了。

2、SPI硬件PCB布线长度等等影响着线路阻抗,这也同样限制了通信速率,一般通信距离越长,通信速度越低,否则容易造成通信不稳定。

特别是通信线路经过一些干扰源更是影响其稳定性,所以SPI作为一种相对高速的通信方式,一般都不会用于长距离通信中,而是大量用于微处理器与外部SPI接口的设备之间的通信,比如高速采样芯片ADC、处理器之间等等。

3、前面说了即使SPI主机能够达到较高的通信速率,但从机主频或者数据处理能力不够,这样也是没有太大意义的,当你可以通过配置从机为接收队列或者DMA等方式进行优化,当然高速率在多机中能够减少同步延时。

值得注意的是一些芯片标称的最高通信速率,是在比较好的外界条件下的测试值,超过了该标称值可能也能用,但并不会很稳定,容易导致通信异常。

所以具体选用多快的通信速度,还需根据实际情况分析确认。

容错性

SPI不像IIC那样存在应答机制,也没有流控制机制,当从机配置较低,如果一个报文还没处理完,后一个报文又到来,导致传输错乱,其通信过程几乎都是靠硬件来保证数据的传输稳定性,是一种不可靠传输。

当然如果是用于多机通信倒是可以通过制定可靠性校验协议来保证传输数据的稳定,但这也在一定程度上会降低通信的有效数据传输速度。

像stm32的SPI外设发送和接收都存在独立的CRC校验功能,大致的原理就是使用CRC在每个位上进行串行计算,然后在最后一次数据传输结束时来传输CRC校验值,接受方接收到CRC以后自动拿着数据和CRC值进行比对,看是与否有数据故障,如果存在传输问题就会置位相应的CRC故障标志位告知。

当然如果所选用的芯片SPI外设没有独立CRC模块可以模拟类似的操作进行处理,只是相对比较耗时,毕竟这个CRC得软件自己处理。

stm32的SPI外设的灵活度远不止这些,比如配置成双线单向模式等,可以把MISO和MOSI都向一个方向传输,从而提高一倍的传输速度,感兴趣可以参考一下手册玩一下。

审核编辑:刘清

-

该如何提高代码容错率、降低代码耦合度?2024-06-26 1933

-

SPI通讯协议你真的懂吗?5分钟教#SPI #总线 #串口通讯 #通讯 #电路知识 #电子工程师 #科工机械安泰小课堂 2024-01-23

-

硬件SPI与软件模拟SPI速度区别实测2021-12-22 3860

-

硬件SPI与软件模拟SPI速度区别2021-07-01 2112

-

容错CAN收发器TJA1054电子资料2021-04-21 1890

-

nrf24l01+和stm32的spi通讯要设置nrf24l01+的spi波特率吗?是在哪段代码设置的2020-06-09 1811

-

两块STM32之间SPI通讯进行的注意事项2020-04-04 16705

-

USART波特率与SPI速率对比2020-01-15 13790

-

Compact Rio下NI9401如何通过SPI通讯采集加速度信号?2018-04-16 6102

-

nrf24l01+和stm32的spi通讯需要设置nrf24l01+的spi波特率吗2018-01-21 6458

-

RN8302spi通讯例程2011.5.302017-08-24 1726

-

SPI通讯错误问题解决2016-09-30 8393

-

关于STM32的SPI主从双机通讯问题2015-10-11 16142

全部0条评论

快来发表一下你的评论吧 !