FPGA程序时序错误对雷达抗干扰的影响

可编程逻辑

描述

雷达抗干扰FPGA实现

1.副瓣匿影和副瓣对消联合处理的基本原理

2.基于FPGA的副瓣匿影实现

3.FPGA程序时序错误对工程的影响

4. 如何优化FPGA时序(一)

一、副瓣匿影和副瓣对消联合处理的基本原理

1.雷达电子对抗环境中,针对噪声干扰或者假目标干扰的单个干扰因素进行对抗的技术已相对成熟,但噪声干扰往往和密集假目标复合存在,近年来噪声加密集假目标复合干扰应用手段得到发展,我们实际工程主要是对噪声干扰和密集假目标分别进行了干扰效能分析,并提出了可以联合采用这2 种干扰,达到对雷达同时压制和欺骗目的.有源干扰主要是从副瓣进入雷达天线,为消除这种干扰,雷达普遍采用自适应副瓣相消[(ASLC)和副瓣匿影SLB) 技术;

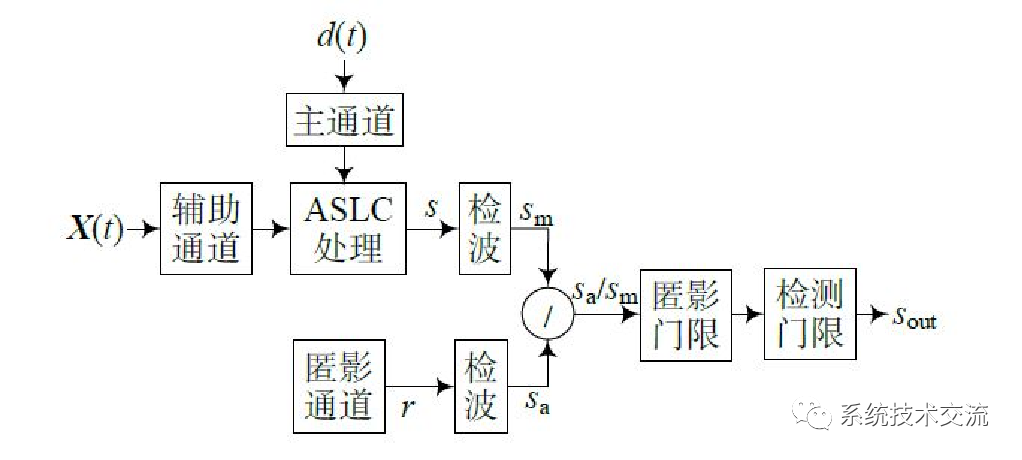

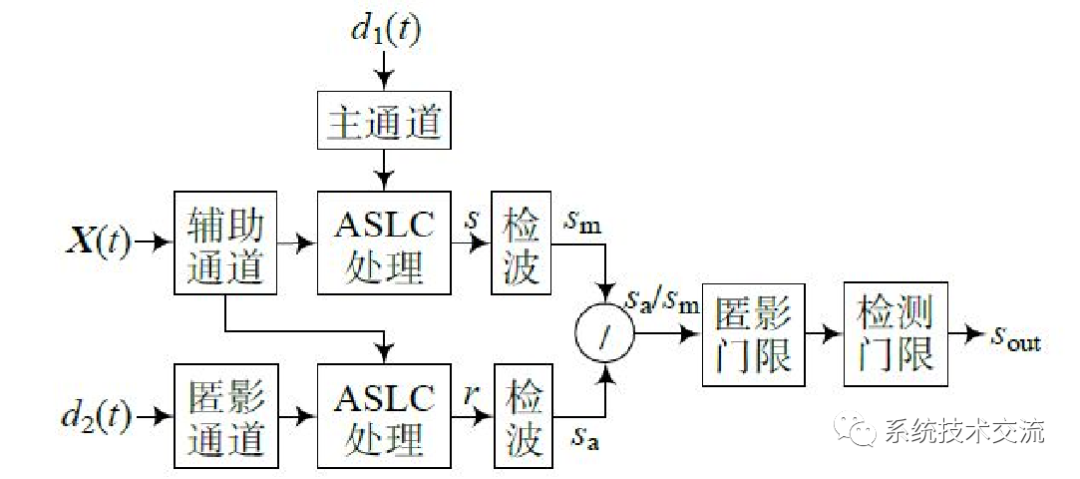

2.2. ASLC 技术可以对消掉噪声干扰,但无法抑制欺骗性干扰.而SLB 技术则主要利用主、辅天线增益的不同,对主辅通道信号的幅度进行比值,通过匿影门限的判决,从而抑制假目标干扰,但无法滤除噪声干扰.

3.常规示意图

三、FPGA程序时序错误对工程的影响

2. 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在时钟之前什么时候准备好,综合布线工具就可以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。附加时序约束的一般策略是先附加全局约束,然后对快速和慢速例外路径附加专门约束。附加全局约束时,首先定义设计的所有时钟,对各时钟域内的同步元件进行分组,对分组附加周期约束,然后对FPGA/CPLD输入输出PAD附加偏移约束、对全组合逻辑的PAD TO PAD路径附加约束。附加专门约束时,首先约束分组之间的路径,然后约束快、慢速例外路径和多周期路径,以及其他特殊路径。

3.分析时序,本质上是节点对节点之间的时序分析,如果没有节点,时序也就无从谈起。在FPGA中,我们可以把节点当作是寄存器与寄存器之间的时序分析,寄存器与寄存器之间可能还有一些组合逻辑充斥着。所以时序路径通常有四大类:

(1)寄存器到寄存器类型,即reg2reg;

(2)输入引脚到寄存器类型,即pin2reg;

(3)寄存器到输出引脚类型,即reg2pin;

(4)输入引脚到输出引脚类型,即pin2pin;

针对上述四种基本时序路径,最关心的就是数据信号和时钟锁存沿之间的建立时间和保持时间的关系。

///------------------------------------------------------

clc;

clear all;

close all;

x=[1 1 1 1 1 -1 -1 1 1 -1 1 -1 -1 1 1 1 -1];

N1=length(x);

res=conv(x,conj(fliplr(x)));

figure,plot(abs(res));

x=[x -x];N2=length(x);

figure,plot(x);

res=conv(x,conj(fliplr(x)));

figure,plot(abs(res));

//////////////////////

工程和代码请看连接:

链接:https://pan.baidu.com/s/17A8yEISd4sAdrUUIqItgRg

提取码:7ust

--来自百度网盘超级会员V6的分享

编辑:黄飞

-

基于微机保护控制接口装置实现CPLD抗干扰设计2019-04-25 1807

-

怎么提高雷达的抗干扰能力?2019-08-14 5030

-

怎么利用FPGA器件来设计抗干扰电路?2021-05-08 1505

-

微机系统软件抗干扰的方法2022-01-20 970

-

基于FPGA的光电抗干扰电路设计方案2010-02-09 921

-

ADS用于雷达高度表抗干扰研究2011-07-05 809

-

雷达抗干扰性能的评估模型研究2013-01-18 691

-

机载脉冲多普勒雷达的抗干扰措施2016-12-26 957

-

雷达抗干扰技术研究2017-12-06 3804

-

机载雷达接收机滤波器抗干扰2018-01-10 1185

-

FPGA程序时序错误对工程的影响2019-11-08 3328

-

最强抗干扰的5.8G雷达模块哪里有?2020-03-28 4261

-

雷达抗干扰原理说明2021-03-24 1508

-

雷达抗干扰技术主之雷达旁瓣消隐实现原理2022-12-15 12621

-

为什么磁环可以抗干扰?磁环抗干扰的原理 抗干扰磁环的作用2023-12-29 9399

全部0条评论

快来发表一下你的评论吧 !