PCI Express真的需要85欧姆吗?

电子说

描述

以下内容为Samtec做过SI相关主题研讨会上,专家做的一些问题沟通互动,关于PCIe 85 欧姆的布线的问题。

丹尼:史蒂夫,你能给我们简要介绍一下这次网络研讨会吗?你为什么选择这个主题?

史蒂夫:如今,高速系统面临着许多必须在同一堆叠中实现的同步阻抗要求 -以太网的100欧姆差分阻抗,90欧姆的USB,85欧姆的PCIe以及无数的单端DDR要求。我们希望遵循规范,以正确的阻抗选择组件和布线走线。然而,有时也存在一些障碍——首选元件不是 85 欧姆,或者上游封装是另一种阻抗。我们想遵循 PCIe 的 85 欧姆的口头禅,但这可能并不容易。我们能做什么,规范怎么说?

丹尼:PCIe 是否需要 85 欧姆连接器?

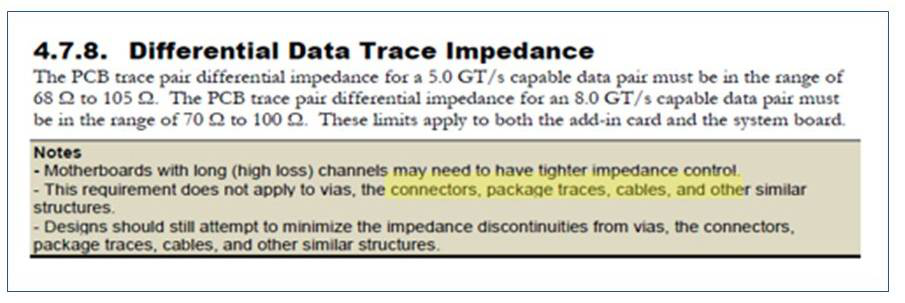

史蒂夫:让我们直接进入规范。关于 PCIe 85 欧姆要求,规范说“此要求不适用于过孔、连接器、封装、电缆和其他类似结构” PCIExpress 卡 EletroMechanical 规范修订版 中的内容:

85欧姆以外的连接器是可以接受的,事实上这很常见。在短时间内,触点暴露在空气中(如CPU插槽),这会增加阻抗。这些短距离偏移将高于85欧姆,但在回波损耗中不会起不利影响。事实上,在兼容的 Gen3 和 Gen4 连接器上观察到 110 欧姆是很常见的。

丹尼:在PCB上,是否需要85欧姆布线?

史蒂夫:对于遵循CEM(卡电子机械)规范的可互操作系统和卡,它是必需的,确保任何配接设备的阻抗匹配。

所有其他系统(具有任意数量的连接器或电缆)都可以使用任何PCB阻抗。许多封装和连接器设计为支持多个I / O,并且具有100欧姆甚至93欧姆的阻抗作为平衡折衷方案。我建议查看并确定哪种阻抗可能最适合您的特定设计。

93欧姆布线变得越来越普遍,但继续使用85欧姆布线以及更高阻抗的封装和连接器并非没有道理。较低的PCB阻抗确实具有一些优点,包括更低的损耗,更好地匹配密集的BGA,以及对阻抗变化的更大容忍度等等。

丹尼:通过布线传输PCIe是否需要85欧姆?

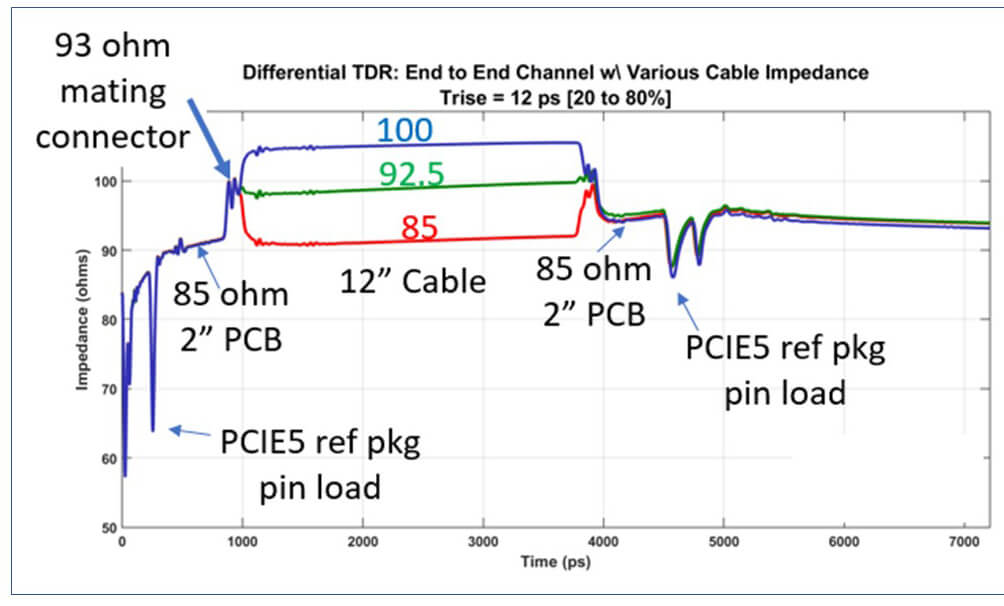

史蒂夫:选择电缆阻抗以匹配PCB上使用的阻抗是很诱人的。但是,有几个需要考虑因素:首先,更高频率的反射比PCB本身对配接连接器阻抗的参数更大。如果给定连接器的输入信号从PCB上的85增加到93欧姆,则最好保持在93欧姆,并且不会通过减少到85欧姆电缆来产生新的反射。

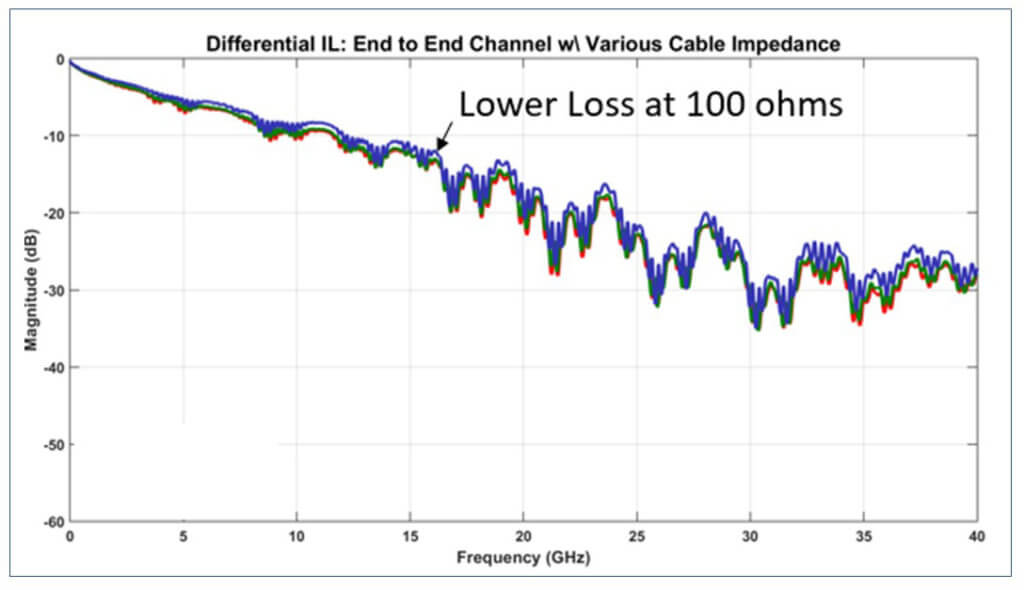

其次,阻抗和损耗之间的关系与PCB关系成反比。也就是说,较高阻抗的电缆具有较少的插入损耗,而较高阻抗的PCB则具有更大的损耗。85 欧姆和 100 欧姆之间的损耗差高达 14%。

最终,电缆阻抗的选择取决于系统的优先级。如果插入损耗是最大的限制,那么 93 或 100 欧姆电缆是最佳选择。

丹尼:非常好!有什么结束语吗?

史蒂夫:希望我们的读者能够查看他们的特定设计,选择最佳阻抗,而不是局限于85欧姆。请记住,当使用可互操作的CEM插槽时,该规范仅要求PCB布线为85欧姆。当涉及到连接器、电缆、封装和 PCB 与其他连接器的布线时,该规范允许任何最适合您的设计的阻抗。

一己之见:很久之前就有听连接器的厂商说过,端子的设计一般做不到85欧姆,都是在90欧姆以上,当时就很好奇,为什么这样?当时给出的解释是工艺方面的问题。这篇文字给出的最佳阻抗说法,换句话说,所有的设计都是匹配和控制能量的反射。心有规则而不拘泥于此,抓住本质的东西,这才是总线链路设计的管控基本法。

审核编辑:汤梓红

-

PCI Express Endpoint Master DMA2014-08-23 3083

-

如何去设计一种PCI Express接口?2021-05-21 1711

-

FPGA的PCI Express接口有哪些优势?2021-05-26 1863

-

PCI Express的基本工作原理2009-10-23 1639

-

PCI Express 至PCI 桥设计原理及应用2010-03-06 815

-

pci express总线概念2006-12-25 2324

-

PCI Express插槽,什么是PCI Express插槽2009-04-26 5591

-

PCI Express总线技术白皮书2009-10-04 1484

-

PCI-Express插槽2009-12-24 624

-

什么是PCI Express接口2009-12-25 3048

-

PCI Express总线2010-01-22 858

-

从PCI、PCI-X到PCI-Express之间的连接2012-06-05 4147

-

PCI Express IP核应用参考设计2016-06-07 849

-

PCI Express layout guide2017-09-11 1616

-

PCI Express卡机电规格2023-03-13 793

全部0条评论

快来发表一下你的评论吧 !