设计高速印刷电路板的最佳实践

描述

设计高速板是嵌入式应用的重要组成部分。如今,印刷电路板(PCB)的设计方式应自动满足高级解决方案的要求。这就是高速高频PCB设计成为硬件工程师重要课题的最大原因.

正确的硬件设计方法正成为产品设计服务能力的必要条件,以实现产品公司定义的项目时间表和成本。在设计具有PCI Express、SATA和LPDDR4等接口的高速电路板时,如果没有深入的高速设计知识和经验,实现第一个正确的可靠设计更具挑战性。

当我们谈论高速电路板设计时,从架构设计开始,在硬件设计生命周期中有许多领域需要研究,例如组件选择、接口时序和直流特性分析、原理图设计、所需的堆叠设计、布局设计、SI 分析、PI 分析等等。为了突出高速设计实践,下面我们详细讨论了最初的两个重要步骤:

楼层规划策略

平面规划是一个可视化图表,可视化了电路板上所有互连子部分的位置。没有适当布局规划的布局布线可能会导致PCB尺寸增加、寄生效应、布线拥塞、EMI问题、层叠中层数要求更多等。通常,几乎拥有布局规划,用于估算PCB尺寸,隔离PCB上的模拟数字RF子部分,并根据产品外壳设计最终确定机电组件的放置。

高速电路板设计需要第二级平面规划,以避免PCB布局期间的返工以及后期设计的时间和成本增加。放置互连模块的良好做法之一是将PCB空间划分为多个块,然后根据驱动器和接收器或收发器之间尽可能短的互连来决定互连模块最适合哪个块。这将有助于确定PCB堆叠中的布线方向和所需层。

让我们了解在电路板上优化放置的重要参数:

为高速电路板选择小型封装尺寸元件,以减少高速传输线路上的阻抗失配和寄生效应、电感和电容。请注意,较小的组件包可能存在良率问题。根据装配供应商的能力咨询他们来做出决定

从高引脚数元件和机电连接器开始放置

将组件分组为逻辑子部分,并按照组件或逻辑子部分放置的示意图逻辑流程进行操作

印刷电路板层堆叠

它是导电层和绝缘层一个接一个的排列,以便在布局设计之前制作PCB结构.PCB堆叠在高速电路板设计中很重要。定义良好的层叠有助于最大限度地减少EMI辐射并提高PCB的电磁兼容性。此外,它还有助于增强信号完整性、设计的电源完整性、不受外部噪声影响,并降低制造成本。

定义电路板层堆叠的三个重要步骤:

确定所需的层数:信号层取决于信号完整性要求,如低串扰、低间距元件、高引脚数元件(如BGA)、固定PCB尺寸等。电源和接地层数取决于高速设计中的配电、低 EMI 和信号返回路径要求,从而降低电源轨中的直流压降并提高电源完整性。

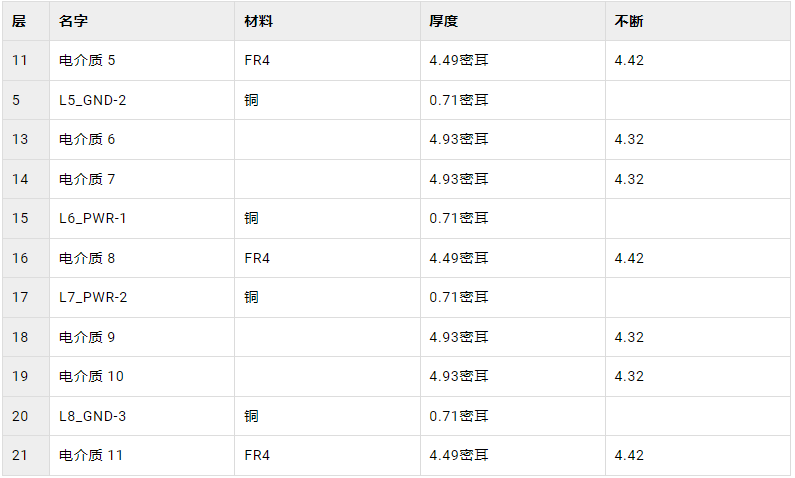

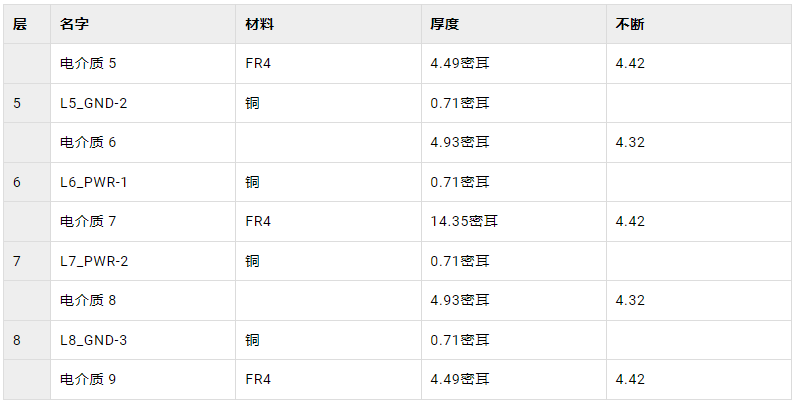

层叠中的层排列:一旦确定了信号、电源和接地层的数量,下一步就是按顺序排列它们。在层叠安排中,我们需要遵循的一些规则如下:

电源层和接地层应彼此靠近,以获得良好的规划间电容

避免两个相邻的信号层。如果不可能,请确保信号层与参考接地层之间的预浸料厚度较低,两个信号层之间的芯层厚度较高,如下图所示

从中心到顶部和底部建立对称或平衡的堆叠

在堆叠中添加可能的接地层,以减少高速信号的共模辐射

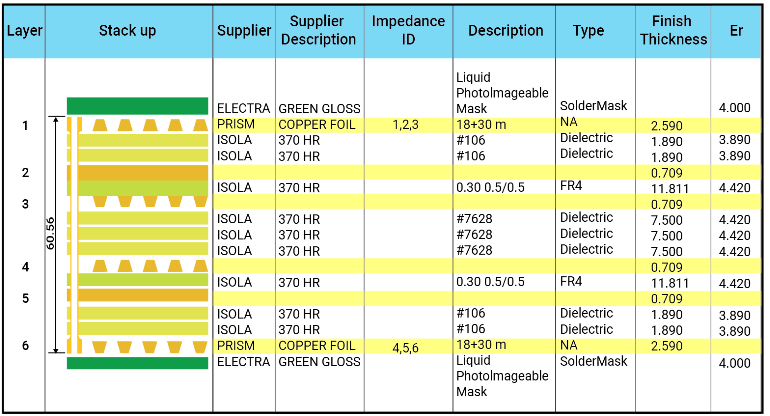

确定材料类型:PCB由四种不同类型的材料组成, 即丝网印刷材料, 阻焊材料, 铜, 和基板.影响高速设计参数(如阻抗和信号完整性)的基板材料在大多数常见应用中是FR4。由于快速时钟速率和数据传输,高速电路板组件比普通电路板散发更多的热量,数据传输也会传导到PCB。设计人员可以选择中等或高Tg,玻璃化转变温度,FR4材料,以实现长期运行可靠性。Tg是PCB基板开始变得机械不稳定的温度。FR4 适用于时钟速率为 <5GHz 的应用。超过5GHz的高速板需要使用其他材料,如Nelco和Megtron。对于56GHz以上的频率,微波频率需要Rozer材料用于堆叠

在定义了层堆叠之后, 现在设计人员应该开始让他们的PCB制造商或合同制造商参与进来,根据材料的可用性, 基板厚度, 和所需的信号阻抗, 获得实际可能的堆叠.为了达到所需的阻抗, PCB制造商在PCB制造过程中调整堆叠的介电厚度.可以与制造商核实,并确保在制造过程中验证的阻抗在单端和差分信号的容差范围内。

-

探讨高速印刷电路板布局的运算放大器2021-02-04 5026

-

什么是PCB助焊剂?印刷电路板焊接的目的2020-11-23 5807

-

如何设计和创建自己的印刷电路板2020-10-20 3315

-

印刷电路板图设计的基本原则和要求2019-04-12 4509

-

印刷电路板设计2018-03-28 1049

-

印刷电路板设计基础课程2017-01-05 1089

-

印刷电路板图设计的基本原则2014-05-15 3281

-

印刷电路板的设计与制作2010-02-11 1121

-

什么是单面印刷电路板?2009-12-09 2829

-

印刷电路板设计的基本原则2009-11-17 804

-

基于OSP在印刷电路板的应用2009-11-16 2160

-

印刷电路板2009-09-30 1961

-

印刷电路板设计的最佳实践 Best Practices in2009-07-01 1604

-

高速数字系统印刷电路板的设计要点2009-03-24 746

全部0条评论

快来发表一下你的评论吧 !