斩波运放和陷波滤波器的工作原理

模拟技术

描述

前言

在CMOS运放中,由于工艺失配的影响,使得运放会产生一个固定的失调。同时,1/f噪声也是运放需要经常面对的一个问题。由于失调是一个直流值,而1/f噪声的大小和频率成反比,在低频时1/f噪声最大,因此失调和1/f对运放的影响在一定频率范围内是相同的。克服这样的低频噪声,主要有两种思路:

方法一:增大运放输入对管的面积,由于失调和1/f噪声的主要来源均为输入对管,而失调和1/f噪声均随着晶体管面积的增加而减小,因此增大输入对管的面积是一种有效的方法。但是这种方法的缺点也很明显,即需要很大的芯片面积,同时面积的增大也会带来寄生电容的增大,从而引起一系列其他的问题。因此,这种方法相对采用地较少。

方法二:采用斩波和自零技术,这样避免了芯片面积的增大,但是会增加电路的复杂度,同时斩波和自零均需要时钟电路,除此之外,采用斩波和自零会带来运放输入电流,减小了运放的输入阻抗。

除了上述两种方法,也有一些其它的方法,例如模拟校准等。

在本文中,着重对斩波技术进行了分析。相比通常采用频域的方式,本文以时序的方式作为切入点,理解斩波如何消除低频输入噪声的影响。同时,还介绍了常和斩波一起使用的陷波滤波器的时域原理。

斩波运放时域分析

在本文中,我们通过一个差分输入,单端输出的OTA组成的Buffer来进行分析。同时,将1/f噪声对电路的影响也归结在失调中,这在当对运放关注的频率足够高的情况下是成立的。

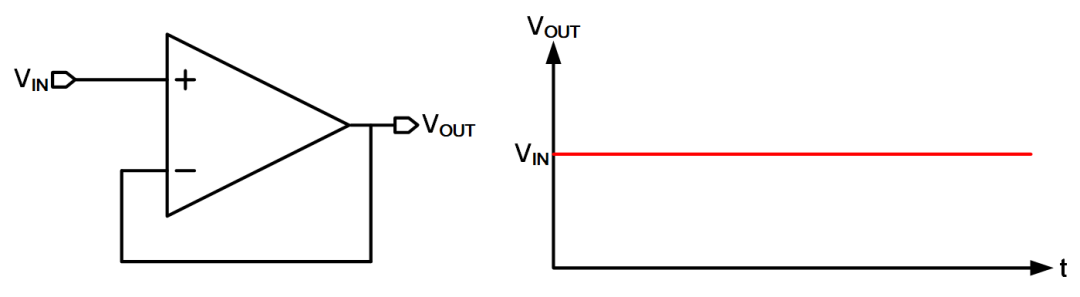

图1 无输入失调时Buffer输出

图2 存在输入失调时Buffer输出

在运放不存在输入失调时,Buffer将输入信号VIN缓冲至其输出VOUT,如图1所示。然而,当存在一个失调时,Buffer的输出从VIN偏移VOS,如图2所示。

图3 采用斩波后Buffer表征

为了克服失调电压的影响,采用斩波技术如图3所示。斩波的本质是通过对运放差分输入的不断切换,将正负极性的失调电压VOS动态地在输入VIN端进行切换,可以理解为理想运放输入在VIN+VOS和VIN-VOS之前进行轮换。对Buffer而言,如果Buffer的带宽远大于斩波频率fCH,那么输入的每次切换Buffer输出都可以快速建立,得到的输出波形如图3(右上)所示,输出在VIN+VOS和VIN-VOS直接切换。相反,如果Buffer的带宽远小于斩波频率fCH,那么输入的每次切换Buffer输出都无法完全建立,导致其输出呈现出一个在VIN值上下波动的锯齿波信号,如图3(右下)(有兴趣的读者可以分析,运放未稳定时输出中间值不一定是VIN,但最终中间值总会稳定在VIN)。

上述的第一种情况经常应用在一些过采样ADC上,ADC对VIN+VOS和VIN-VOS进行轮换采样,最终得到的结果进行平均后即为VIN(平均本质上是一种低通滤波)。

这两种情况下的输出都可以经过低通滤波得到图1所示的输出曲线。但是相比低通滤波,有一种更好的选择—陷波滤波,将在下一节进行介绍。

陷波滤波器时域分析

图4 采用斩波+陷波滤波器后Buffer表征

如图4所示为添加了陷波滤波器后的斩波运放及其时域表征。陷波滤波器通过两个相差一个陷波时钟相位的采样保持电路组成。在使用陷波滤波器时,需要斩波频率满足上一节所述的第二种情况:fCH>>BW。在这种情况下,斩波运放的输出VA表征为一个在VIN上下波动的锯齿信号,并且在稳定后,VA总在半个斩波频率的中间穿过VIN。采用陷波滤波器,对VA穿过VIN这一点进行采样,并在后半个陷波周期保持,那么后半个陷波周期输出VOUT就可以恒定保持为VIN。采用两个这样的采样+保持电路,在一个电路采样时,另外一个电路进行保持,那么就可以保证输出VOUT总为VIN,因此得到了一个平滑的,输出总为VIN的输出曲线。从图4可以看出,斩波+陷波滤波器,可以将VOS对Buffer输出的影响抵消,且得到一个平滑的,输出总为VIN的曲线。

总结

本文简单地通过时域分析的方式,介绍了斩波运放+陷波滤波器的工作原理,以及其如何抵消失调电压(1/f低频噪声)对运放的影响。虽然在本文的分析中,输入VIN为恒定电压,但对于其他类型的输入信号,当斩波频率fCH远大于输入频率时(也是斩波的通常应用情况),在一个斩波频率内输入近似是不变的,因此本文的分析对其他类型的输入信号同样有效。

-

有源陷波滤波器的定义和工作原理2024-09-27 3397

-

陷波滤波器和低通滤波器的区别是什么2024-08-21 2637

-

基于运放的窄带滤波器设计2011-12-05 2428

-

运放组成的单峰特性滤波器电路2009-12-07 1520

-

运放积分器的工作原理2009-06-28 16523

-

带通和陷波滤波器2008-06-12 2049

全部0条评论

快来发表一下你的评论吧 !