密度提升近3倍,高NA EUV光刻机有何玄机

密度提升近3倍,高NA EUV光刻机有何玄机

描述

电子发烧友网报道(文/周凯扬)到了3nm这个工艺节点之后,单靠现有的0.33NA EUV光刻机就很难维系下去了。为了实现2nm乃至未来的埃米级工艺,将晶体管密度推向1000MTr/mm2,全面投入使用高NA EUV光刻机已经势在必行了。据了解,一台高NA EUV的光刻机成本就可能达到3.2亿美元,这样一个天价的光刻系统究竟能带来哪些优势,又存在哪些挑战呢?

规模和密度的平衡,我们为什么需要高NA光刻机?

从今年发布的不少新品来看,即便工艺没有太大的变化,芯片的性能仍在稳步提升,有的是从架构上找到了创新,有的选择了改善带宽之类的性能。但我们也都能看出,其中有一部分产品选择了走大规模的路线,比如苹果的M1 Ultra。这种方式虽然增加了功耗,但对于那些对功耗并不敏感的产品来说,似乎也是可行的一种思路,那么我们真的有必要用到更贵的高NA EUV光刻机进一步提升密度吗?

这个问题的答案其实不言而喻了,英特尔、台积电等晶圆厂提前预订的高NA EUV光刻机订单已经证明了它的重要性。归根结底还是我们的晶体管密度需求仍在不断攀升,但我们需要明白这个需求并不是线性增长的。

新世纪的20年代,很可能成为深度技术发展的黄金十年,比如边缘AI芯片、基于CMOS的NIR/SWIR成像器、光电集成的片上激光雷达等等。你可以说推动工艺发展最大的功臣是智能手机芯片,但其他应用对高密度的需求同样不可小觑,因为这对它们来说也就意味着更高的存储容量和带宽、更高的算力。

如今的深度学习在大规模模型的爆发下,所需算力每几个月就会翻一番,但现在能效比已经成了优先级更高的指标,要想同时满足性能和算力的话,主要方法有四种:一是换一种系统级计算架构,比如DSA架构;二是充分利用3D设计,也就是我们常说的3D封装和堆叠技术;三是从晶体管架构上创新,譬如纳米管、纳米片、CFET和原子沟道等;第四个则是目前看来最快捷的一条路线,通过光刻技术的发展直接提升密度。

高NA光刻机带来的优势

固然高NA EUV光刻机能够让我们挺进下一工艺节点,但它带来的好处并不只是增加晶体管密度。先从技术价值上来说,0.55的大数值孔径与0.33相比,可以实现尺寸减小2/5的特征图形,将密度提升2.9倍。其次,高NA EUV光刻机带来了更高的成像对比度,从而极大改善线宽均匀性,在更少的光刻胶剂量下实现更少的条纹变化。

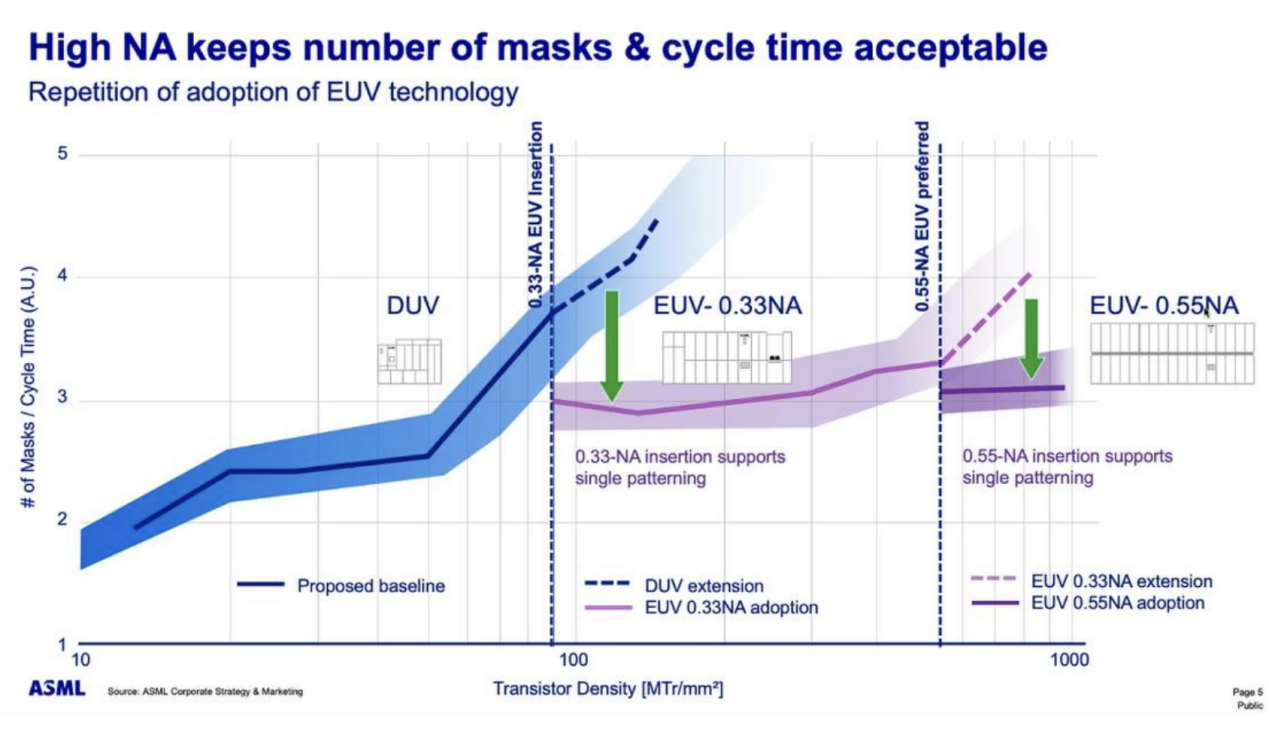

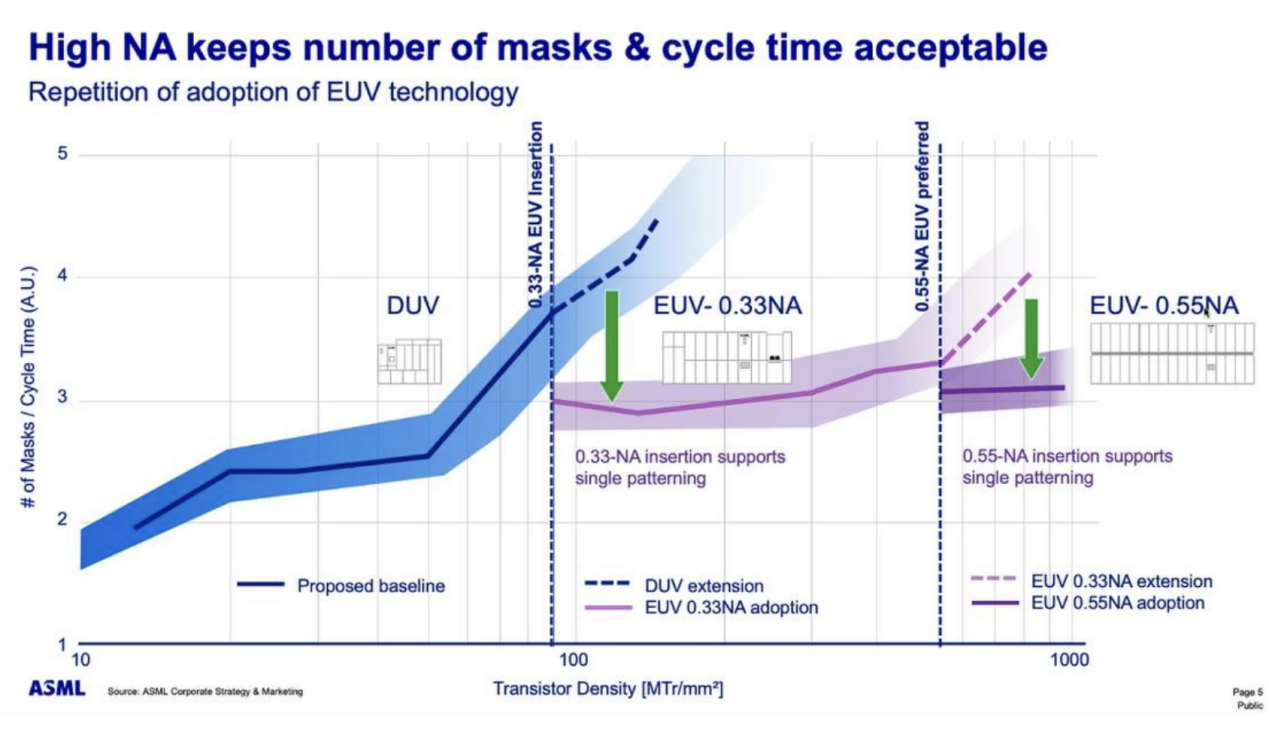

光刻机晶体管密度的变化趋势 / ASML

对于使用光刻机的晶圆厂来说,以上的优势减少了多重光刻的需要,也减少了光刻胶的剂量使用,从而降低了整体成本。其次,由于工序的简化,曝光后光刻胶图形边缘与设计图形之间的边缘放置误差也一并减少了。这也一并导致了掩膜处理周期的减少,极大提高整个晶圆厂的运转效率。

有突破就有挑战

既然高NA EUV光刻机有这么多好处,ASML为何还不加快进度将其造出来,而是要等到2024年才能出货呢?答案是目前看来,这类光刻机的制造和应用都面临着不小的挑战,以至于在2025年大规模投入都存在一定阻碍。

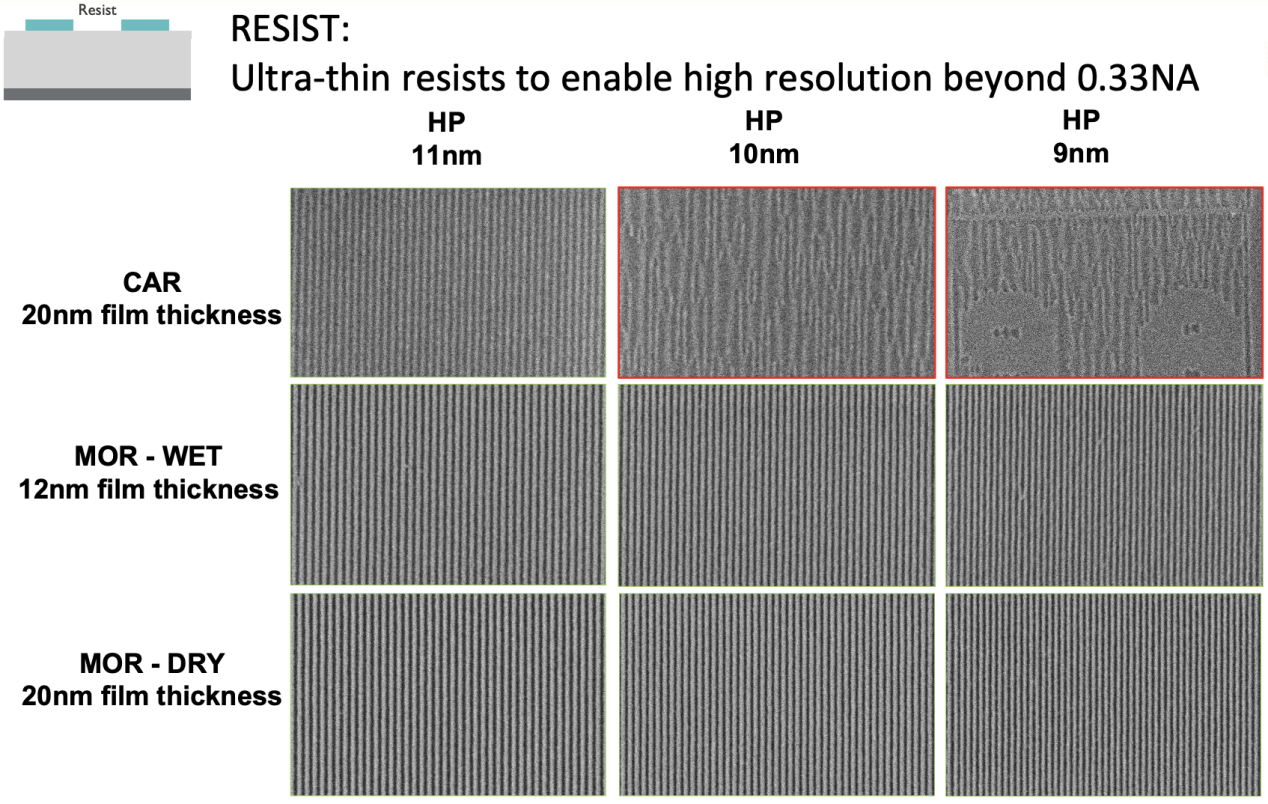

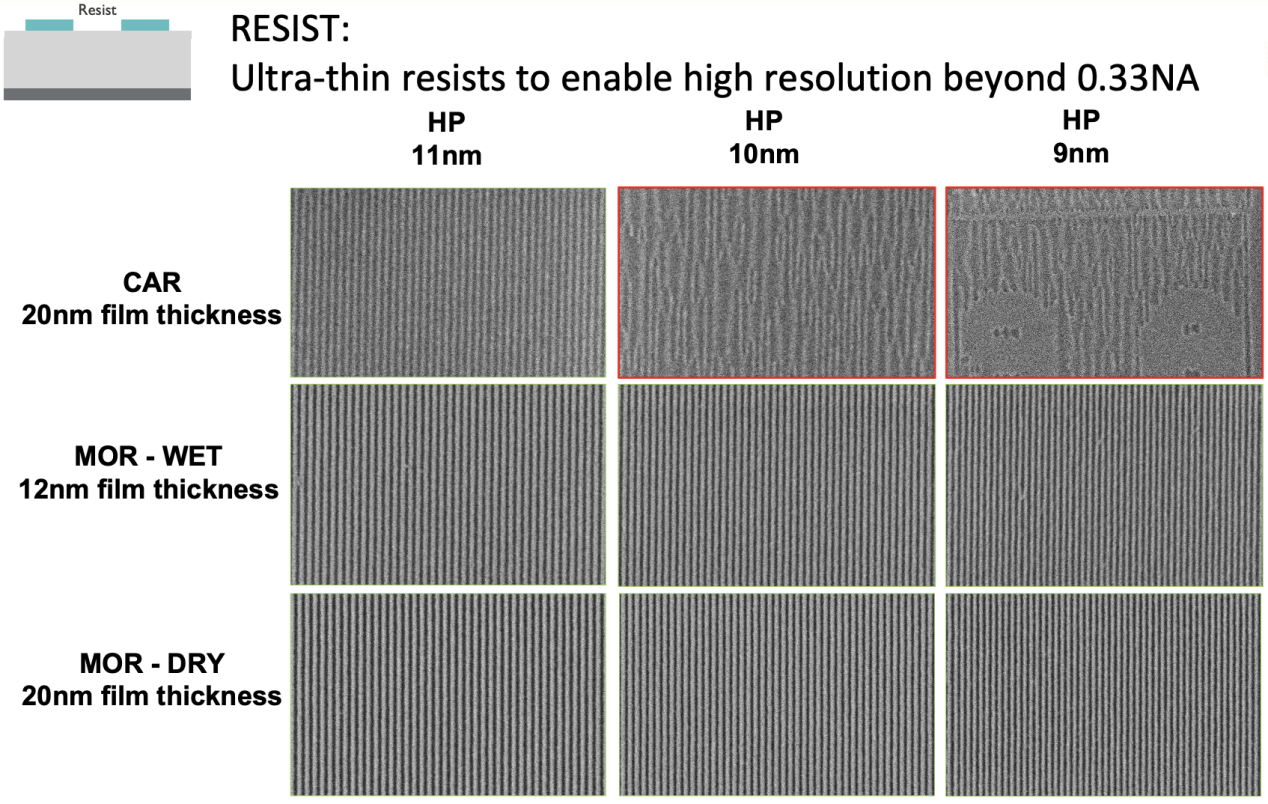

0.33NA之后所需的光刻胶厚度 / IMEC

我们先从光刻胶说起,高NA EUV光刻机需要用到更薄的光刻胶,比如小于20nm,这样才能维持2:1这一理想的线高宽比。否则因为更大的厚度,就会超过这一比例,在曝光阶段容易因为重心变化引发光刻胶塌陷。除了需要超薄、超高分辨率的光刻胶,还要考虑引入的随机效应,这种随机效应会导致不必要的失效和特征图形粗糙度,从而影响到芯片的性能,甚至可能会使整个系统失效。

再者就是高NA EUV光刻机需要用到的新光掩膜,光掩膜对于芯片的制造来说至关重要,因为它的明暗区域内保存着设备成品所需的设计布局信息。随着特征图形尺寸的减小,与理想光掩膜之间的偏差对最终晶圆图案的影响也在增加。

为祸作乱者之一就是光掩膜的3D效应,比如EUV中,光线以6°的入射角击中光掩膜,以此产生的反射可能会产生屏蔽,从而因为光掩膜的缘故在晶圆上产生成像误差。所以必须开发新的变形光掩膜技术及规范,才能减轻3D效应带来的影响。

小结

在更高的芯片性能需求下,转向高NA的EUV光刻机已是必然,这类光刻系统也能彻底释放现代晶体管结构创新的潜力,引领我们走向埃米时代。但我们也不能就此忘记刚引入EUV光刻机时的教训,3年后ASML的高NA EUV实现高密度已经是定数,但良率和产量问题才是这套系统交付后最大的问题。

打开APP阅读更多精彩内容

规模和密度的平衡,我们为什么需要高NA光刻机?

从今年发布的不少新品来看,即便工艺没有太大的变化,芯片的性能仍在稳步提升,有的是从架构上找到了创新,有的选择了改善带宽之类的性能。但我们也都能看出,其中有一部分产品选择了走大规模的路线,比如苹果的M1 Ultra。这种方式虽然增加了功耗,但对于那些对功耗并不敏感的产品来说,似乎也是可行的一种思路,那么我们真的有必要用到更贵的高NA EUV光刻机进一步提升密度吗?

这个问题的答案其实不言而喻了,英特尔、台积电等晶圆厂提前预订的高NA EUV光刻机订单已经证明了它的重要性。归根结底还是我们的晶体管密度需求仍在不断攀升,但我们需要明白这个需求并不是线性增长的。

新世纪的20年代,很可能成为深度技术发展的黄金十年,比如边缘AI芯片、基于CMOS的NIR/SWIR成像器、光电集成的片上激光雷达等等。你可以说推动工艺发展最大的功臣是智能手机芯片,但其他应用对高密度的需求同样不可小觑,因为这对它们来说也就意味着更高的存储容量和带宽、更高的算力。

如今的深度学习在大规模模型的爆发下,所需算力每几个月就会翻一番,但现在能效比已经成了优先级更高的指标,要想同时满足性能和算力的话,主要方法有四种:一是换一种系统级计算架构,比如DSA架构;二是充分利用3D设计,也就是我们常说的3D封装和堆叠技术;三是从晶体管架构上创新,譬如纳米管、纳米片、CFET和原子沟道等;第四个则是目前看来最快捷的一条路线,通过光刻技术的发展直接提升密度。

高NA光刻机带来的优势

固然高NA EUV光刻机能够让我们挺进下一工艺节点,但它带来的好处并不只是增加晶体管密度。先从技术价值上来说,0.55的大数值孔径与0.33相比,可以实现尺寸减小2/5的特征图形,将密度提升2.9倍。其次,高NA EUV光刻机带来了更高的成像对比度,从而极大改善线宽均匀性,在更少的光刻胶剂量下实现更少的条纹变化。

光刻机晶体管密度的变化趋势 / ASML

对于使用光刻机的晶圆厂来说,以上的优势减少了多重光刻的需要,也减少了光刻胶的剂量使用,从而降低了整体成本。其次,由于工序的简化,曝光后光刻胶图形边缘与设计图形之间的边缘放置误差也一并减少了。这也一并导致了掩膜处理周期的减少,极大提高整个晶圆厂的运转效率。

有突破就有挑战

既然高NA EUV光刻机有这么多好处,ASML为何还不加快进度将其造出来,而是要等到2024年才能出货呢?答案是目前看来,这类光刻机的制造和应用都面临着不小的挑战,以至于在2025年大规模投入都存在一定阻碍。

0.33NA之后所需的光刻胶厚度 / IMEC

我们先从光刻胶说起,高NA EUV光刻机需要用到更薄的光刻胶,比如小于20nm,这样才能维持2:1这一理想的线高宽比。否则因为更大的厚度,就会超过这一比例,在曝光阶段容易因为重心变化引发光刻胶塌陷。除了需要超薄、超高分辨率的光刻胶,还要考虑引入的随机效应,这种随机效应会导致不必要的失效和特征图形粗糙度,从而影响到芯片的性能,甚至可能会使整个系统失效。

再者就是高NA EUV光刻机需要用到的新光掩膜,光掩膜对于芯片的制造来说至关重要,因为它的明暗区域内保存着设备成品所需的设计布局信息。随着特征图形尺寸的减小,与理想光掩膜之间的偏差对最终晶圆图案的影响也在增加。

为祸作乱者之一就是光掩膜的3D效应,比如EUV中,光线以6°的入射角击中光掩膜,以此产生的反射可能会产生屏蔽,从而因为光掩膜的缘故在晶圆上产生成像误差。所以必须开发新的变形光掩膜技术及规范,才能减轻3D效应带来的影响。

小结

在更高的芯片性能需求下,转向高NA的EUV光刻机已是必然,这类光刻系统也能彻底释放现代晶体管结构创新的潜力,引领我们走向埃米时代。但我们也不能就此忘记刚引入EUV光刻机时的教训,3年后ASML的高NA EUV实现高密度已经是定数,但良率和产量问题才是这套系统交付后最大的问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如何提高光刻机的NA值2025-01-20 2445

-

台积电A16制程采用EUV光刻机,2026年下半年量产2024-05-17 2010

-

密度提升近3倍,高NA EUV光刻机有何玄机2022-12-07 1835

-

euv光刻机是哪个国家的2022-07-10 8519

-

euv光刻机可以干什么 光刻工艺原理2022-07-06 8343

-

euv光刻机三大核心技术 哪些公司有euv光刻机2022-07-05 18580

-

台积电将于2024年引进ASML最新EUV光刻机,主要用于相关研究2022-06-17 7578

-

中科院5nm光刻技术与ASML光刻机有何区别?2021-03-14 25234

-

EUV光刻机还能卖给中国吗?2020-10-19 10744

-

光刻机工艺的原理及设备2020-07-07 17322

-

关于EUV光刻机的分析介绍2019-09-03 14869

全部0条评论

快来发表一下你的评论吧 !