干货:PCIE6.0技术剖析

描述

关于PCIe6.0 你需要知道的都在这里

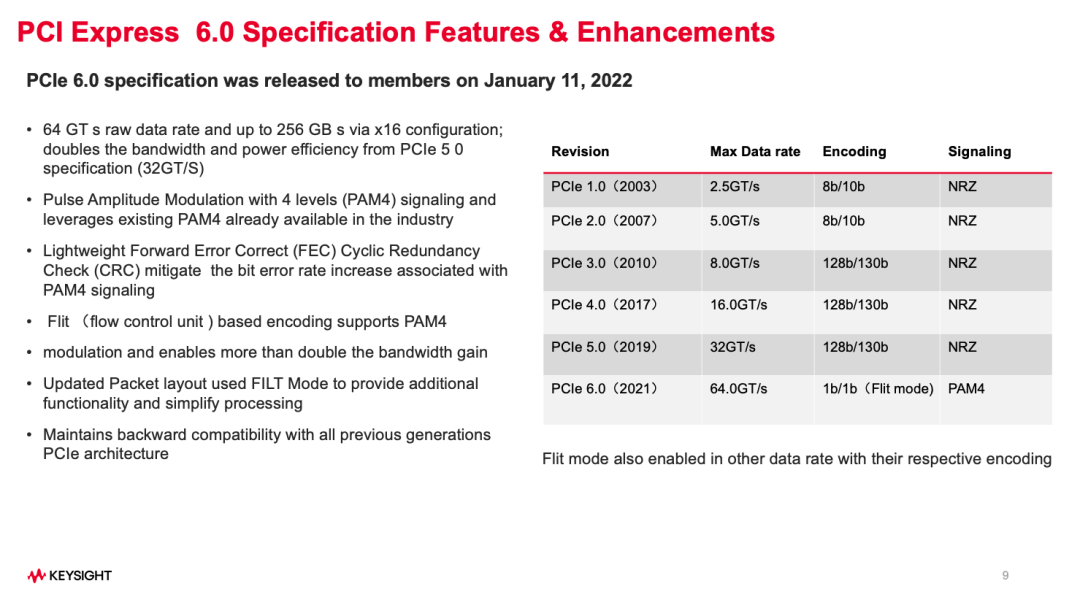

从正式发布至今,PCI Express(PCIe)发展迅速,已经成为高性能计算、人工智能/机器学习(ML)加速器、网络适配器和固态存储等应用不可或缺的一项技术。行业永不满足带宽需求促使PCIe的协议版本不断被刷新,2022年1月,PCI-SIG组织宣布PCIe 6.0规范标准v1.0版本正式发布,宣告完工。

•

数据速率从32GT/s翻倍至64GT/s

•

从NRZ编码转换到PAM4编码,可以在单个通道、同样时间内封包更多数据

•

从传输的可变大小TLP到固定大小FLIT,从而提高带宽效率,降低延时

•

LTSSM新增低功耗状态L0p

翻倍的64GT/s数据速率

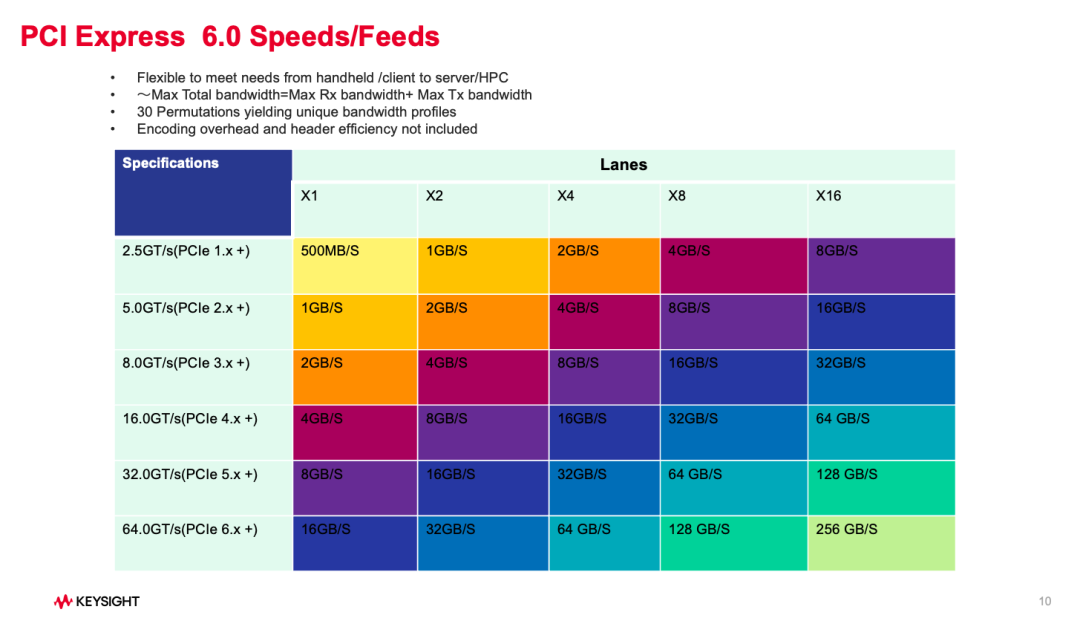

首当其冲的是,从5.0到6.0的数据速率翻倍递增,6.0支持64GT/s,16路双向传输带宽可达 256GB/s;对于数据速率翻倍的PCIe 6.0,如何保证系统性能变得尤为重要!PCIe的系统性能取决于RTT(Round-TripTime)及有效负载大小,简单来说就是工程师们需要确定系统所需的未处理、未发布请求的数量,从而来保证数据流的畅通。该数量转换为可用标签的数量,并且是必须根据系统需求正确设置的控制器属性。相较于PCIe 5.0的768标签数量,PCIe6.0对其的要求则变成了基于14位的15,360个标签数量,这样就满足了在RTT较长的情况下也能使系统整体保证高性能的工作状态。

首次采用高阶调制格式PAM4

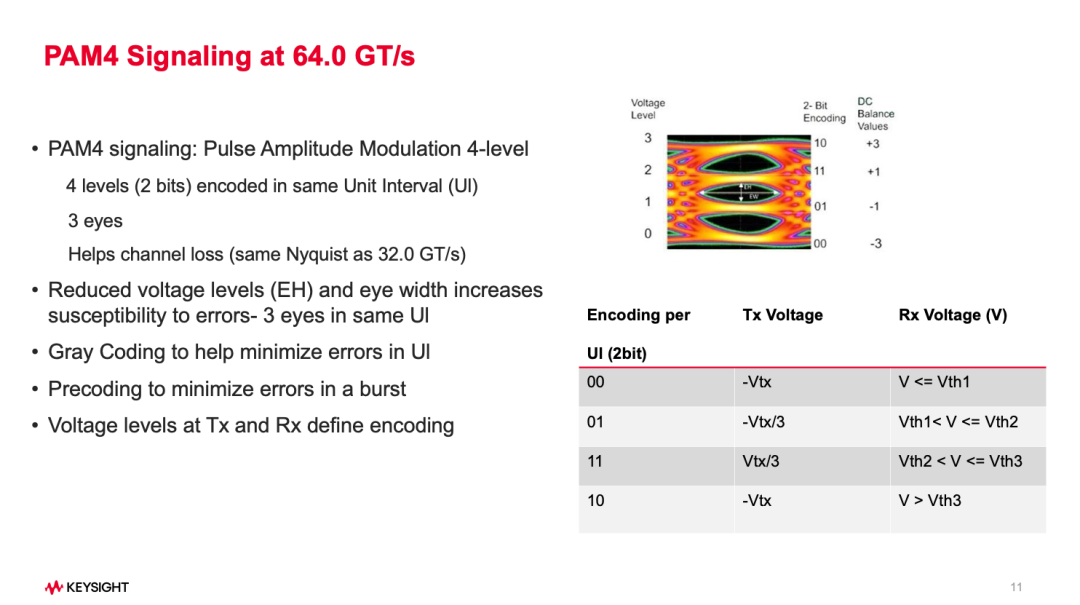

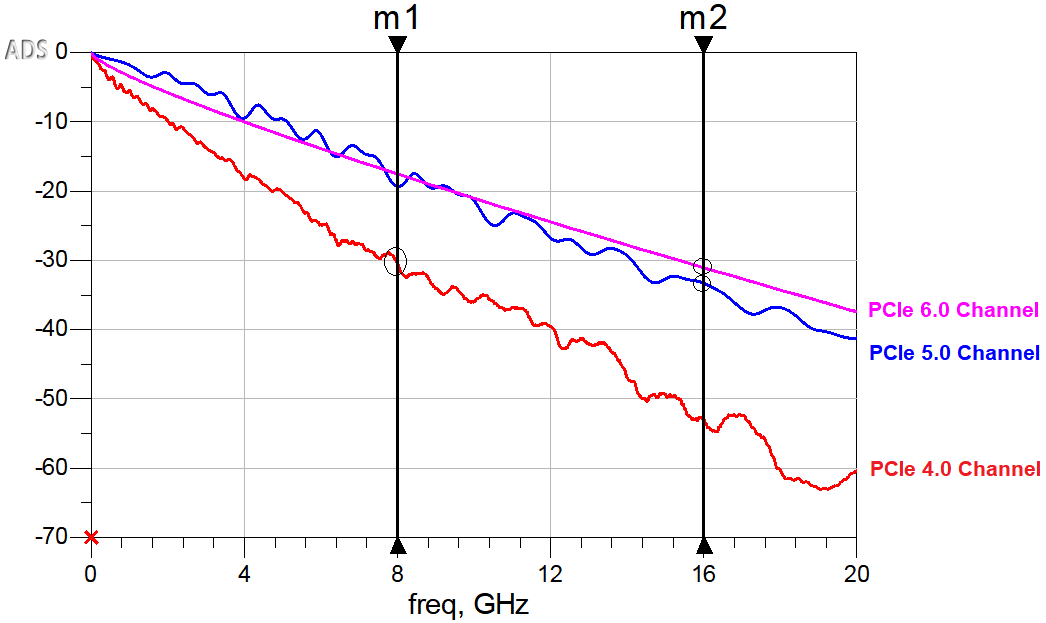

PCIe 5.0采用的32G NRZ编码已经使得Gen5的频率相关损耗比之前任意一代的频率损耗都要严重,假设PCIe 6.0 保留NRZ编码格式,那么它的通道损耗将达到60dB,这显然是不行的。所以新发布的PCIe 6.0采用高阶调制格式PAM4,这样的做法会使得在信号幅度相同的情况下信噪比天然会下降约9.5dB。但是这样的做法会使得系统对噪声更加敏感(比如电源噪声、串扰、反射等),为降低该影响,新版规范在综合考量了FBER、FIT、FLIT Retry 概率、带宽效率、Latency 及 FLIT 的 FEC 能力后,采用了轻量级FEC配合使用循环冗余码(CRC),那么这种做法就可以在降低噪声敏感性的基础上将FEC带给系统延迟控制在2ns之内。

FLIT模式

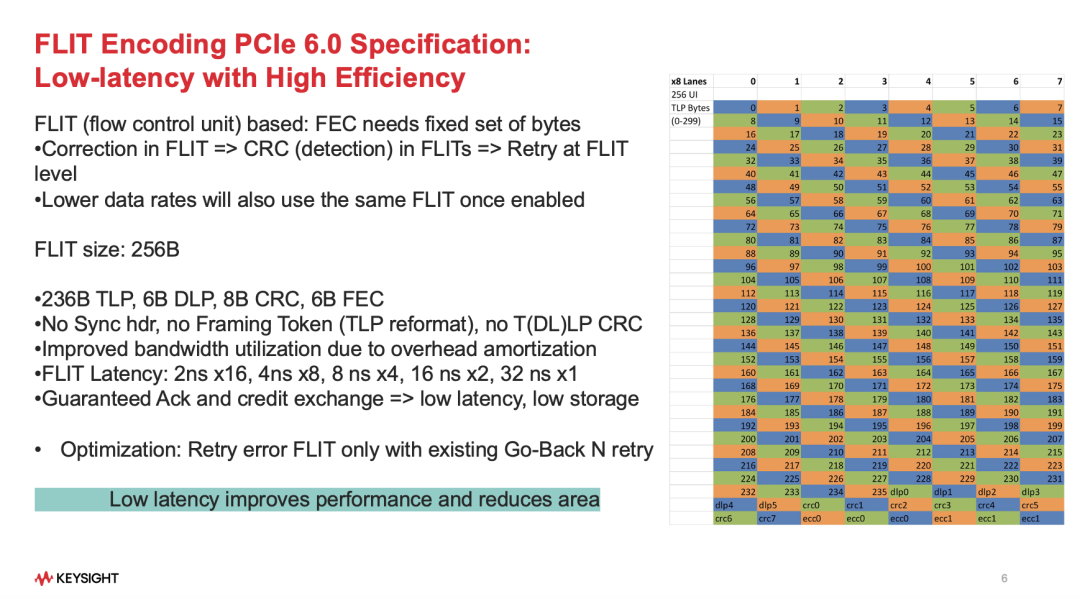

PCIe 6.0引入了FLIT模式(流量控制单元),也是PCIe 6.0标准最大的变化之一,与物理层的PAM4不同,FLIT编码用于逻辑层,将数据分解为固定大小的数据包。PCIe 6.0以FLIT为单位进行事务传输,每个FLIT有256 B数据(1 FLIT=236B TLP+6B DLP+8B CRC+6B FEC=256B),每B数据占用4 UI。以x8为例,一次FLIT传输的格式如下图所示。

最初引入FLIT模式的原因是纠错需要从而使用固定大小的数据包;然而,FLIT模式也简化了控制器级别的数据管理,随之而来的是更高的带宽效率、更低的延迟和更小的控制器占用空间。带宽效率:对于固定大小的包,不再需要物理层的包帧,这为每个包节省了4字节。FLIT编码还消除了以前PCIe规范的128B/130B编码和DLLP(数据链路层数据包)开销,从而显著提高了TLP(事务层数据包)效率。

FEC /CRC助力FBER

PCIE6.0规范定义了FBER是1E-6,那么为什么是1E-6呢?能否放宽至1E-4,满足PCIe 5.0通常的传输距离或IL目标呢?答案是否定的。参考以太网标准放宽至1E-4,需要使用复杂RS-FEC纠错,延时将增加到约100ns量级,这对负载和存储等对时延敏感的应用是一个很大的挑战。

为满足FBER=1E-6目标,PCIe 6.0引入轻量级FEC和鲁棒性强的CRC算法实现修正和错误检测。相比100G/400G以太网标准中经常用到的RS(544,514),该FEC实现相对简单,在固定包长度Flit模式下,6字节的FEC“保护”242字节Payload和8字节CRC,2字节1组实现FEC Group通过交织方式抵抗突发错误。如果FEC解码完成,但CRC仍检测到错误,那么接收侧会发送NAK启动重传,为提高效率,该模式下不会重传NOP-only TLP包。通过上述FEC、CRC适配FBER=1E-6要求,同时保证出错情况下重传概率在5E-6、带宽额外消耗约0.05%、FIT接近0。

互连通道与连接器

PCIe 5.0~6.0相比PCIe 1.0~4.0速率高,SI、PI要求也有提高。电源方面,插卡最大功耗可提升至600W,将在6.0 CEM中更新;信号方面为保证信号完整性要求使用表贴连接器;互连通道方面,与PCIe 5.0类似,要求主板支持约12 inch,插卡支持约3-4 inch,可以想象下,如果PCIe 6.0仍旧采用NRZ调制格式,64GT/s速率奈奎斯特频点在32GHz,那么通道IL将小于-60dB(参考下图通道仿真结果),很难通过现有技术实现该信号的高频补偿,考虑实现成本和技术复杂度,采用高阶调制PAM4是种不错选择,相比PCIe 5.0奈奎斯特频率不变,当前可用板材下可传输相似距离。

不同信道插损仿真图

PCIe6.0测试方案

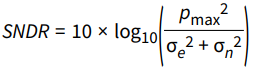

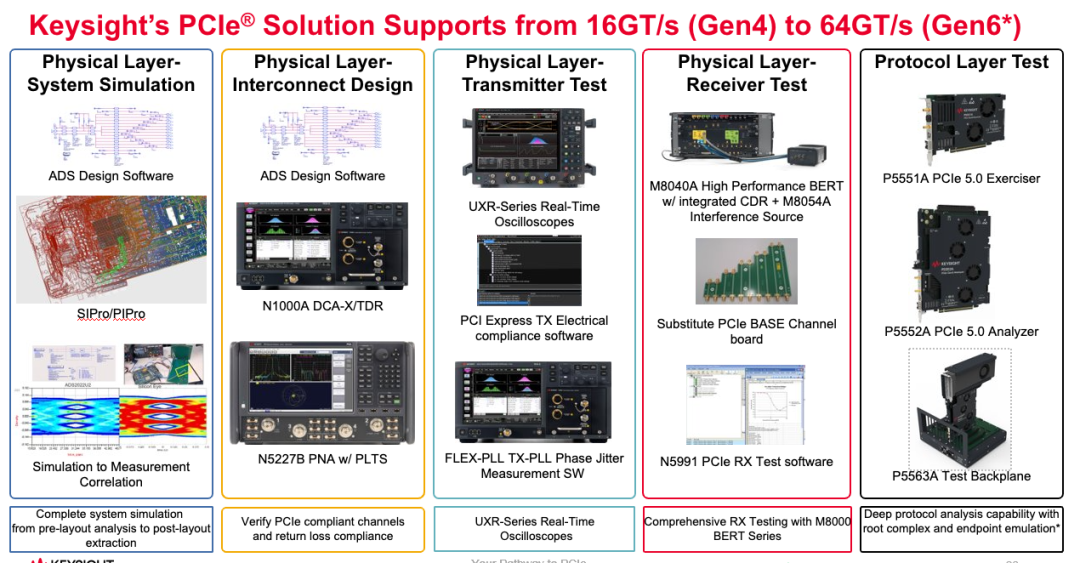

我们先来讲一讲物理层测试,PCIe 6.0采用PAM4的调制方式,与前一代采用NRZ的PCIe 5.0相比,规范对发射端测试增加了全新的测试方法和参数要求,包括SNDR(信噪失真比),RLM-TX(发射端电平等级失配率)和基于PAM4的非相关总抖动、确定性抖动;为此,PCIe 6.0 Base spec v1.0定义了新的64GT/s的一致性测试码型和抖动一致性测试码型,有几个要点需要注意:

1.

规范要求使用33GHz带宽Bessel-Thomason滤波器频响进行发射端一致性测试,对应示波器带宽至少为50GHz,这里推荐UXR0504A示波器。

2.

计算SNDR

计算线性拟合脉冲响应p(k)和矢量误差e(k),脉冲长度Np=600和脉冲延迟Dp=4,每个UI要有32个采样点,允许重采样,其中σn需要对一致性码型中的4个电平各自的64个长符号中第61个UI进行测量和统计平均,每个UI内需要统计8个采样点,等效为256GSa/s;

3.

测量需要考虑到示波器的底噪对测量结果影响,需移除示波器底噪对σn的贡献,这要求示波器软件能够对4个电平各自的示波器底噪计算并校准,提供最佳的测试精度。

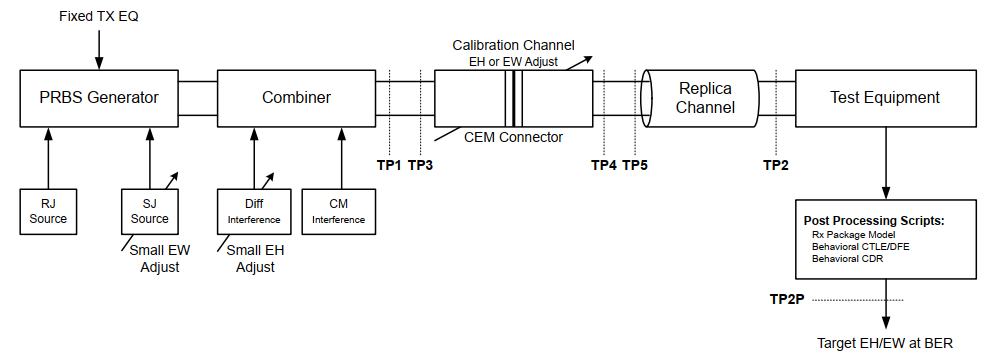

Keysight已经发布基于UXR示波器PCIe 6.0 Tx一致性测试软件SW00PCIE或包含协议解码功能的SW02PCIE,软件内已集成上述PCIe 6.0规范要求的测试参数和算法。下图为PCIe 6.0 Tx一致性测试软件SW00PCIE所覆盖的测试内容、功能和软件界面。

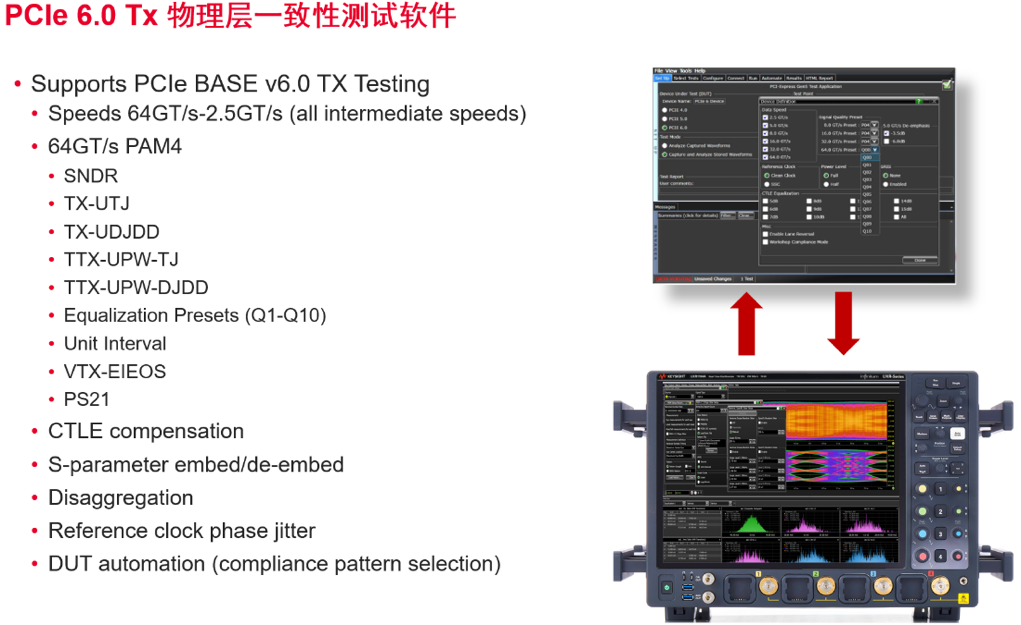

PCIe 6.0接收端一致性测试要求在如下图的组网环境下进行校准,TP3到TP2P链路损耗调整范围从30dB到33dB,从最大loss开始校准,Sj调整范围1到3ps,DMI调整范围5mv~25mV,目标Top Eye眼图眼高和眼宽(1e-6)分别为6 mV +/- 0.5 mV, 3.125 ps +/- 0.3 ps.

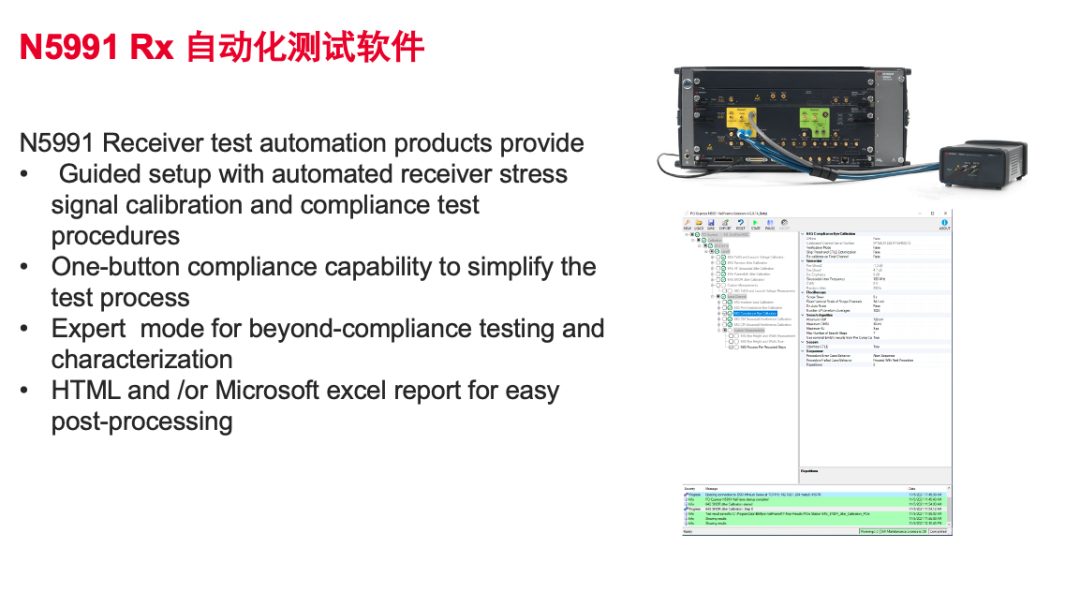

PCIe 6.0 Rx测试使用M8040A误码仪,它支持NRZ和PAM4信号产生和信号分析,可以向下兼容PCIe 1.1/2.0,对目前5.0 Rx测试的客户有很好的扩展性,可以通过软件许可的方式从NRZ升级PAM4选件支持PCIe 6.0,目前M8040A 分析仪模块也支持PCIe 6.0 LTSSM选件M8046-0N1,可与PCIe 6.0被测件实现链路协商,完成Rx/Tx LEQ测试,另外M8040A也支持PAM3信号生成,可实现对USB4 v.2的支持,除了硬件之外,也有包括丰富的软件方案支持对802.3CK、802.3BS以及CEI5.0/4.0的测试。N5991PB6A自动化软件可以实现PCIe 6.0自动校准和接收一致性测试。

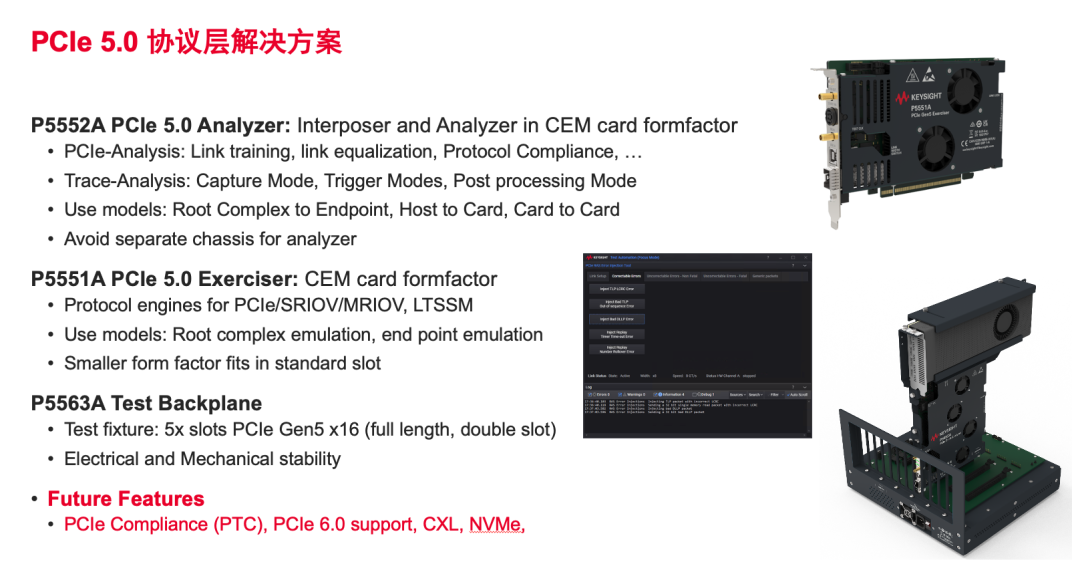

再来讲讲协议层的测试,芯片回片完成bring up,除基础规范和物理电气子层测试外,还需验证逻辑子层LTSSM链路状态机以及数据链路层、事务层等业务,这里需要使用协议分析仪或训练器。当前已经发布了支持PCIe 5.0的P5551A和P5552A的训练器和分析仪产品,由于PCIe 5.0和后续的6.0对于分析仪本身的信号完整性挑战非常高,P5552A协议分析仪创新性地将PCIe 5.0采集与处理硬件和Interposer设计为一体,无需一堆外部长线缆将信号传给主机处理,减少协议分析仪的欠补偿或过补偿问题。分析仪注重协议解析、链路监控及数据过滤等,训练器重点在于模拟对端EP或RC完成数据通信、支持注错和重播等,以及系统的RAS测试。未来也有计划通过升级支持PCIe 6.0、CXL、NVMe等协议。

最后总结一下,是德科技可以提供基于ADS仿真、PLTS信号测量、物理层收发、插卡环路带宽分析及协议分析等综合解决方案。

了解更多

更有好礼相送

保温杯雨伞套装

* 礼品图片仅供参考,请以实物为准。请在填写问卷时留下详细地址,如遇地址不详无法寄送,敬请谅解。

关于是德科技

点击“阅读原文”立即注册

原文标题:干货:PCIE6.0技术剖析

文章出处:【微信公众号:是德科技KEYSIGHT】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- 是德科技

-

楷登电子发布PCIe 6.0规范Cadence IP2021-10-26 5388

-

PCIe 6.0的新变化与新挑战2022-04-13 6764

-

PCIe 6.0规范及它是如何从过去的规范演变而来的2022-06-01 3511

-

如何破解PCIe 6.0带来的芯片设计新挑战?2023-01-19 1928

-

Samtec技术前沿 | 多重原因促使PCIe® 6.0采用了PAM42023-05-11 1571

-

PCIe 6.0入门之什么是 PCIe 6.02023-05-22 9710

-

PCIe6.0助力AI人工智能应用2023-07-06 3178

-

新思科技PCIe 6.0 IP与英特尔PCIe 6.0测试芯片实现互操作2023-10-12 1064

-

PCIe 6.0元年,AI与HPC迎来新速度2024-01-31 4386

-

下一代PCIe5.0 /6.0技术热潮趋势与测试挑战2024-03-06 3136

-

详解PCIe 6.0中的FLIT模式2025-02-27 4192

-

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!2025-09-07 8599

-

【PCIe 6.0 连载 · 上篇】64GT/s 时代来临:AI与算力爆发下的高速互联新基石2026-04-08 359

-

【PCIe 6.0 连载 · 中篇】从设计到实现:高速信号如何做到又快又稳?2026-04-15 97

-

【PCIe 6.0 连载 · 下篇】测试才是关键:PCIe 6.0 如何保证稳定量产?(行业干货)2026-04-22 602

全部0条评论

快来发表一下你的评论吧 !