FPGA数字IO如何实现DAC功能

描述

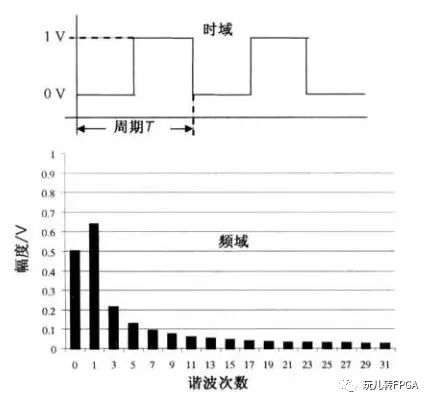

方波时域与频域

假设方波频率为f0。横轴谐波次数为0的柱状图代表直流分量的幅值,也就是方波的平均电压(与占空比有关),谐波次数为1代表频率为f0的正弦波分量的幅值,3代表,3*f0的正弦波分量幅值,以此类推。

可以看出,谐波只有奇数次的分量,1次谐波开始频率越高,幅值越低,对波形影响也就越小。

那么,此时如果此方波过一个低通滤波器,将1,3,5,7...次谐波通通滤掉会如何?

结果就会只有一个0次谐波,也就是0.5V(50%占空比)的直流分量。那么此时我们IO输出占空比变为40%,输出电压就是0.4V,占空比80%,输出就是0.8V,这不就实现了DAC的功能吗?

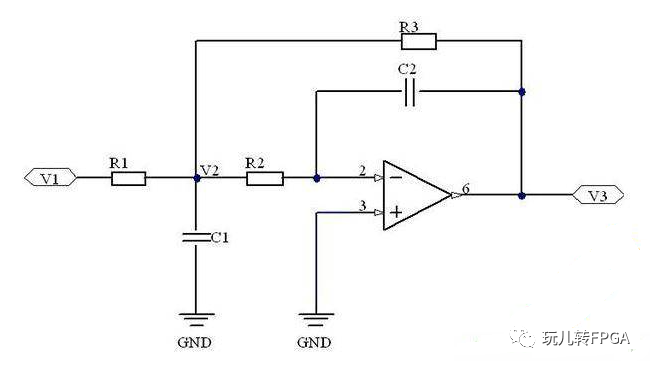

模拟滤波器

二阶有源低通滤波器

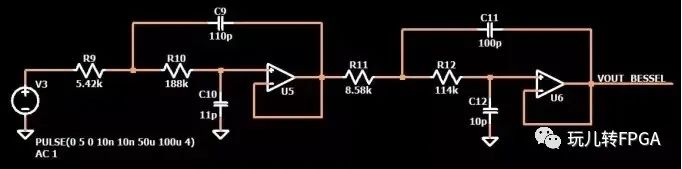

贝塞尔滤波器

除了上图的滤波器外,如果不追求精度,可以直接LC低通滤波器,简单实用,亲测有效。

Matlab分析方波频谱代码

fs=10000; %采样频率

t=0:1/fs:1;

x=square(2*pi*50*t); %信号波形

subplot(211);

plot(t,x);

subplot(212);

pspectrum(x); %显示功率谱密度

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC3161在应用中若要使用IO TEST该怎么用?2024-12-02 377

-

FPGA与传统DAC的比较2024-10-25 1319

-

请问FPGA数字IO如何实现DAC功能呢?2023-06-28 936

-

基于TXS0108实现FPGA IO Bank接不同外设IO接口电压转换2023-05-16 5392

-

请问CPLD或者FPGA能够实现任意的IO口对联吗?2023-04-23 3007

-

FPGA 结构分析 -IO 资源2022-12-13 3432

-

怎么实现基于FPGA的dac控制?2021-11-02 2697

-

FPGA设计中DAC控制的Verilog实现图文稿2021-07-26 1173

-

将Kintex 7 FPGA与CMOS输入DAC连接如何实现?2020-05-14 2441

-

如何设计基于FPGA的多功能数字钟?2019-11-11 3072

-

FPGA的IO2019-07-18 4395

-

基于FPGA和Quartus II的多功能数字钟设计与实现2012-12-18 40556

-

FPGA实现数字时钟2011-11-29 1594

全部0条评论

快来发表一下你的评论吧 !