SiP产品严格而规范的设计流程

描述

SiP 产品从设计到封装

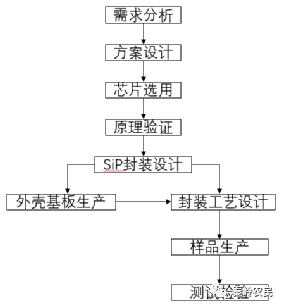

微系统产品的实现框图如图2.25所示,首先进行需求的分析,根据需求情况采用SiP技术对由裸芯片组成的微系统进行设计,根据SiP设计文件输出生产文件,投产陶瓷外壳,最后进行封装和组装工艺。

图2.25 SiP微系统封装设计验证过程

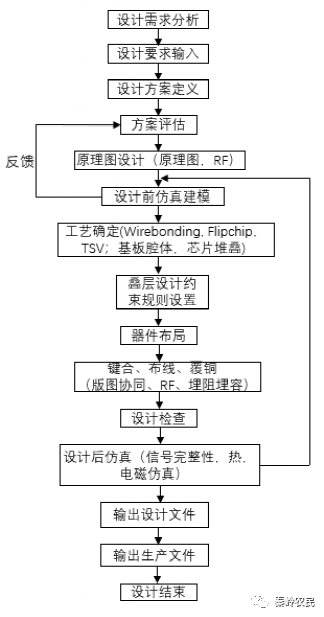

为了确保SiP项目能够取得成功,遵循严格而规范的设计流程是必不可少的。一款高密度系统级封装产品的设计往往需要在芯片布局、封装结构设计、基板设计、材料选择、先进封装制程之间寻找良好的平衡与解决方案。任何细小的环节都将影响系统级封装产品的成本、可制造性、性能与可靠性,考虑不周有可能导致产品开发延期和开发成本急剧上升,甚至导致产品报废。系统级设计封装流程如下图2.26。

图2.26系统级设计封装流程

1) 设计需求分析和设计要求的输入,需要就是要将产品的设计指标明确化,量化。确定系统封装产品的应用类型、性能要求等基本信息。

2)设计方案定义,主要包括:SiP相关资料收集、裸芯片物理尺寸、管脚定义、能否采购等。封装类型是采用BGA还是其他封装形式、封装尺寸的确定、管脚间距、数目的确定。采用自定义管脚排列方式还是采用标准封装。封装工艺和材料选择,根据其应用领域选择塑料封装、陶瓷封装或金属封装。以及可能存在的潜在风险。

3)设计前方案评估,主要是当所有的参数定义明确后进行方案的初步讨论和评估,将潜在的风险减小和量化以及想好解决方案。

4)原理图设计和仿真建模同步进行,通过假定分析 ,确定设计层叠结构、关键信号的网络拓扑结构、阻抗匹配,以及电源平面的分割、电容种类及型号选择等,并在设计过程中建立好仿真模型,对模型进行仿真验证。仿真验证包括对数模混合电路根据需要进行电路功能仿真,对机械与热进行的热应力仿真,对RF射频信号的电磁天线仿真,对光学信号的光路仿真等。

5)主要是为了确定 SiP 采用哪种工艺 ,如Wire Bonding、FlipChip、TAB、TSV等。基板上是否要挖腔体,采用单面腔体还是双面腔体,以及腔体结构等。同时要考虑是否做芯片堆叠 Chip stack,基板的层数以及层叠结构等通常在这一步要确定下来。

6)基板层叠设置,约束规则设置,根据工艺确定及设计复杂程度进行 SiP 基板层叠结构设置,包括层数以及层叠结构的选择,基板内部走线的设计,以及加工工艺的选择等。约束规则主要包括间距约束、差分线约束、信号线分类、高速信号约束。

7)器件布局,确定裸芯片在 SiP 封装中的位置。如果芯片需要放置到腔体里,则需要确定腔体的深度以及是单阶还是多阶腔体, 腔体形状的绘制和属性设置等;如果需要设计芯片堆叠,则堆叠芯片后再进行布局。

8)键合、贴装、布线、覆铜,根据芯片及元器件的排列选择适合的工艺,以及走线方式保证信号的连接。

9)设计检查,通常情况下设计完成后对整体设计对照checklist进行仔细检查,保证每一项设计需求都可以达到。并满足设计规则的约束。

10)设计后的仿真,设计完成后将版图设计数据导出到仿真工具,进行信号完整性、电源完整性、电磁场及热等方面的仿真。解决由于信号质量、供电不足、噪声等产生的问题,以及由于芯片功耗过大而发生的过热问题,确保产品工作的稳定和可靠性。仿真如果顺利通过,则进入到下一步,如果不能通过则需要回到前仿真,进行优化后重新设计和仿真。

11) 输出设计文件,将设计文件cad图纸,仿真结果等输出仿真报告。完成设计。

12)将设计文件结合生产设备与工艺进行输出生产可操作性文件。

13)设计结束。

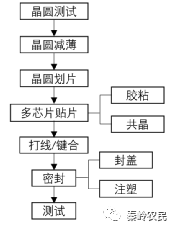

设计完成后就是封装和组装了,封装工艺包括清洗,贴片,焊接,绑线,封盖等

图2.27系统级封装流程

1)晶圆测试

就是对晶圆上每个芯片进行测试,测试每个芯片上凸点的电特性,不合格的芯片会标上记号并淘汰,以确保出产的每个芯片的正常功能和性能,也被称为中间测试(中测),目前应用最为广泛的晶圆测试是使用探针测试台等设备完成测试操作。

圆片探测是半导体制造过程中最后一道工艺。在这里对器件进行完整的测量。在晶圆制造完成之后的圆片被分切成封装管芯之前,对大晶片的每个芯片进行测试,以确定它的功能与性能。晶圆测试也就是芯片分选测试(die sort)或晶圆电测(wafer probe)。测试是为了3个目的:晶圆被送到封装厂之前,鉴别出合格芯片;对器件 / 电路的电性能参数进行特性评估;芯片的合格品与不良品的核算会给晶圆生产人员提供全面业绩的反馈。

2)芯片减薄技术

为了将2层甚至多层的芯片组装在一个高度小于或是更小的堆叠芯片封装体中,制造商致力于实现更薄的基板、更低的引线键合弧度、更低的塑封帽和更薄的芯片。芯片减薄技术是叠层裸芯片封装的关键技术。因为它降低了单个芯片封装高度,从而不会因为芯片叠加而增加系统的整体高度。

芯片减薄还可以提 高 散热效率、机械性能、电性能,减小封装体积,减轻划片加工量。减薄技术包括背面研磨、化学刻蚀和等离子体刻蚀。机械研磨是最普通的方法,就是从晶圆背部去除多余的硅材料。当前标准的晶圆减薄工艺(背部研磨和抛光)能将将厚度为300um的晶圆减至50um。甚至低于50um。

背部研磨通常会在晶圆表面留下微小缺陷。化学刻蚀和等离子体工艺可用于完成较低厚度的芯片减薄,且工艺过程对晶圆产生的应力较小。典型的减薄工艺流程是先背部减薄,接着采用湿刻蚀技术,可清除最后10~30um厚度的硅。

3)芯片贴片

芯片叠层是要求芯片在Z方向的叠加过程中实现高精度贴装,要保证芯片在贴装过程中尽量不产生漂移。芯片与芯片之间需采用绝缘胶粘接,而最底层的芯片直接和引线框架相接,所以可以用导电胶或者焊锡。芯片粘结工艺就有两种,胶水粘结和共晶焊接。胶水和共晶需要共同考虑的问题有粘接应力,导热,以及粘结温度曲线。

4)芯片密封

密封工艺是为了保护芯片保护器件不受外界环境的侵害,并提供足够的机械支持。就包括了塑封和管壳封装,管壳又包括陶瓷管壳和金属管壳。根据芯片工作环境和芯片性能选择合适的密封工艺。

审核编辑:刘清

-

生产电容器时流程不规范会有什么后果?2024-06-25 1133

-

SiP系统级封装设计仿真技术流程2024-04-26 848

-

浅谈硬件电路开发流程规范2023-08-03 2837

-

SIP协议的定义及基本流程2023-05-19 6965

-

sip网络可视对讲a181231365 2023-02-16

-

陶瓷封装SiP腔体结构介绍2023-02-10 6195

-

SIP立体封装器件手动装配规范2022-06-08 606

-

PCB工艺流程设计规范2021-06-07 3367

-

SiP的11个误区盘点2020-08-06 3138

-

硬件开发流程及规范2017-12-19 5281

-

SIP协议性能测试的方法2011-01-05 3458

-

SIP协议,什么是SIP协议2010-04-07 2585

-

3GPP R4版本为什么使用BICC协议而不是SIP-T?2009-06-13 3679

-

Cadence发布推动SiP IC设计主流化的EDA产品2008-06-27 7097

全部0条评论

快来发表一下你的评论吧 !