栅氧化层和多晶硅栅工艺示意图解析

制造/封装

540人已加入

描述

栅氧化层(Gate Oxide)和多晶硅栅 (Poly Gate)工艺

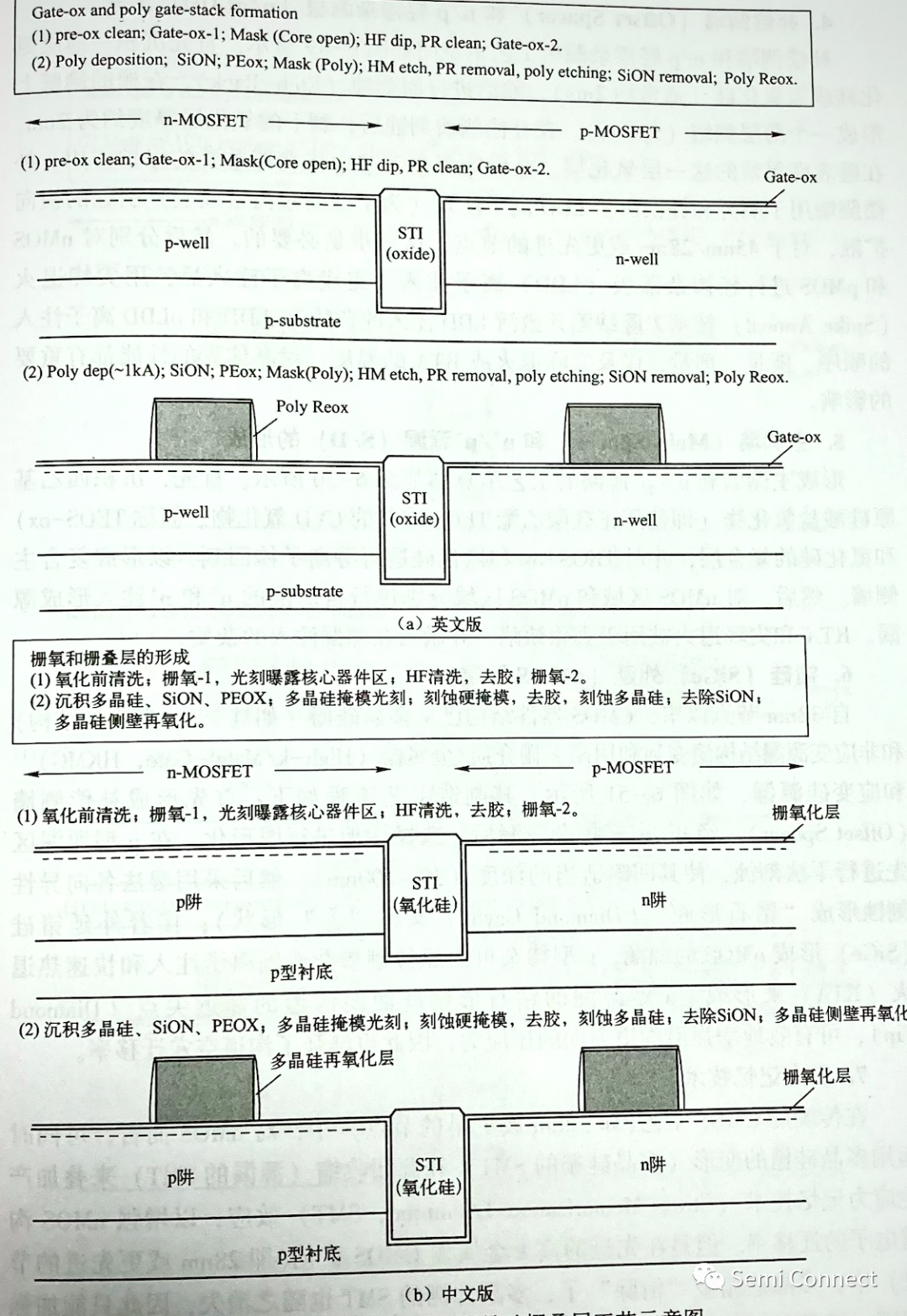

双层栅氧化层和多晶硅栅叠层工艺示意图如所示。

用湿法去掉牺牲氧化层后,通过热氧化生长第1层栅氧化层(Gate-ox-1,为了提高质量和降低内部缺陷),然后形成核心场效应晶体管区的掩模图形(使用掩模 “Core”曝露核心区域),接着浸入到HF溶液中,随后在核心场效应晶体管区通过热氧化的方式生长晶体管的第2层栅氧化层(Gate-ox-2)。注意,在I/O晶体管区(非核心区)经历了两次氧化,因此 I/O 晶体管的栅氧化层更厚一些。

当核心区域和 I/O 区域都已经生长晶体管后,沉积多晶硅层(Poly-Si)和硬掩模层(薄的SiON和PECVD二氧化硅)。沉积栅叠层(Cate-Stack)后,进行图形化硬掩模(经过光刻步骤)。去除光刻胶后,将SiON和二氧化硅作为硬掩模进行多晶硅刻蚀。去除SiON后,利用氧化炉或快速热氧化(RTO)形成多晶硅栅叠层侧壁的再氧化(小于3nm),以修补栅氧化物中的损伤和缺陷。因为栅的形状决定了场效应晶体管沟道的长度,即CMOS 场效应晶体管中的最小关键尺寸 (Critical Dimension,CD),因此栅叠层图形化通过硬掩模方案(而不是光刻胶图形化方案)会获得更好的分辨率和一致性。两次栅氧化的结果使得I/O场效应晶体管的栅氧层较厚而核心场效应晶体管的栅氧层较薄。

编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

评论(0)

发评论

-

jf_82261507

2024-06-03

0 回复 举报这本书能否推荐一下呢,谢谢啦 收起回复

jf_82261507

2024-06-03

0 回复 举报这本书能否推荐一下呢,谢谢啦 收起回复

-

为什么采用多晶硅作为栅极材料2025-02-08 1654

-

多晶硅栅工艺的制造流程2024-11-07 3158

-

栅氧化层工艺的制造流程2024-11-05 2790

-

多晶硅栅耗尽效应简述2024-08-02 7661

-

平面互补场效应晶体管替代金属栅工艺流程2023-01-17 4073

-

多晶硅栅(Poly-Si Gate)2022-11-17 9462

-

为什么多晶硅栅上还要再摞一层钨?不用不行吗?2012-01-12 5410

-

混合动力汽车示意图2009-11-21 2352

-

失会聚示意图2009-07-31 1326

-

飞机示意图2009-05-26 2566

-

电脑键盘示意图,计算机键盘示意图2009-03-10 128130

-

氯离子结构示意图和钠离子结构示意图2008-05-28 57088

全部0条评论

快来发表一下你的评论吧 !