如何管理约束文件?

描述

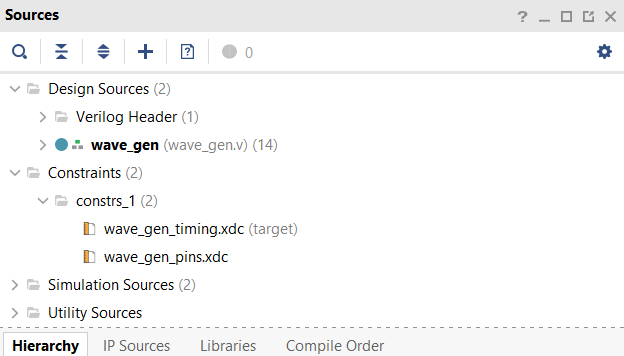

约束文件是FPGA设计中不可或缺的源文件。那么如何管理好约束文件呢? 到底设置几个约束文件? 通常情况下,设计中的约束包括时序约束和物理约束。前者包括时钟周期约束、输入/输出延迟约束、多周期路径约束和伪路径约束。后者包括管脚分配、管脚电平等。除此之外,有些情况下还包括用于设计调试的约束(设置ILA属性)或位置约束或通过Pblock执行的面积约束。Xilinx建议将约束分类写入不同的文件中,典型的场景是:时序约束放在一个文件里,物理约束放在一个文件里。如下图所示。图中wave_gen_timing.xdc中写的是时序约束,wave_gen_pins.xdc中写的是管脚分配。如果有ILA,可将ILA相关信息写入单独的文件中,这样的好处是当后期不再需要调试时,直接将该文件移除或点右键选择DisableFile,而不用一行行注释。

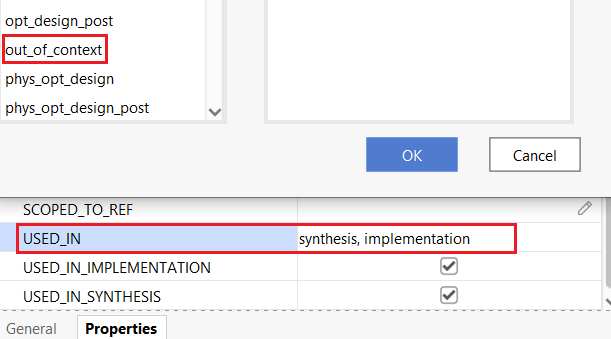

用于OOC综合的约束 Vivado支持对IP、BlockDesign进行OOC(Out-of-Context)综合。同时,Vivado还可对指定的用户模块进行OOC综合,这时可对该模块指定OOC综合时用到的约束文件。这可通过xdc文件属性USED_IN设定,将其值设置为{synthesis,out_of_context},如下图所示。

设置约束的生效阶段

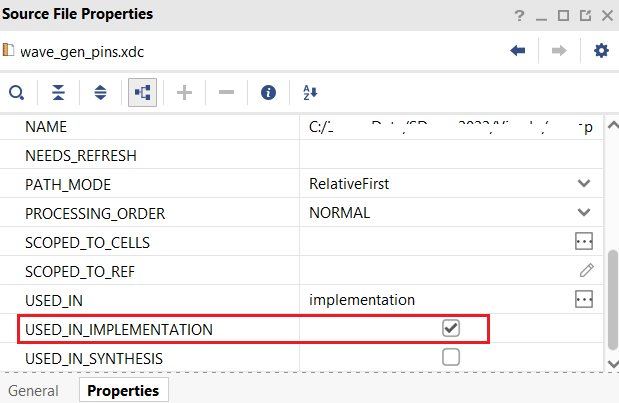

默认情况下,添加到Vivado工程中的xdc文件既用于综合阶段也用于布局布线阶段。但事实上,有些约束仅在布局布线阶段有效,例如管脚分配,这时可通过.xdc文件属性设定其使用阶段,如下图所示。

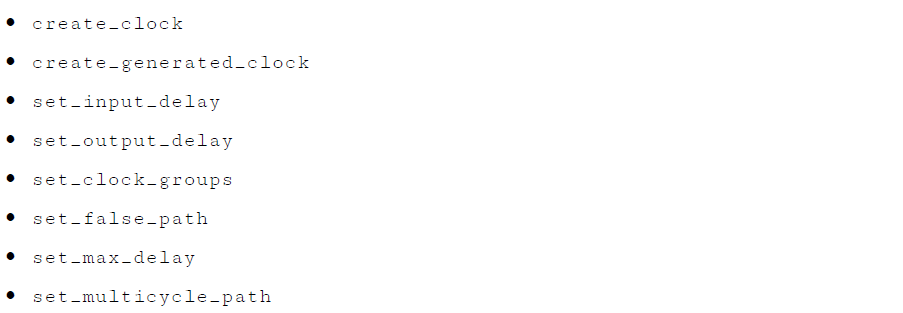

即使对于时序约束,也只有如下几条命令且与建立时间相关时综合阶段才起作用,这也是为什么我们在分析综合后的设计时只关注建立时间违例而忽略保持时间违例。

审核编辑:汤梓红

-

《EDA工具手册》约束管理器分册2017-11-10 4352

-

【FPGA学习】如何使用 ISE 编写约束文件2018-09-29 6384

-

PADS约束管理器不能用2019-04-11 1747

-

PADS约束管理使用指南2019-09-16 10314

-

请问时序约束文件SDC支持哪些约束?2023-08-11 785

-

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明2017-02-11 2105

-

如何为密集的高约束PCB设计创建和管理约束2019-05-17 3255

-

如何创建和管理约束密集型、高度约束的PCB设计2019-11-07 4034

-

PADS约束管理系统创建、审查和验证PCB设计约束2019-11-04 2747

-

易于使用的pads约束管理标准2019-11-01 2958

-

约束管理器节省设计时间2019-10-24 2757

-

Vivado IDE全面了解XDC文件的约束顺序2020-11-13 5947

-

Vivado中XDC文件的约束顺序2021-10-13 8262

-

Vivado设计约束功能概述2022-06-30 5791

-

约束管理器.zip2022-12-30 570

全部0条评论

快来发表一下你的评论吧 !