设计毫米波PCB需要考虑哪些必要因素

描述

在过去十年中,商业、工业、物联网、无线连接和一系列汽车雷达的应用已经发展到了毫米波(24-100GHz)。毫米波应用的这种快速增长创造了对带有毫米波电路的多层印制电路板(PCB)的需求。向毫米波的过渡给印制电路行业带来了许多挑战,主要是导体的几何形状和材料,因为较短的波长缩小了特征尺寸,放大了PCB制造过程中固有的相对容差。

控制生产成本可能是一项复杂的工程挑战。成本必须从一开始就被纳入电气设计中,因为材料、基材结构和PCB技术都是在这里确定的。像所有好的工程一样,目标是设计一个满足所有性能要求的产品,并有较高的产量,考虑到所有材料和制造容差,结果是在成本和性能之间进行平衡。

最后,在毫米波频率下,将信号传导到不同的层是一个难题。关于材料特性和制造方面的难题,我们展示了一个为毫米波PCB应用形成各种通孔结构的例子。我们介绍了一种简化通孔形成的表面安装交叉组件,它有几个额外的优点:它有利于快速改变结构,将信号传导到不同的层,解决对电气性能的影响。

PCB制造的挑战

毫米波的波长与PCB的几何尺寸是同一数量级的。成本是另一个增加设计复杂性的因素,因为许多新的毫米波产品是用于消费类应用,其基材生产量从几万到几百万件不等。

在其最简单的形式中,印制电路是使用照片成像和化学蚀刻工艺制造的。这是通过在铜箔层压板或多层层压板上钻电路孔实现的。钻孔后,面板被电镀,在钻孔和表面上形成铜层,大约有50微米的厚度。接下来,在表面涂上光阻剂,通过光罩用紫外线照射成像,并进行显影,以暴露出不需要的铜。暴露的铜被化学蚀刻,留下一个成品电路。

蚀刻到电介质也会横向蚀刻到导体的侧面,使该工艺一般不适合射频/微波应用。电镀铜和基片都必须被蚀刻以形成导体,从而导致不良的几何形状和不太理想的导体容差。

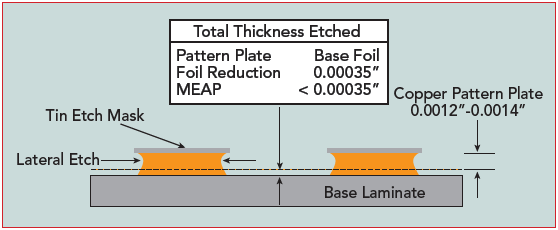

为了克服面板电镀的问题,大多数电路的制作采用了"图案电镀工艺"。不对整个面板表面进行电镀,而是在基础铜箔上施加光阻。然后,使用光罩或激光直接成像,将电路图案转移到抗蚀剂涂层的面板上。在成像和显影之后,基底铜箔上暴露的区域将被电镀,形成一个电路图案,铜也在钻孔中。为了保护电路图案和孔壁不受最后的蚀刻影响,锡被镀在电路图案的上面。接下来,光阻剂被剥离,背景铜箔被蚀刻,接着是锡条,产生一个成品电路。与面板电镀相比,图案电镀工艺提供了更好的几何形状和更严格的容差,因为只有底层箔需要进行化学蚀刻,最大限度地减少了改变导体侧壁的横向蚀刻(图1)。

图1 箔片削减和高级箔片削减工艺的侧向蚀刻厚度。

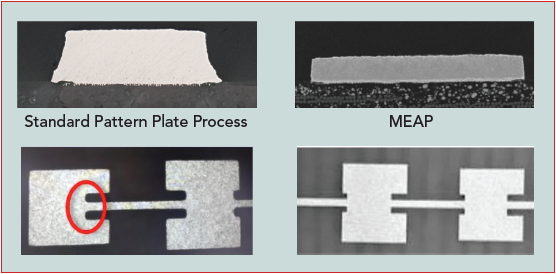

工作频率为60-100GHz的毫米波结构需要改进天线贴片和嵌入馈线的导体容差和角半径。为了实现更严格的蚀刻容差,已经引入了几种技术:首先是通过化学研磨减少关键层的基础铜箔厚度。基础铜箔被减少到不到18微米,这减少了蚀刻时间并改善了导体的几何形状,最大限度地减少了对导体侧壁的蚀刻和蚀刻补偿。第二种方法是改良的蚀刻添加剂工艺(MEAP),它能实现更严格的容差和更高的分辨率。与铝箔还原工艺非常相似,MEAP利用了更薄的基底铜,然而,它使用先进的蚀刻技术,在蚀刻后产生极其均匀的铜几何形状(图2)。

图2 标准图案电镀工艺和MEAP。

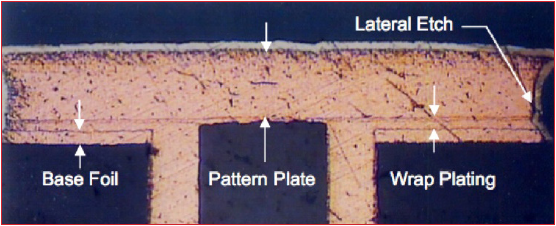

另一个经常被忽视的因素是,由于更复杂的通孔结构,额外的铜箔厚度对导体的几何形状和容差都有影响。大多数先进的PCB结构不仅仅包括通孔。还有盲孔、埋孔、微孔和"焊盘上的孔"(VIPPO),这些都使电镀工艺复杂化。为了创造可靠的通孔,铜箔必须从电路图案表面沿着孔壁向下电镀,然后再回到表面。被称为"包裹式电镀",铜镀层是连续的。由于所有三个表面都是同时电镀的,所以默认情况下,通孔会发生包覆电镀。盲孔和VIPPO的情况则不同。根据IPC-6012规范,面板电镀需要满足每个包覆电镀周期的最小厚度为5微米(图3)。

图3VIPPO与包覆电镀的对比。

在毫米波结构中,几乎总是有一个或多个深度的VIPPO和/或盲孔。对仿真模型的影响是,基片现在有一个额外的铜镀层厚度,每个包覆周期至少5微米。额外的铜层厚度会影响导体的分辨率以及电气结构的容差。例如,增加VIPPO会增加一个包覆电镀周期,两个盲孔深度会增加两个包覆电镀周期,等等。这必须在设计过程中尽早解决。

为了保持准确的尺寸容差和克服铜的厚度变化,引入了第三种工艺。这种工艺是图案电镀和简单的铝箔印刷和蚀刻之间的一种混合。对于贴片天线和滤波变压器等电路图像来说,其概念是简单明了的:它们在基础铜箔上拍照成像,通常是18微米或更薄,然后进行蚀刻。蚀刻后的部分没有被电镀,具有纯铜箔蚀刻

审核编辑:郭婷

-

毫米波雷达方案对比2018-08-04 12394

-

毫米波频段PCB材料关键参数和特性的理解2019-05-18 5540

-

毫米波的PCB平面传输线技术2019-06-24 4273

-

毫米波技术的发展进程2019-07-03 3019

-

汽车毫米波雷达传感器的性能一致性2019-07-29 6097

-

毫米波雷达是什么?2019-08-02 4635

-

毫米波雷达(一)2019-12-16 14879

-

毫米波是什么2021-01-28 2468

-

毫米波雷达的特点是什么2021-07-30 7315

-

毫米波技术基础2022-07-29 2707

-

激光开槽技术在毫米波产品中的应用2009-10-06 671

-

影响汽车毫米波雷达传感器的性能及因素2020-07-15 1603

-

毫米波应用的电路材料应该如何选择2020-11-06 1067

-

使用毫米波需要注意什么问题?应该如何选择合适如何选择毫米波的处理2020-10-06 8276

-

奕叶最新毫米波PCB测试站2023-08-24 1525

全部0条评论

快来发表一下你的评论吧 !