下一代软件定义无线电收发器在跳频方面取得巨大进步

描述

本文深入讨论了跳频(FH)的高级概念、通过ADRV9002 SDR收发器的灵活锁相环(PLL)架构实现的跳频设计原理及其四个主要跳频特性。这些功能使用户能够使用跳频功能来处理Link 16等应用,并在单通道和双通道操作模式下实现快速实时载波频率加载。此外,跳频与多芯片同步(MCS)和数字预失真(DPD)的结合使这款SDR收发器成为满足当今复杂通信系统高级要求的有吸引力的解决方案。

介绍

与传统无线电通信相比,跳频(FH)定义了通过快速改变其载波频率来传输无线电信号的方法。1尼古拉·特斯拉(Nikola Tesla)在他1903年的美国专利“信号方法”中首次提到。后来,在1942年,女演员海蒂·拉玛(Hedy Lamarr)和作曲家乔治·安泰尔(George Antheil)通过使用钢琴卷在88个频率之间切换以防止干扰鱼雷的无线电控制,进一步巩固了这一概念。近百年来,从第一次世界大战中固定指挥点之间的非实时、慢速通信,到飞机、轮船、陆基系统之间的实时、高速多媒体通信,FH在军事应用上已经进入了一个新的时代。除此之外,FH已广泛应用于许多无线个人通信网络,如蓝牙个人局域网(PAN),以及消费者和业余无线电领域,如对讲机、模型车和无人机。®

什么是跳频?

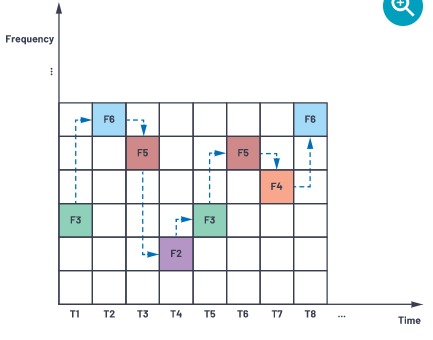

FH的高级概念如图1所示。整个频段和持续时间被划分为二维网格。在任何给定的时隙,使用不同的频率子带进行通信。这带来了对窄带干扰的高抵抗力和强大的抗恶意拦截和干扰能力的好处,因为跳频模式的随机性等效地增加了另一层安全性,该安全层只能在发射器和接收器之间解码。此外,由于相互干扰最小,跳频信号可以轻松地与其他传统通信共享带宽,从而实现高频谱效率。随着跳频速率的提高和子频段的增大,跳频的优势变得更加突出,这使其成为许多不同应用的有吸引力的解决方案。

图1.跳频的高级概念。

下一代 SDR 收发器

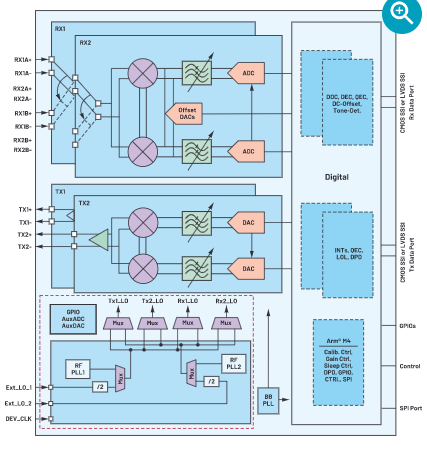

ADRV9002是一款双通道窄带和宽带SDR收发器,提供先进的RF性能以及DPD和FH等高级系统功能。ADRV9002的工作频率范围为30 MHz至6 GHz,涵盖超高频(UHF)频段;甚高频 (VHF) 频段;工业、科学和医疗 (ISM) 频段;以及窄带 (kHz) 和高达 40 MHz 的宽带操作的蜂窝频段。 图2显示了ADRV9002的高级框图。它包括具有一组高级数字信号处理算法的双发射和接收通道。以红色突出显示的PLL结构是独一无二的,因为器件中采用了两个RF PLL,而不是像许多其他收发器那样为接收数据路径提供一个专用PLL,为发射数据路径提供一个专用PLL,并且两个PLL都可以选择提供任何接收器或发射器,或两者兼而有之,或者两者都不提供。这种灵活性对于在各种TDD应用中支持跳频至关重要,例如单通道和双通道操作,包括仅发送模式(1T/2T)、仅接收模式(1R/2R)以及发射和接收模式(1T1R/2T2R)。双通道操作支持通道分集和通道多路复用。此外,两个PLL可以在乒乓模式下运行,以满足严格的跳频定时要求。

图2.采用灵活PLL设计的ADRV9002高级框图

ADRV9002的四大跳频特性

具有两个 PLL 复用和快速 PLL 重整的超快速跳频

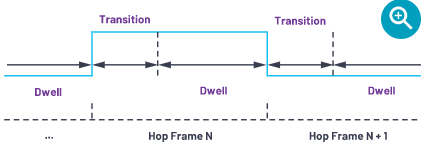

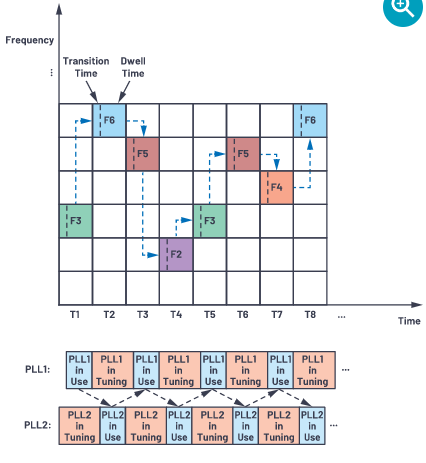

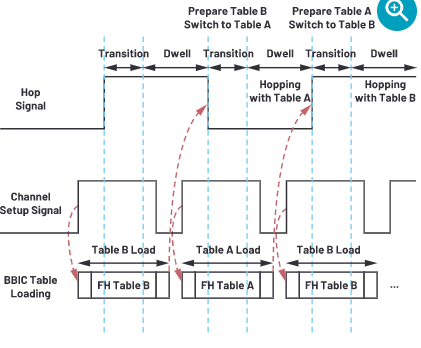

跳频是通过在切换到不同频率之前重新调谐PLL来实现的。ADRV9002根据PLL使用情况提供不同的跳频模式。2图 1 中的每个时隙代表一个跳帧,该帧分为转换时间段和停留时间段,如图 3 所示。

图3.跳帧结构。

在频率变化之间转换时间足够长(大于通道建立时间和所需的PLL调谐时间)较慢的跳频模式下,TDD操作(PLL重调谐模式)中的一对发射和接收通道只需要一个PLL。为了以更短的转换时间(比通道建立时间和所需的PLL调谐时间短)实现更快的跳频,器件中采用了两个PLL(PLL多路复用模式)。两个PLL以乒乓方式相互协调:一个PLL用于当前频率,另一个PLL重新调谐到下一个频率。这使得非常快速的跳频成为可能,并且可以显着减少不同频率变化之间所需的转换时间。表1总结了这两种模式。

| 跳频模式 | 过渡时间 | 用于一对通道的 PLL | 允许的 PLL 重整定时间 |

| 锁相环多路复用器 | <锁相环再调谐时间 | 两个相环 | <两个过渡 + 一个停留 |

| 锁相环重整定 | >PLL重整定时间 | 一个锁相环 | <一次过渡 |

如表1所示,这两种模式的选择取决于用户定义的转换时间。

图4进一步描述了PLL多路复用模式的概念。如前所述,每个时隙代表一个由转换时间段和停留时间段组成的跳帧。当一个PLL在停留期间使用时,另一个PLL从同一跳帧的转换时间开始调谐。它可以继续调谐,直到下一跳帧的过渡期结束。因此,只要所需的PLL调谐时间小于一个停留时间加上两个转换时间的总和,PLL多路复用模式就是成功的。

图4.用于快速跳频的PLL多路复用模式。

带PLL多路复用器模式的跳频对于Link 16等军事应用至关重要。Link 16被认为是北大西洋公约组织(NATO)使用的最重要的战术数据链路标准之一,是一种抗干扰的高速数字数据链路,工作在960 MHz至1.215 GHz的无线电频段3。 通过在初始化时正确校准整个跳频范围,ADRV9002采用快速PLL重调模式来满足严格的时序要求。PLL重整定时间取决于ADRV9002 PLL参考时钟速率。表2显示了基于不同PLL参考时钟速率所需的快速PLL重整定时间。在300 MHz的PLL参考时钟速率下,快速PLL重整定时间约为15 μs。当链路16的跳帧长度为13 μs时,使用PLL多路复用模式时,如果转换时间大于2 μs,则15 μs的PLL重整定时间可以满足时序要求,如表1所示。

| 锁相环参考时钟 (兆赫) | 快速锁相环再调谐时间(μs) |

| 30 | 91 |

| 38.4 | 77 |

| 50 | 56 |

| 100 | 27 |

| 150 | 21 |

| 200 | 20 |

| 250 | 17 |

| 300 | 15 |

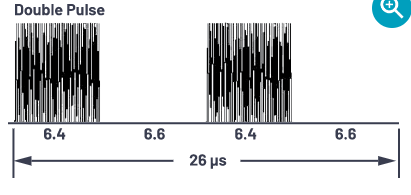

如论文“存在窄带干扰的情况下通过慢速平坦的中上衰落信道传输的JTIDS / Link 16型波形的性能分析”中所述。3Link 16 消息数据可以作为单脉冲或双脉冲发送,具体取决于包装结构。单脉冲结构由6.4 μs导通时间和6.6 μs关断时间组成,总持续时间为13 μs。双脉冲结构由两个单脉冲组成,它们携带相同的数据,但使用不同的载波频率,如图5所示。因此,转换时间可能长达6.6 μs(>2 μs),这使得ADRV9002的Link 16 FH可行。

图5.标准链路16双脉冲结构。

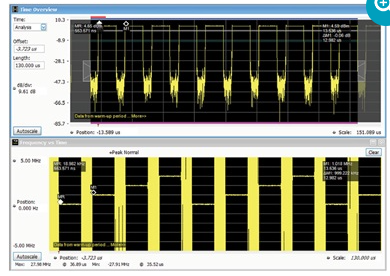

图6显示了ADRV9002的发射输出(功率与时间和频率与时间的关系),采用Link 16型跳帧(为简单起见,使用仅发送跳频)。请注意,为了显示ADRV9002可实现的最小转换时间,本实验不遵循图5中的标准Link 16脉冲结构。导通时间从6.4 μs增加到11 μs,关断时间从6.6 μs减少到2 μs。泰克RSA306B频谱分析仪连接到ADRV9002评估板上的发射输出端口进行观察。上图显示了功率与时间的关系。可以看出,发射跳频每13 μs发生一次,连续发射跳帧之间的转换时间约为3 μs。下图显示了频率与时间的关系。在本实验中,发射载波频率以1 MHz的步长循环通过四个不同的频率。正如预期的那样,下图证明发射输出也以1 MHz的步长循环通过四个不同的频率,在整个驻留时间内具有良好的频率精度。

图6.链路 16 Tx 跳频的传输输出。

使用是德科技 E5052B 和 R&S FSWP 等更先进的测试设备进行进一步的测量,以研究 Link 16 FH 的频率精度。在表3所示的示例测量中,发射载波频率在400 MHz、400.1 MHz、400.2 MHz和400.3 MHz处跳频。发射输入旨在为所有跳帧产生 400 MHz 输出。测量持续时间设置为 100 μs,其中包括七个完整的跳帧。频率每128 ns时间间隔测量一次。可以观察到,PLL在停留时间开始时完全锁定。驻留期间的频率误差取决于相位噪声性能。表 3 显示了这连续 7 个跳帧的平均、最大和最小频率偏移(输出频率与 400 MHz 之间的绝对差值)性能。在大多数帧中,平均频率误差小于1 ppm。结果也可用于数十次测量。请注意,测量值可能因设备和测试配置而异。

| 跳帧编号 | 平均频率误差(赫兹) | 最大频率误差(赫兹) | 最小频率误差 (Hz) |

| 1 | 348 | 730 | 46 |

| 2 | 424 | 997 | 4 |

| 3 | 267 | 563 | 20 |

| 4 | 327 | 892 | 7 |

| 5 | 253 | 569 | 2 |

| 6 | 394 | 903 | 12 |

| 7 | 253 | 677 | 17 |

ADRV9002为用户提供微调PLL环路滤波器带宽的功能。表3所示的性能是在PLL环路滤波器带宽配置为1200 kHz时实现的。更大的PLL滤波器带宽改善了PLL重整定时间,从而保证了PLL在驻留时间开始之前完全锁定。选择环路滤波器带宽时,用户还应评估其应用所需的相位噪声性能。

静态和动态工作台加载多达 128 个不同频率的条目

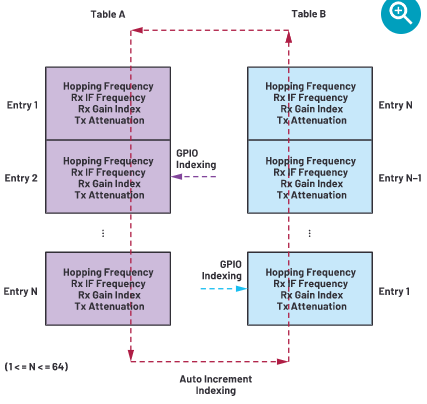

ADRV9002采用跳频表概念适用于所有跳频模式。2 跳频表包含每个跳帧的频率和其他操作参数列表。跃点表可以是静态的,这意味着它在初始化期间加载,不允许即时更改。它也可以是动态的,这意味着它在执行跳跃时加载;在这种情况下,用户可以即时更改表内容。采用了类似的乒乓球概念,以便用户可以选择加载两个不同的表,每个表最少 1 个到最多 64 个条目。当一个表用于当前跃点帧时,正在加载另一个表以准备下一个跃点帧。每个条目都会通知ADRV9002特定跳帧的配置。可以通过自动递增索引(从第一个表的第一个条目开始到第二个表的最后一个条目,然后使用两个跳表再次返回到第一个表的第一个条目或使用一个跃点表连续循环)或通过数字 GPIO 指示的任何时间访问特定条目来索引跃点表。

图 7 显示了跃点表 A 和 B,每个都有 N 个条目(1 ≤ N ≤ 64)。表中的每个条目都包含四个关键参数:跳频、中频(仅适用于接收IF模式)、接收增益指数和发射衰减。在TDD操作中,用户必须使用专用通道设置信号(每个发射通道一个,每个接收通道一个)通知ADRV9002每个跳帧启用哪个通道(发送或接收)。因此,尽管跳表中的每个条目都包含用于接收和发送的参数,但仅使用相关参数。

图7.ADRV9002跳表内容和索引方法。

在进一步讨论跳频中的跳频工作之前,有必要了解ADRV9002与基带集成电路(BBIC)之间的高级通信。

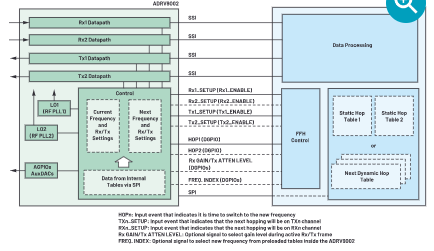

如图8所示,BBIC充当跳频操作的主要器件,用于设置跳频模式、通道设置信号(Rx1_ENBALE、Rx2_ENABLE、Tx1_ENABLE和Tx2_ENABLE)、跳频信号(HOP1和HOP2)以及静态或动态跳频表(跳频、接收IF频率、接收增益和发射衰减)。BBIC通过SPI接口或DGPIO与ADRV9002通信。ADRV9002通过接受来自BBIC的信号来充当跳频的节点,然后相应地配置数据路径和LO。

图8.ADRV9002和BBIC在跳频期间通信的高级框图。

图 9 描述了一个动态表加载示例,每个跳表 A 和 B 只有一个频率。这是一种极端情况,允许用户在每一帧中即时更改跳频。本例使用PLL多路复用模式。如图8所示,跳频信号的上升沿和下降沿都定义了跳帧的时序边界,每个时序边界由转换时间和停留时间组成,如前所述。通道设置信号上升沿定义了遵循一帧延迟的跳帧类型(此延迟对于PLL多路复用模式是必需的)。

图9.使用PLL多路复用模式对每个表一个频率进行动态表加载的示例。

请注意,通道设置信号可以代表发射设置信号或接收设置信号。图9显示了该信号的简化版本。由于TDD操作涉及发送和接收,因此用户需要分别配置发送设置信号和接收设置信号。除了指示跳帧类型外,通道设置信号还可用于触发由BBIC启动的跳表加载。跳频表加载应在通道设置信号下降沿之后的跳频信号边沿之前完成,然后PLL在同一跳边沿开始调谐到此频率,并为下一个跳频边沿发出的下一个跳帧做好准备。表 A 和表 B 以乒乓模式运行,因此,在加载完成后,FH 在一个表的频率上工作,同时调谐另一个表的频率。

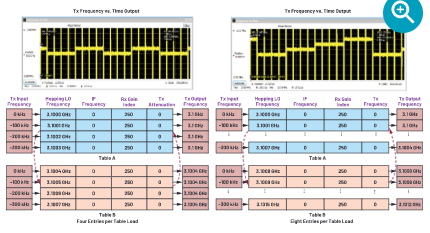

图10显示了每个负载4个条目和每个负载8个条目的动态表加载的发射频率与时间输出的关系。发射输入具有0 kHz、–100 kHz、–200 kHz和–300 kHz频率的四个帧,通过连续循环帧馈送到ADRV9002。它还与跳帧完全对齐和同步,因此 0 kHz 输入帧与 3.1 GHz LO 对齐。在跳频期间,当LO变为下一个频率时,发射输入频率也会变为下一个频率。

图 10.动态表加载的比较,每次加载四个条目和每次加载八个条目。

表 A 和表 B 在执行 FH 时动态加载(为简单和易于观察,表内容不会随加载而变化)。对于每个负载的四个条目,我们期望在 3.1 GHz 时看到四个连续的发射输出帧,然后在 3.1004 GHz 处看到四个连续的帧,并且相同的模式会一次又一次地重复。对于每个负载的八个条目,我们期望在 3.1 GHz 时看到四个连续的发射输出帧,在 3.1004 GHz 下看到四个连续帧,在 3.1008 Hz 下看到四个连续帧,在 3.1012 GHz 下看到四个连续帧,并且相同的模式一次又一次地重复。图8所示的传输输出证明动态表加载按预期工作。

通道分集与使用双通道的通道多路复用

如图2所示,ADRV9002支持双发送和接收通道。跳频可以应用于两个通道,以实现通道分集或通道多路复用。

为了实现分集,两个通道使用相同的PLL(一个或两个)以及相同的跳频表和TDD定时配置同时跳频。ADRV9002提供的MCS功能可以启用,以确保相同或不同ADRV9002器件上的多个通道彼此完全同步,并具有确定性的延迟。相位同步也可以通过MCS实现,每次PLL重新调谐频率时都会执行MCS。借助MCS,即使在跳频期间,多个通道也可以实现同步,这使得ADRV9002成为涉及跳频的MIMO分集应用的极具吸引力的解决方案。有关在跳频期间使用MCS的要求和限制的更详细说明,请参阅ADRV9001系统开发用户指南。2

对于通道多路复用,每对通道使用一个PLL,并彼此独立地执行跳频。一个限制是,一对发射和接收通道需要两个PLL的超快速跳频无法应用于一个ADRV9002器件的通道多路复用。

除了2T2R模式外,值得一提的是,ADRV9002还支持跳频的1T2R和2T1R操作,这为满足用户的特定要求提供了更大的灵活性。

支持跳频设备操作

ADRV9002还支持窄带和宽带应用的DPD操作。它校正功率放大器(PA)的非线性,以显著提高PA效率,同时实现符合标准的相邻通道功率泄漏比(ACPR)性能。

ADRV9002的一个高级特性是DPD可以与跳频一起执行。在这种情况下,ADRV9002允许用户配置多达8个频率区域,DPD算法为每个频率区域创建最佳解决方案。DPD解决方案作为一组系数也可以分别在每个区域的传输结束和开始时存储和加载。这确保了整个跳频范围内的PA线性度。

由于DPD是一种自适应滤波过程,必须定期捕获一组样本以进行系数计算,因此跳帧长度需要足够长以满足DPD捕获长度要求。但是,如果用户仅使用初始加载的DPD系数而不需要DPD更新,则可以删除此限制。

ADRV9002跟踪校准通常在快速跳频期间不执行。但是,初始校准是根据用户的跳频配置基于多个频率区域执行的,以实现最佳性能。

使用ADRV9002收发器评估软件(TES)进行跳频性能评估

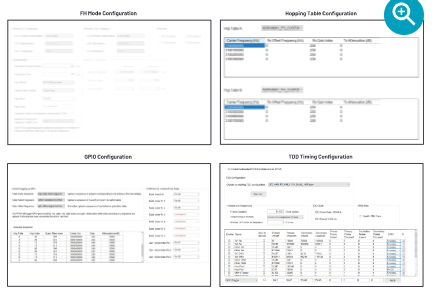

跳频性能可通过ADRV9002 TES和评估板进行全面评估。赛灵思 ZC706 和 ZCU102 FPGA 板均受 TES 支持。®2如图 11 所示,跳频配置页易于用于配置 FH 参数,包括跳频操作模式、跳频表、GPIO 设置、TDD 时序等。TES内置FPGA同步功能,允许用户精确控制TDD时序,以便发送或接收帧可以与跳帧完全同步。TES中还提供了许多跳频示例,供用户进一步探索。

图 11.通过 TES 配置 FH。

结论

跳频是下一代SDR收发器ADRV9002提供的高级系统功能之一。ADRV9002具有两个PLL、多种跳频模式以及加载和索引跳频表的灵活性,使用户能够处理各种应用并满足高级系统要求。所有特性均可通过ADRV9002 TES和软件开发套件(SDK)进行全面评估。

-

下一代SDR收发器中的黑魔法:发射本振泄漏!“零中频”的挑战如何破?2017-09-11 12044

-

下一代SDR收发器,所用算法是重要方面2017-09-18 11178

-

提供显著跳频(FH)优势的下一代软件定义无线电收发器2021-12-08 7346

-

基于软件无线电的高速QPSK调制器的设计与实现2017-08-02 2544

-

全面了解基于射频捷变频收发器AD9361的软件定义无线电解决方案2018-10-22 3408

-

射频转换器为下一代无线基站提供高效的多波段无线电2018-12-13 3972

-

双向射频收发器NCV53480在下一代RKE中的应用是什么2021-05-20 1744

-

什么是软件无线电?2022-04-15 13140

-

基于软件无线电的自适应跳频系统研究2010-08-09 689

-

基于软件无线电跳频电台射频前端研究2011-06-08 1096

-

软件定义无线电的应用2017-09-15 1027

-

下一代软件定义无线电收发器在跳频方面取得了巨大进步2022-12-12 2688

-

提供显著跳频(FH)优势的下一代软件定义无线电(SDR)收发器2023-06-15 3230

-

基于软件无线电跳频电台射频前端的研究2023-10-26 552

-

RF转换器为下一代无线基站提供多频段无线电2023-11-23 507

全部0条评论

快来发表一下你的评论吧 !