FPGA学习-Verilog例化说明

描述

Verilog例化说明

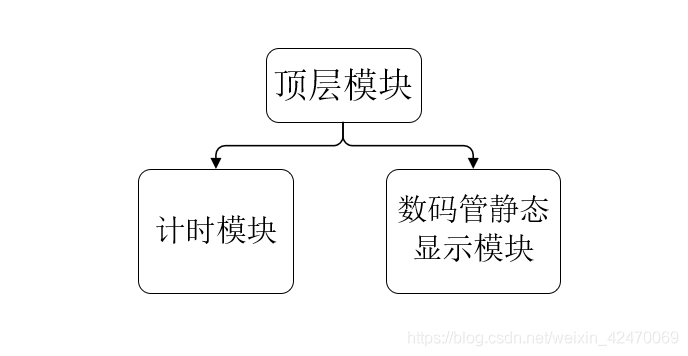

1.什么是模块例化?为什么要例化?

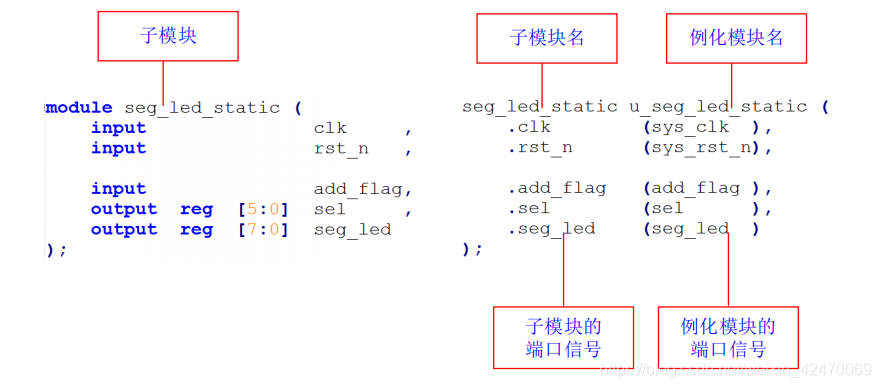

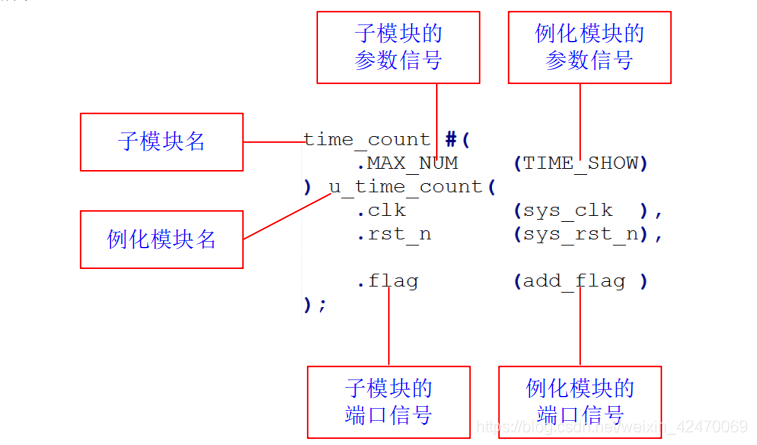

2.实例说明例化方法

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-Verilog例化说明

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- FPGA

-

Verilog例化说明2024-12-17 3808

-

Verilog HDL程序设计案例2023-02-13 831

-

FPGA设计硬件语言Verilog中的参数化2022-12-26 1476

-

FPGA的Verilog学习教程课件免费下载2021-01-21 1284

-

FPGA的视频教程之Verilog模块的基本构成要素资料说明2019-03-26 1315

-

FPGA视频教程之学习FPGA选择verilog还是vhdl详细资料说明2019-03-22 1778

-

FPGA视频教程之Verilog基础的详细资料说明2019-03-21 1428

-

FPGA视频教程之Verilog语法基础的详细资料说明2019-03-01 1974

-

例说FPGA连载62:电子点菜单之FIFO例化说明2016-12-26 4974

-

FPGA_Verilog学习资料part42016-03-14 647

-

数字电路中的FPGA和verilog教程2016-01-18 736

-

学fpga的verilog语言怎么模块化2013-11-21 2052

全部0条评论

快来发表一下你的评论吧 !