基于T35F324的FPGA开发板图像采集显示系统方案

可编程逻辑

描述

1.前言

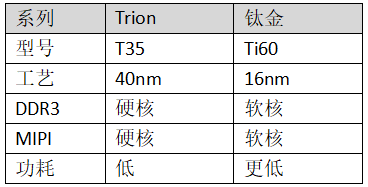

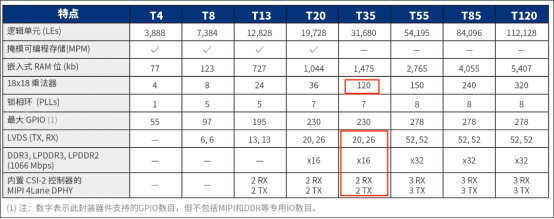

个人觉得易灵思的Trion系列比钛金系列FPGA,就目前而言,更适合做图像显示相关应用,以T35和Ti60为例,主要原因如下表所示:

易灵思如果专注图像细分领域,毕竟大部分客户还是用DDR和MIPI,因此我觉得钛金系列的架构真的脑袋被驴踢了,DDR和MIPI用硬核才是正确的选择!

另外,钛金系列FPGA相对推出时间不够,目前IP也不成熟。以T35为例,DDR硬核IP在Efinity Interface中直接可以调用DDR IP并设定相关参数,但是钛金系列Ti60还没有包含到工具链中,这让拿不到一手资源的FPGAer就很尴尬,虽然可以理解不集成到IDE中,可以更快的迭代前提不成熟的版本。

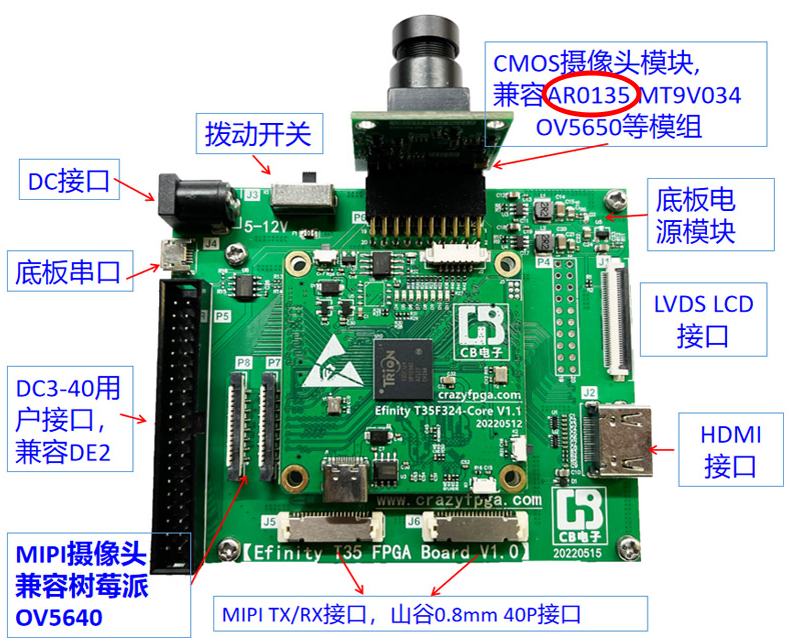

如上图所示,T35F324的FPGA开发板,我都做了快半年了,一直没有做一个基于视频图像的像样点的Demo,甚是惭愧。为了给当下煎熬的大家送点福利,我打算分2步走,如下:

DVP相机+DDR3+LVDS-LCD实时显示系统

MIPI相机+DDR3+LVDS-LCD实时显示系统

前者更关注DDR3硬核、LVDS TX,以及进行并口相机的配置与图像采集,完成实时图像采集、缓存、显示系统;后者则借用1)的基础,更关注MIPI相机的开发,进一步把易灵思FPGA进行图像采集的优势,发挥一下。

当然这过程肯定还是有不少的坑,有些坑只有自己趟过,才有发言权。

2.FPGA设计详解

言归正传,我们开始干正事:基于T35的摄像头采集、存储、显示系统的介绍。

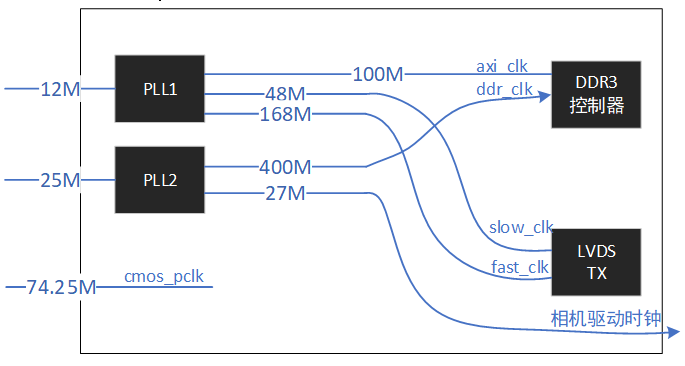

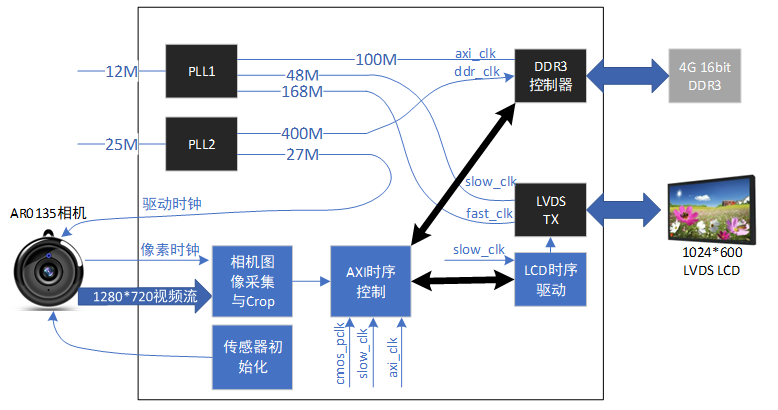

首先是FPGA时钟网络

这里涉及到DDR控制器的时钟,LVDS TX的快慢时钟,系统时钟,以及外设驱动时钟等,大致示意图如下:

由于Trion的PLL是能输出3个时钟,因此将2个PLL都用上了,一个产生100MHz的系统时钟,48/168M的LVDS慢/快时钟,另一个PLL产生DDR的驱动时钟400MHz,以及外部传感器的驱动时钟27MHz。另外,还有一个从传感器输入的像素时钟74.25MHz,作为视频流的同步时钟。

其次是硬核的配置

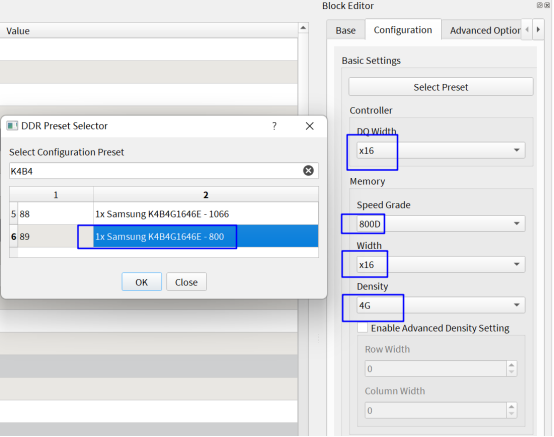

这里用到了DDR与LVDS TX硬核。关于DDR硬核的使用,外部使用的是三星的K4B4G1646E-BYMA,4G 16bit容量。

在Interface中配置DDR控制器相关参数,如下图所示:

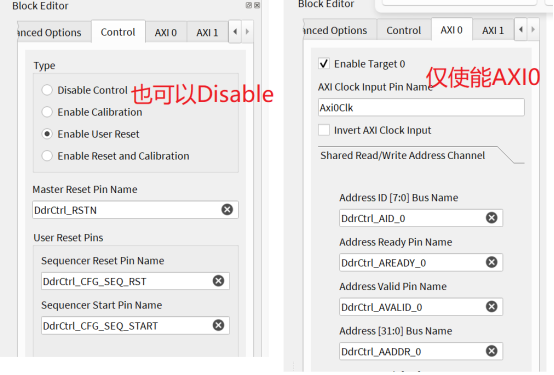

其实软件包含了颗粒的型号,因此配置还是挺简单的,对于用户接口,Interface提供的是标准的AXI接口,其他的都是在硬核中,用户不需要例化,非常的简单。

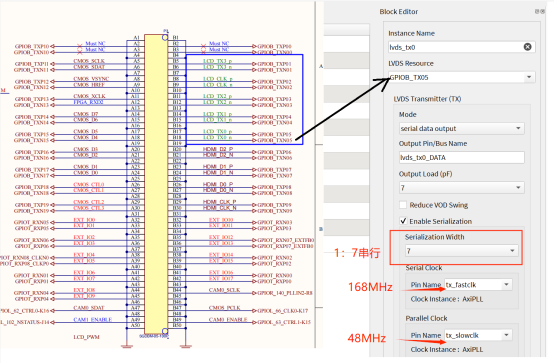

关于LVDS TX的使用,主要是PORT的配置,以TX0为例,Interface配置如下图所示:

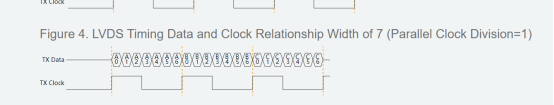

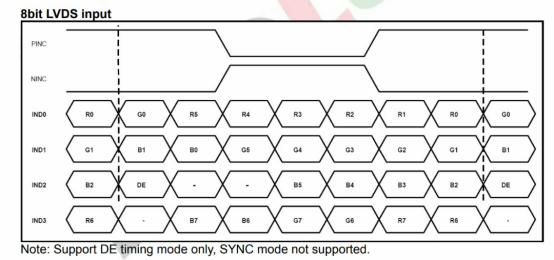

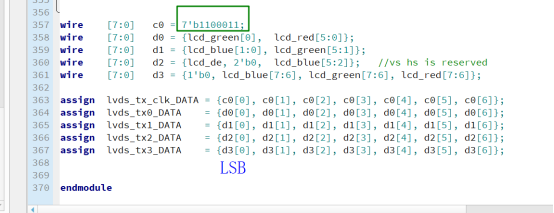

这里特别需要注意的是,PLL1设置tx_fastclk时,需要90度响铃;另外,Efinity的LVDS是LSB的,也就是先发LSB,这在Interface的说明文档中有解释,如下图所示:

另外,在1024*600 LVDS手册中,LVDS时钟有一定的相位关系,如下所示,在7bit数据传输时,时钟为1100011:

所以如上这部分代码,如下所示:

接着是相机的驱动

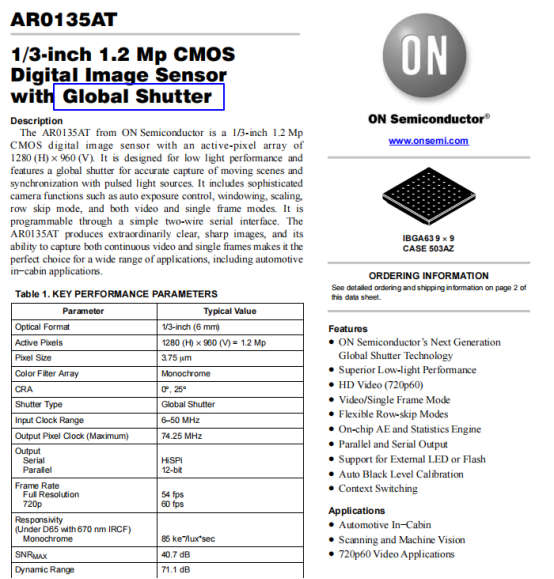

目前采用的AR0135是车规常用的130万全局曝光黑白相机,成像质量非常好,相关的参数如下所示:

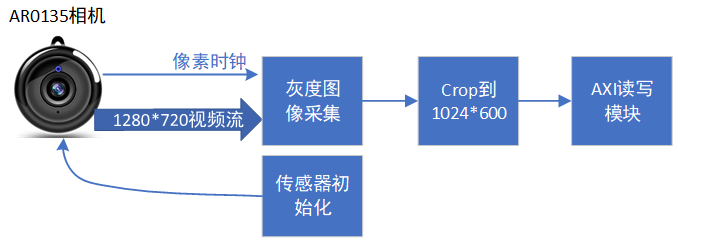

我曾在《FPGA设计技巧与案例开发详解》一书中详细介绍了如何使用FPGA驱动CMOS摄像头,因此这里不再描述细节,给出框图如下:

这里在进行相机的初始化后,捕获输入的并行视频流数据;另外为了适配后面1024*600的LVDS LCD,再捕获数据后,直接Crop到1024*600分辨率。接着将数据送入AXI读写模块,将DVP转成AXI后写入DDR。

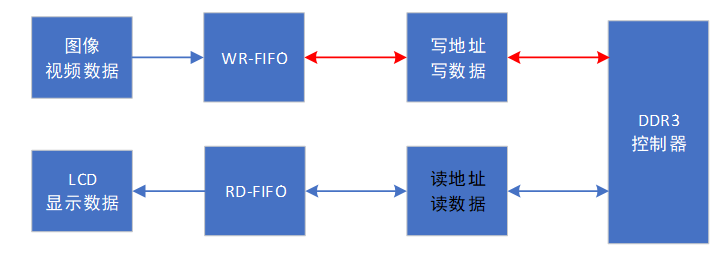

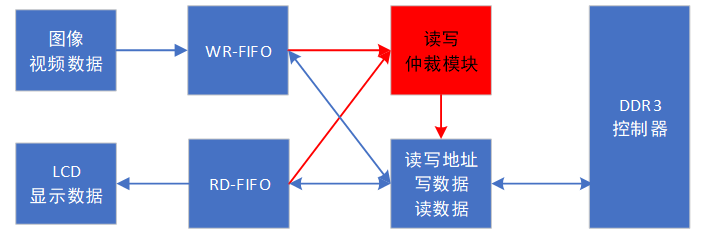

最后是视频流的缓存与显示

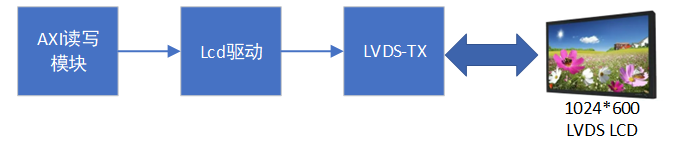

这一步其实和相机的数据缓存比较类似,无非是用一样的时序反着走一遍:即采用AXI从DDR中读取数据,转成并口后,送给后续的LCD驱动模块,再通过LVDS送给LCD显示,框图如下所示:

最后,汇总整个时钟、DDR、相机、LCD驱动显示的框图,基于T35的摄像头采集、存储、显示系统,如下图所示:

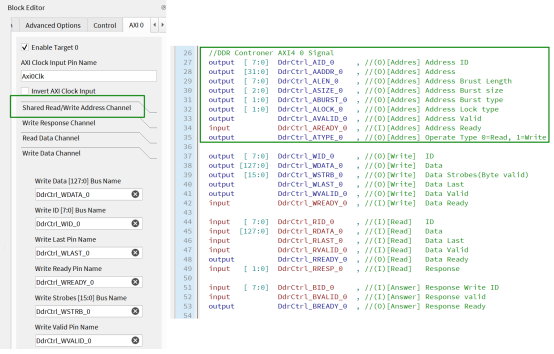

由于该趟的坑,都已经趟过一遍了,这里我们不得不再静下心来再分析讨论一下,这个设计中遇到的最大的坑——DDR3的AXI接口竟然是Shared Read/Write Address Channel,配置与接口代码如下所示:

那就意味着,虽然AXI可以做到读写通道独立,但我不能同时发起读命令与写命令。如果AXI读写通道是完全独立的,则我们可以这样设计,即读归读,写归写,设计相对简单。

但是现在竟然AXI的读写地址通道是shared,我被惊讶到了,毕竟做了七八年芯片,AXI也是手撸过很多遍,Shared地址通过的阉割版,还是有点不适应,毕竟当读写冲突的时候,必须做仲裁,同时也需要更大的FIFO,还缓存读写通道的数据。

3.总结

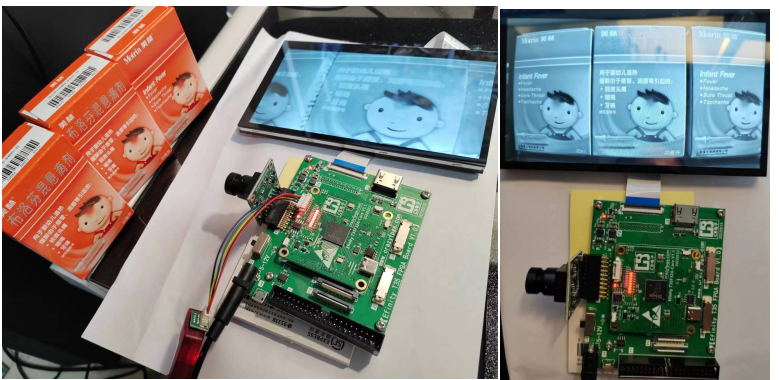

花了九牛二虎之力,搞定了1280*720@60Hz的AR0135采集,然后裁剪成1024*600后,与1024*600的LCD显示数据仲裁读写DDR(加入读写仲裁,且读数据优先,),最后得到的效果是这样的:

这里,我还是不解,易灵思的DDR控制器,如果是买的,那Synopsys应该是标准的AXI;或者如果是买的DDR PHY+自研的控制器,那应该至少遵循标准,为什么会出一个阉割版本的AXI接口呢?

百思不得其解,但这也无法阻碍我们前进。在不久的将来,我将写基于易灵思FPGA的MIPI相机采集显示开发详解。

编辑:黄飞

-

fpga开发板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T开发板用户手册-学习板2025-10-14 452

-

STM32F103C8T6开发板最小系统原理图2025-03-24 5463

-

基于FPGA的图像采集与显示系统设计2024-07-17 3366

-

fpga开发板是什么?fpga开发板有哪些?2024-03-14 4434

-

fpga开发板与linux开发板区别2024-02-01 3992

-

基于紫光同创FPGA的图像采集及AI加速(盘古50K开发板)2023-11-03 1365

-

全志T3+Logos FPGA开发板——双屏异显开发案例2023-03-31 3426

-

FPGA开发板EP4CE22F17C8原理图及封装2021-08-10 3985

-

基于STM32F103C8T6开发板控制的OLED显示2021-06-03 2876

-

通过Arty Artix-35T FPGA开发板创建mig IP2020-12-16 2568

-

基于Zedboard FPGA的VGA图像信号采集系统的设计2017-11-18 2584

-

开发板ep1c3t144fpGAdevelopboard2017-03-20 1525

-

【Artix-7 50T FPGA申请】以太网图像传输验证系统2016-10-11 2330

-

fpga开发板电路图2012-04-19 2484

全部0条评论

快来发表一下你的评论吧 !