й«ҳеҺӢж …жһҒй©ұеҠЁ IC иҮӘдёҫз”өи·Ҝзҡ„и®ҫи®ЎдёҺеә”з”ЁжҢҮеҚ—

жҸҸиҝ°

В

В В В В В ВВ

В д»Ӣз»Қ

В ВВ

жң¬ж–Үи®Іиҝ°дәҶдёҖз§Қиҝҗз”ЁеҠҹзҺҮеһӢMOSFETе’ҢIGBTи®ҫи®Ўй«ҳжҖ§иғҪиҮӘдёҫејҸж …жһҒй©ұеҠЁз”өи·Ҝзҡ„зі»з»ҹж–№жі•пјҢйҖӮз”ЁдәҺй«ҳйў‘зҺҮпјҢеӨ§еҠҹзҺҮеҸҠй«ҳж•ҲзҺҮзҡ„ејҖе…іеә”з”ЁеңәеҗҲгҖӮдёҚеҗҢз»ҸйӘҢзҡ„з”өеҠӣз”өеӯҗе·ҘзЁӢеёҲ们йғҪиғҪд»ҺдёӯиҺ·зӣҠгҖӮеңЁеӨ§еӨҡж•°ејҖе…іеә”з”ЁдёӯпјҢејҖе…іеҠҹиҖ—дё»иҰҒеҸ–еҶідәҺејҖе…ійҖҹеәҰгҖӮеӣ жӯӨпјҢеҜ№дәҺз»қеӨ§йғЁеҲҶжң¬ж–Үйҳҗиҝ°зҡ„еӨ§еҠҹзҺҮејҖе…іеә”з”ЁпјҢејҖе…ізү№жҖ§жҳҜйқһеёёйҮҚиҰҒзҡ„гҖӮ

В

иҮӘдёҫејҸз”өжәҗжҳҜдёҖз§ҚдҪҝз”ЁжңҖдёәе№ҝжіӣзҡ„пјҢз»ҷй«ҳеҺӢж …жһҒй©ұеҠЁйӣҶжҲҗз”өи·Ҝ(IC)зҡ„й«ҳз«Ҝж …жһҒй©ұеҠЁз”өи·Ҝдҫӣз”өзҡ„ж–№жі•гҖӮиҝҷз§ҚиҮӘдёҫејҸз”өжәҗжҠҖжңҜе…·жңүз®ҖеҚ•пјҢдё”дҪҺжҲҗжң¬зҡ„дјҳзӮ№гҖӮдҪҶжҳҜпјҢе®ғд№ҹжңүзјәзӮ№пјҢдёҖжҳҜеҚ з©әжҜ”еҸ—еҲ°иҮӘдёҫз”өе®№еҲ·ж–°з”өиҚ·жүҖйңҖж—¶й—ҙзҡ„йҷҗеҲ¶пјҢдәҢжҳҜеҪ“ејҖе…іеҷЁд»¶зҡ„жәҗжһҒжҺҘиҙҹз”өеҺӢж—¶пјҢдјҡеҸ‘з”ҹдёҘйҮҚзҡ„й—®йўҳгҖӮжң¬ж–ҮеҲҶжһҗдәҶжңҖжөҒиЎҢзҡ„иҮӘдёҫз”өи·Ҝи§ЈеҶіж–№жЎҲпјӣеҢ…жӢ¬еҜ„з”ҹеҸӮж•°пјҢиҮӘдёҫз”өйҳ»е’Ңз”өе®№еҜ№жө®еҠЁз”өжәҗе……з”өзҡ„еҪұе“ҚгҖӮ

В

01

й«ҳйҖҹж …жһҒй©ұеҠЁз”өи·Ҝ

В

иҮӘдёҫж …жһҒй©ұеҠЁжҠҖжңҜ

В

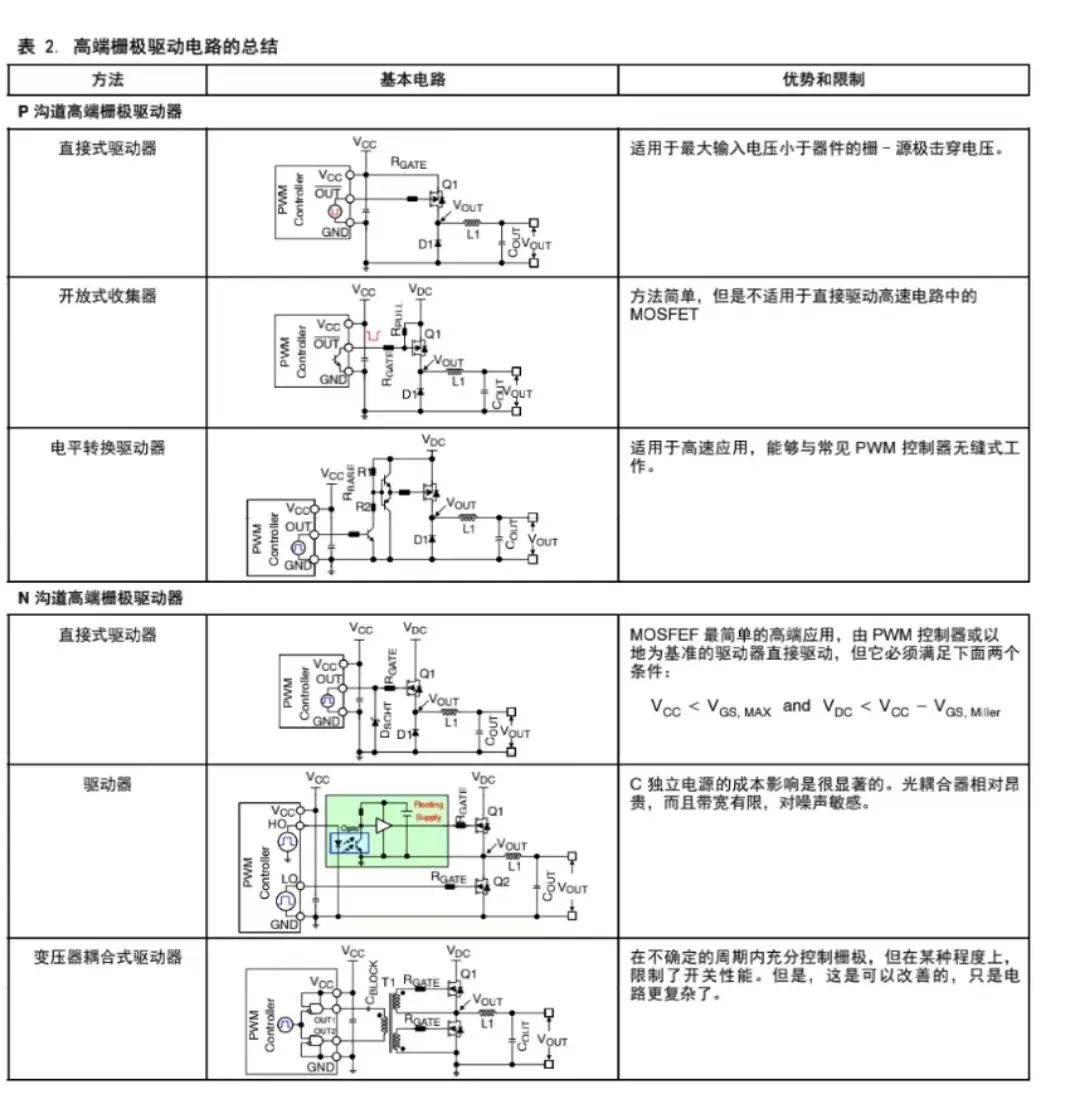

жң¬иҠӮйҮҚзӮ№и®ІеңЁдёҚеҗҢејҖе…іжЁЎејҸзҡ„еҠҹзҺҮиҪ¬жҚўеә”з”ЁдёӯпјҢеҠҹзҺҮеһӢMOSFETе’ҢIGBTеҜ№иҮӘдёҫејҸж …жһҒй©ұеҠЁз”өи·Ҝзҡ„иҰҒжұӮгҖӮеҪ“иҫ“е…Ҙз”өе№ідёҚе…Ғи®ёдёҠжЎҘNжІҹйҒ“еҠҹзҺҮеһӢMOSFETжҲ–IGBTдҪҝз”ЁзӣҙжҺҘејҸж …жһҒй©ұеҠЁз”өи·Ҝж—¶пјҢжҲ‘们е°ұеҸҜд»ҘиҖғиҷ‘иҮӘдёҫејҸж …жһҒй©ұеҠЁжҠҖжңҜгҖӮиҝҷз§Қж–№жі•иў«з”ЁдҪңж …жһҒй©ұеҠЁе’ҢдјҙеҸ‘еҒҸзҪ®з”өи·ҜпјҢдёӨиҖ…йғҪд»Ҙдё»ејҖе…іеҷЁд»¶зҡ„жәҗжһҒдҪңдёәеҹәеҮҶгҖӮ

В

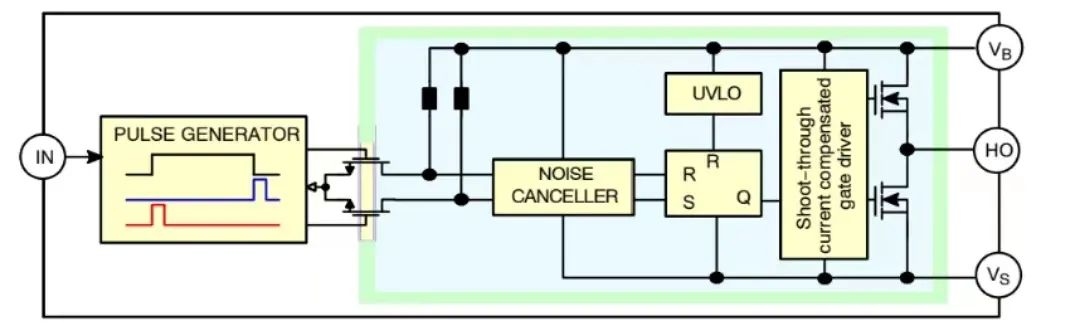

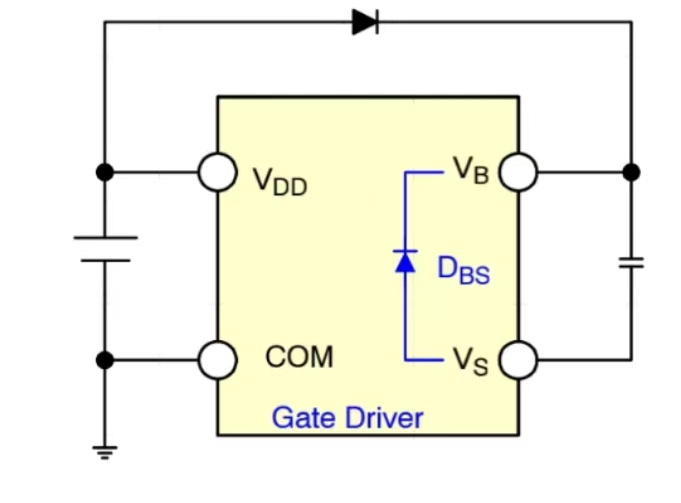

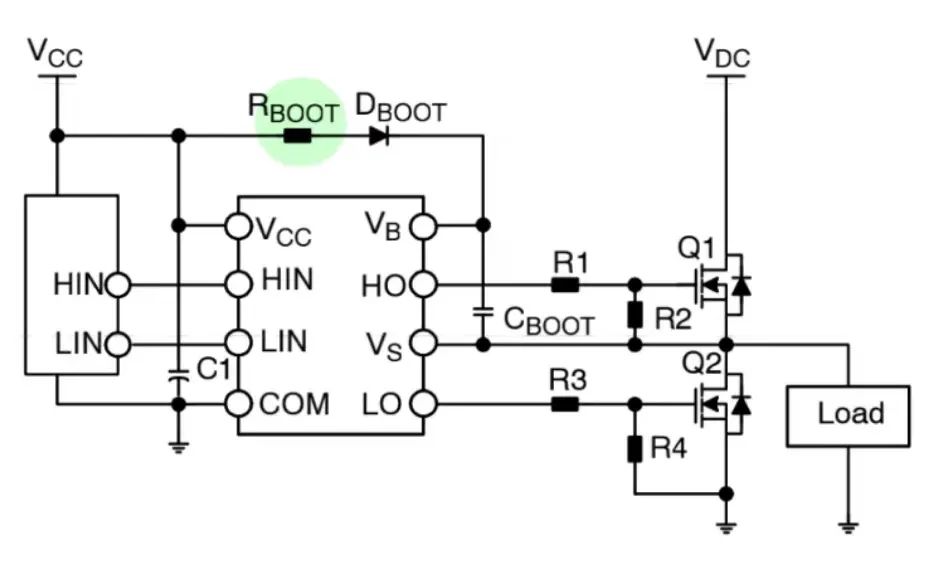

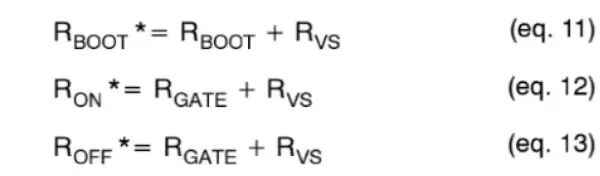

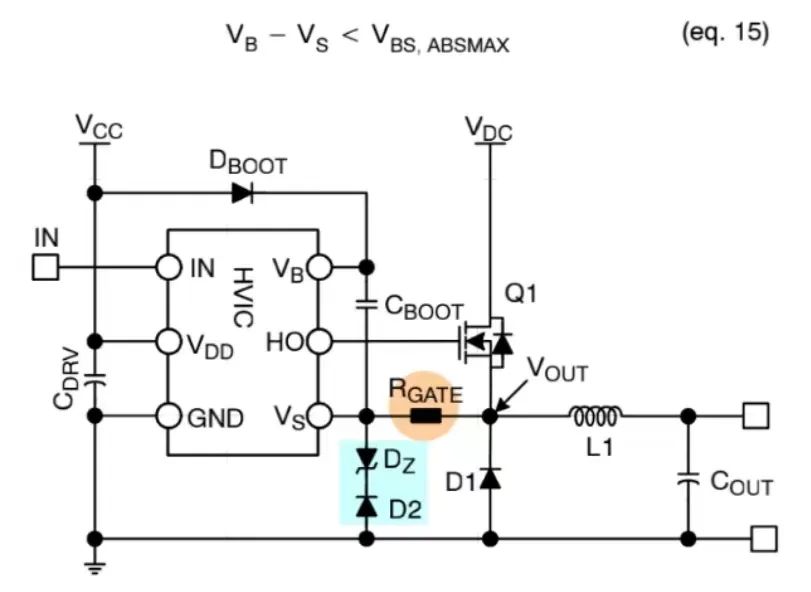

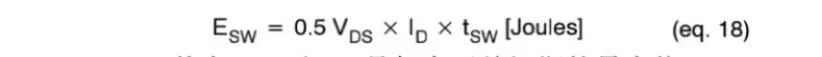

й©ұеҠЁз”өи·Ҝе’Ңд»ҘдёӨдёӘиҫ“е…Ҙз”өеҺӢдҪңдёәж‘Ҷе№…зҡ„еҒҸзҪ®з”өи·ҜпјҢйғҪдёҺеҷЁд»¶зҡ„жәҗжһҒиҪЁиҝһгҖӮдҪҶжҳҜпјҢй©ұеҠЁз”өи·Ҝе’Ңе®ғзҡ„жө®еҠЁеҒҸзҪ®еҸҜд»ҘйҖҡиҝҮдҪҺеҺӢз”өи·Ҝе®һзҺ°пјҢеӣ дёәиҫ“е…Ҙз”өеҺӢдёҚдјҡдҪңз”ЁеҲ°иҝҷдәӣз”өи·ҜдёҠгҖӮй©ұеҠЁз”өи·Ҝе’ҢжҺҘең°жҺ§еҲ¶дҝЎеҸ·йҖҡиҝҮдёҖдёӘз”өе№іиҪ¬жҚўз”өи·ҜзӣёиҝһгҖӮиҜҘз”өе№іиҪ¬жҚўз”өи·Ҝеҝ…йЎ»е…Ғи®ёжө®еҠЁдёҠжЎҘе’ҢжҺҘең°дёӢжЎҘз”өи·Ҝд№Ӣй—ҙеӯҳеңЁй«ҳз”өеҺӢе·®е’ҢдёҖе®ҡзҡ„з”өе®№жҖ§ејҖе…із”өжөҒгҖӮй«ҳз”өеҺӢж …жһҒй©ұеҠЁ IC йҖҡиҝҮзӢ¬зү№зҡ„з”өе№іиҪ¬жҚўи®ҫи®Ўе·®еҲҶејҖгҖӮдёәдәҶдҝқжҢҒй«ҳж•ҲзҺҮе’ҢеҸҜз®ЎзҗҶзҡ„еҠҹиҖ—пјҢз”өе№іиҪ¬жҚўз”өи·ҜеңЁдё»ејҖе…іеҜјйҖҡжңҹй—ҙпјҢдёҚиғҪеҗёж”¶д»»дҪ•з”өжөҒгҖӮеҜ№дәҺиҝҷз§Қжғ…еҶөпјҢжҲ‘们з»ҸеёёдҪҝз”Ёи„үеҶІејҸй”Ғеӯҳз”өе№іиҪ¬жҚўеҷЁпјҢеҰӮеӣҫ1жүҖзӨәгҖӮ

В

В

еӣҫ1В дёҠжЎҘй©ұеҠЁйӣҶжҲҗз”өи·Ҝзҡ„з”өе№іиҪ¬еҢ–еҷЁ

В

иҮӘдёҫејҸй©ұеҠЁз”өи·Ҝе·ҘдҪңеҺҹзҗҶ

В

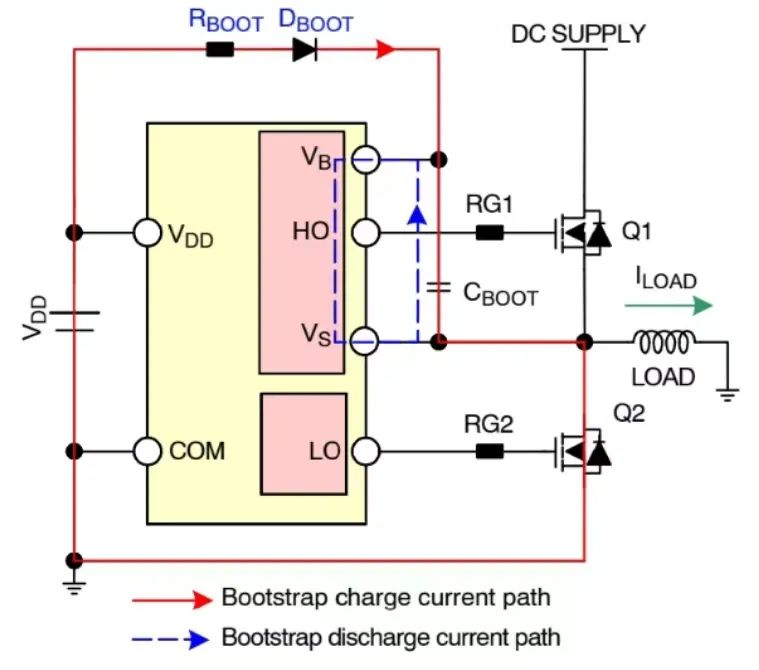

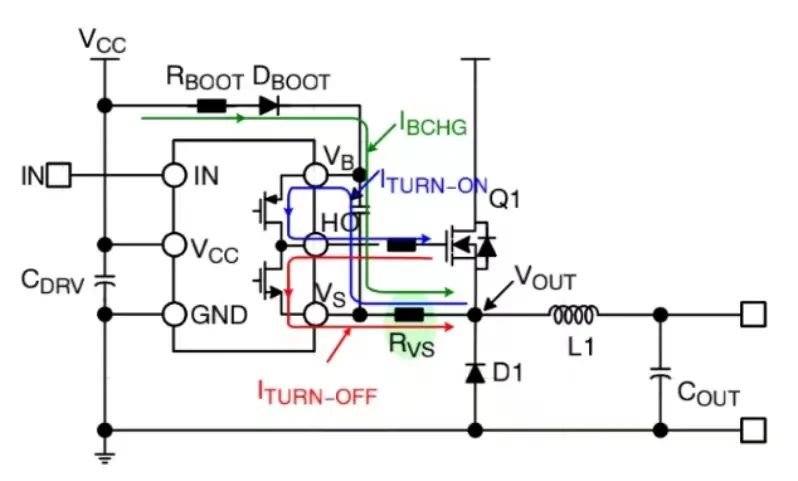

иҮӘдёҫејҸз”өи·ҜеңЁй«ҳз”өеҺӢж …жһҒй©ұеҠЁз”өи·ҜдёӯжҳҜеҫҲжңүз”Ёзҡ„пјҢе…¶е·ҘдҪңеҺҹзҗҶеҰӮдёӢгҖӮеҪ“VSйҷҚдҪҺеҲ°ICз”өжәҗз”өеҺӢVDDжҲ–дёӢжӢүиҮіең°ж—¶(дёӢжЎҘејҖе…іеҜјйҖҡпјҢдёҠжЎҘејҖе…іе…іж–ӯ)пјҢз”өжәҗVDDйҖҡиҝҮиҮӘдёҫз”өйҳ»пјҢRBOOTпјҢе’ҢиҮӘдёҫдәҢжһҒз®ЎпјҢDBOOTпјҢеҜ№иҮӘдёҫз”өе®№CBOOTпјҢиҝӣиЎҢе……з”өпјҢеҰӮеӣҫ2жүҖзӨәгҖӮеҪ“ VSиў«дёҠжЎҘејҖе…ідёҠжӢүеҲ°дёҖдёӘиҫғй«ҳз”өеҺӢж—¶пјҢз”ұVBSеҜ№иҜҘиҮӘдёҫз”өе®№е……з”өпјҢжӯӨж—¶пјҢVBSз”өжәҗжө®еҠЁпјҢиҮӘдёҫдәҢжһҒз®ЎеӨ„дәҺеҸҚеҗ‘еҒҸзҪ®пјҢиҪЁз”өеҺӢ(дёӢжЎҘејҖе…іе…іж–ӯпјҢдёҠжЎҘејҖе…іеҜјйҖҡ)е’ҢICз”өжәҗз”өеҺӢVDDпјҢиў«йҡ”зҰ»ејҖгҖӮ

В

В

В

еӣҫ2В иҮӘдёҫејҸз”өжәҗз”өи·Ҝ

В

иҮӘдёҫејҸз”өи·Ҝзҡ„зјәзӮ№

В

иҮӘдёҫејҸз”өи·Ҝе…·жңүз®ҖеҚ•е’ҢдҪҺжҲҗжң¬зҡ„дјҳзӮ№пјҢдҪҶжҳҜпјҢе®ғд№ҹжңүдёҖдәӣеұҖйҷҗгҖӮ

В

еҚ з©әжҜ”е’ҢеҜјйҖҡж—¶й—ҙеҸ—йҷҗдәҺиҮӘдёҫз”өе®№CBOOTпјҢеҲ·ж–°з”өиҚ·жүҖйңҖж—¶й—ҙзҡ„йҷҗеҲ¶гҖӮ

В

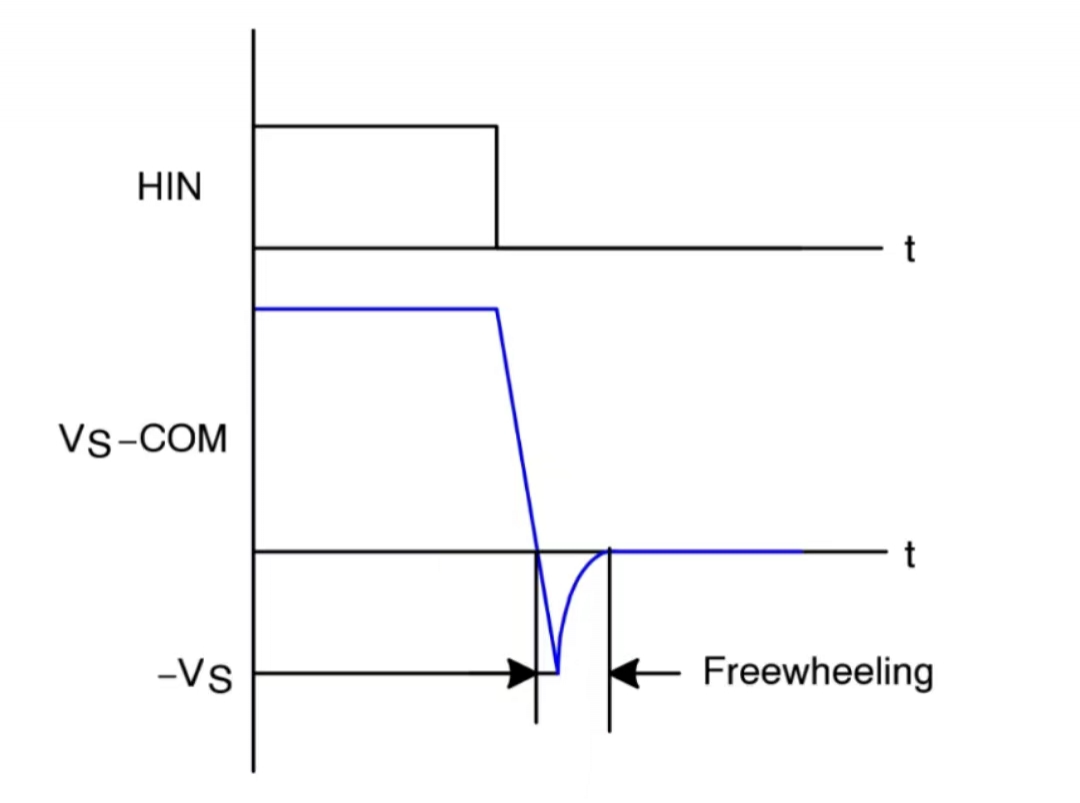

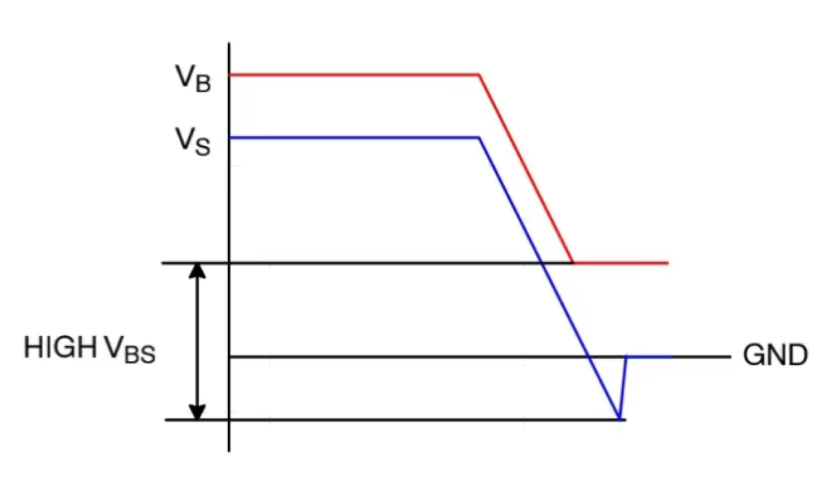

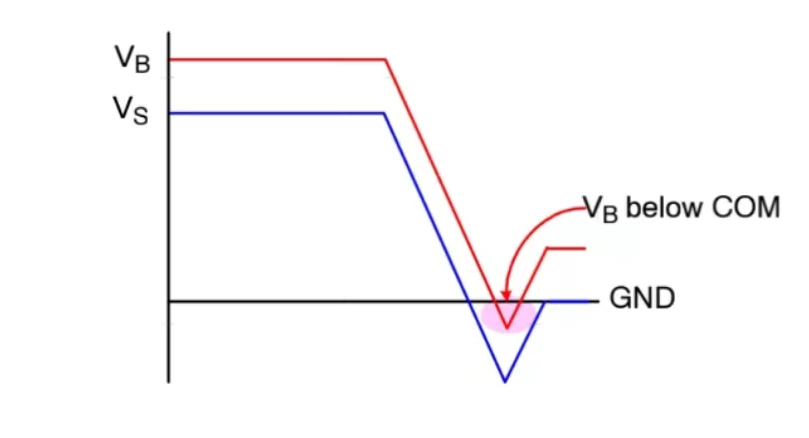

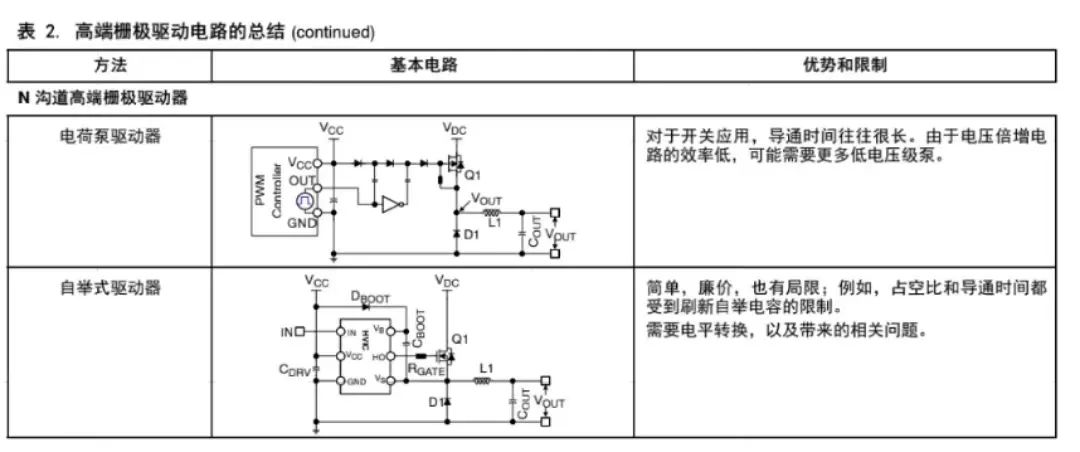

иҝҷдёӘз”өи·ҜжңҖеӨ§зҡ„йҡҫзӮ№еңЁдәҺпјҡеҪ“ејҖе…іеҷЁд»¶е…іж–ӯж—¶пјҢе…¶жәҗжһҒзҡ„иҙҹз”өеҺӢдјҡдҪҝиҙҹиҪҪз”өжөҒзӘҒ然жөҒиҝҮз»ӯжөҒдәҢжһҒз®ЎпјҢеҰӮеӣҫ3жүҖзӨәгҖӮ

В

иҜҘиҙҹз”өеҺӢдјҡз»ҷж …жһҒй©ұеҠЁз”өи·Ҝзҡ„иҫ“еҮәз«ҜйҖ жҲҗйә»зғҰпјҢеӣ дёәе®ғзӣҙжҺҘеҪұе“Қй©ұеҠЁз”өи·ҜжҲ–PWMжҺ§еҲ¶йӣҶжҲҗз”өи·Ҝзҡ„жәҗжһҒVSеј•и„ҡпјҢеҸҜиғҪдјҡжҳҺжҳҫең°е°ҶжҹҗдәӣеҶ…йғЁз”өи·ҜдёӢжӢүеҲ°ең°д»ҘдёӢпјҢеҰӮеӣҫ4жүҖзӨәгҖӮеҸҰеӨ–дёҖдёӘй—®йўҳжҳҜпјҢиҜҘиҙҹз”өеҺӢзҡ„иҪ¬жҚўеҸҜиғҪдјҡдҪҝиҮӘдёҫз”өе®№еӨ„дәҺиҝҮеҺӢзҠ¶жҖҒгҖӮ

В

иҮӘдёҫз”өе®№CBOOTпјҢйҖҡиҝҮиҮӘдёҫдәҢжһҒз®ЎDBOOTпјҢиў«з”өжәҗVDDзһ¬й—ҙе……з”өгҖӮ

В

з”ұдәҺVDDз”өжәҗд»Ҙең°дҪңдёәеҹәеҮҶпјҢиҮӘдёҫз”өе®№дә§з”ҹзҡ„жңҖеӨ§з”өеҺӢVDCзӯүдәҺVDDеҠ дёҠжәҗжһҒдёҠзҡ„иҙҹз”өеҺӢжҢҜе№…гҖӮ

В

В

еӣҫ3В еҚҠжЎҘејҸеә”з”Ёз”өи·Ҝ

В

В

еӣҫ4В е…іж–ӯжңҹй—ҙзҡ„VSжіўеҪў

В

Vs еј•и„ҡдә§з”ҹиҙҹз”өеҺӢзҡ„еҺҹеӣ

В

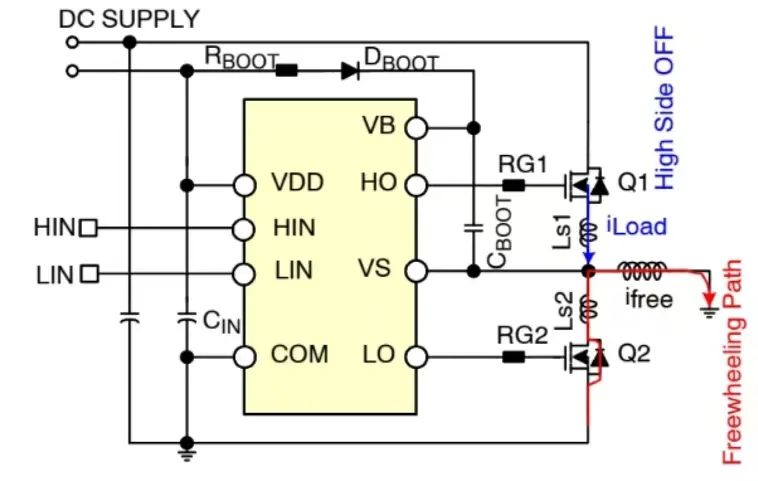

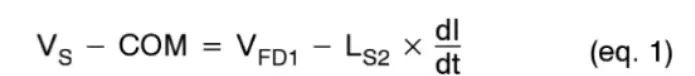

еҰӮеӣҫ5жүҖзӨәпјҢдёӢжЎҘз»ӯжөҒдәҢжһҒз®Ўзҡ„еүҚеҗ‘еҒҸзҪ®жҳҜе·ІзҹҘзҡ„е°ҶVSдёӢдҪҺCOM(ең°)д»ҘдёӢзҡ„еҺҹеӣ д№ӢдёҖгҖӮ

В

дё»иҰҒй—®йўҳеҮәзҺ°еңЁж•ҙжөҒеҷЁжҚўеҗ‘жңҹй—ҙпјҢд»…д»…еңЁз»ӯжөҒдәҢжһҒз®ЎејҖе§Ӣз®қеҺӢд№ӢеүҚгҖӮ

В

еңЁиҝҷз§Қжғ…еҶөдёӢпјҢз”өж„ҹLS1е’ҢLS2дјҡе°ҶVSеҺӢдҪҺеҲ°COMд»ҘдёӢпјҢз”ҡиҮіеҰӮдёҠжүҖиҝ°зҡ„дҪҚзҪ®жҲ–жӯЈеёёзЁіжҖҒгҖӮ

В

иҜҘиҙҹз”өеҺӢзҡ„ж”ҫеӨ§еҖҚж•°жӯЈжҜ”дәҺеҜ„з”ҹз”өж„ҹе’ҢејҖе…іеҷЁд»¶зҡ„е…іж–ӯйҖҹеәҰпјҢdi / dt пјӣе®ғз”ұж …жһҒй©ұеҠЁз”өйҳ»пјҢRGATEе’ҢејҖе…іеҷЁд»¶зҡ„иҫ“е…Ҙз”өе®№пјҢCissеҶіе®ҡгҖӮ

В

CgsдёҺCgdзҡ„е’ҢпјҢз§°дёәеҜҶеӢ’з”өе®№гҖӮ

В

В

еӣҫ5В йҷҚеҺӢиҪ¬жҚўеҷЁ

В

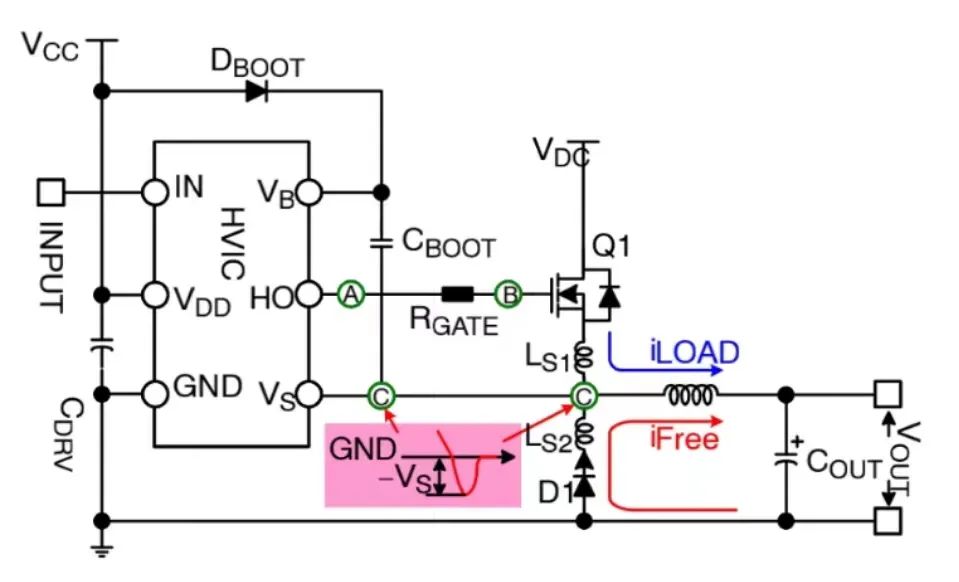

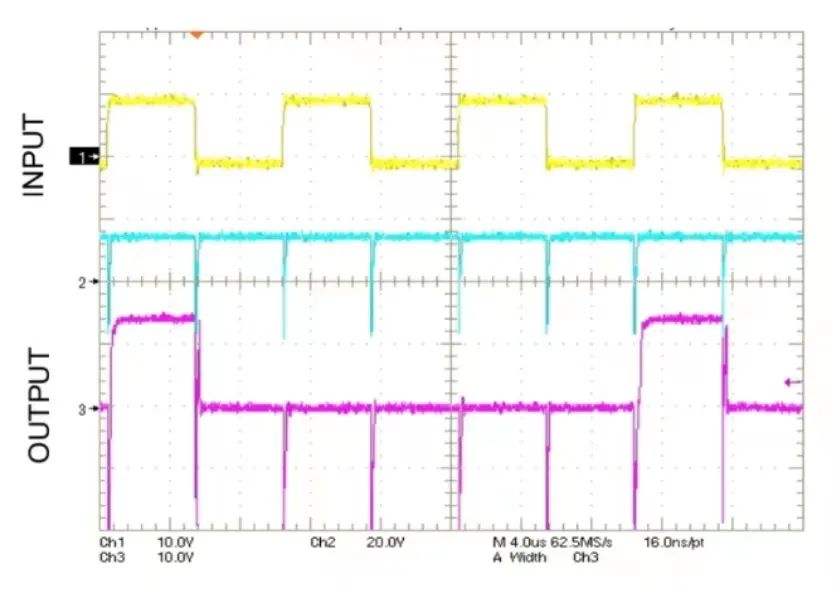

еӣҫ6жҸҸиҝ°дәҶдёҠжЎҘNжІҹйҒ“MOSFETе…іж–ӯжңҹй—ҙзҡ„з”өеҺӢжіўеҪўгҖӮ

В

В

еӣҫ6В е…іж–ӯжңҹй—ҙзҡ„жіўеҪў

В

Vs еј•и„ҡз”өеҺӢдёӢеҶІзҡ„еҪұе“Қ

В

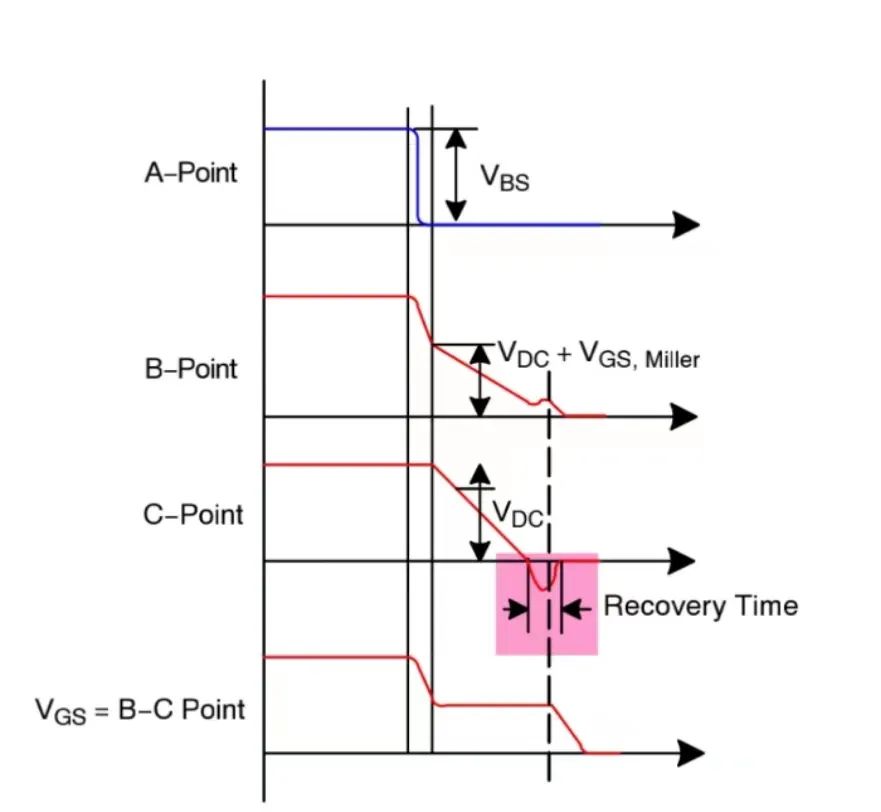

еҰӮжһңж¬ еҶІи¶…иҝҮж•°жҚ®жүӢеҶҢдёӯ规е®ҡзҡ„з»қеҜ№жңҖеӨ§йўқе®ҡеҖјпјҢеҲҷж …жһҒй©ұеҠЁICе°ҶжҚҹеқҸпјҢжҲ–иҖ…дёҠжЎҘиҫ“еҮәжҡӮж—¶ж— жі•еҜ№иҫ“е…ҘиҪ¬жҚўеҒҡеҮәе“Қеә”пјҢеҰӮеӣҫ7е’Ңеӣҫ8жүҖзӨәгҖӮ

В

еӣҫ7жҳҫзӨәй—ӯй”Ғжғ…еҶөпјҢеҚідёҠжЎҘиҫ“еҮәж— жі•йҖҡиҝҮиҫ“е…ҘдҝЎеҸ·иҖіж”№еҸҳгҖӮиҝҷз§Қжғ…еҶөдёӢпјҢеҚҠжЎҘжӢ“жү‘зҡ„еӨ–йғЁгҖҒдё»з”өжәҗгҖҒй«ҳз«Ҝз®ЎпјҢе’ҢдёӢжЎҘејҖе…ідёӯеҸ‘з”ҹзҹӯи·ҜгҖӮ

В

В

еӣҫ7В й—ӯй”Ғжғ…еҶөдёӢзҡ„жіўеҪў

В

еӣҫ8жҳҫзӨәйҒ—жјҸжғ…еҶөпјҢеҚідёҠжЎҘиҫ“еҮәж— жі•еҜ№иҫ“е…ҘиҪ¬жҚўеҒҡеҮәе“Қеә”гҖӮиҝҷз§Қжғ…еҶөдёӢпјҢдёҠжЎҘж …жһҒй©ұеҠЁеҷЁзҡ„з”өе№іиҪ¬жҚўеҷЁе°Ҷзјәе°‘е·ҘдҪңз”өеҺӢдҪҷйҮҸгҖӮйңҖиҰҒжіЁж„Ҹзҡ„жҳҜпјҢеӨ§еӨҡж•°дәӢе®һиҜҒжҳҺдёҠжЎҘйҖҡеёёдёҚйңҖиҰҒеңЁдёҖдёӘејҖе…іеҠЁдҪңд№ӢеҗҺз«ӢеҚіж”№еҸҳзҠ¶жҖҒгҖӮ

В

В

еӣҫ8В дҝЎеҸ·дёўеӨұжғ…еҶөдёӢзҡ„жіўеҪў

В

иҖғиҷ‘й—ӯй”Ғж•Ҳеә”

В

жңҖе®Ңж•ҙзҡ„й«ҳз”өеҺӢж …жһҒй©ұеҠЁйӣҶжҲҗз”өи·ҜйғҪеҗ«жңүеҜ„з”ҹдәҢжһҒз®ЎпјҢе®ғиў«еүҚеҗ‘жҲ–еҸҚеҗ‘еҮ»з©ҝпјҢе°ұеҸҜиғҪеҜјиҮҙеҜ„з”ҹSCRй—ӯй”ҒгҖӮй—ӯй”Ғж•Ҳеә”зҡ„жңҖз»Ҳз»“жһңеҫҖеҫҖжҳҜж— жі•йў„жөӢзҡ„пјҢз ҙеқҸиҢғеӣҙд»ҺеҷЁд»¶е·ҘдҪңж—¶еёёдёҚзЁіе®ҡеҲ°е®Ңе…ЁеӨұж•ҲгҖӮж …жһҒй©ұеҠЁйӣҶжҲҗз”өи·Ҝд№ҹеҸҜиғҪиў«еҲқж¬ЎиҝҮеҺӢд№ӢеҗҺзҡ„дёҖзі»еҲ—еҠЁдҪңй—ҙжҺҘжҚҹеқҸгҖӮдҫӢеҰӮпјҢй—ӯй”ҒеҜјиҮҙиҫ“еҮәй©ұеҠЁзҪ®дәҺй«ҳжҖҒпјҢйҖ жҲҗдәӨеҸүдј еҜјпјҢд»ҺиҖҢеҜјиҮҙејҖе…іж•…йҡңпјҢ并жңҖз»ҲдҪҝж …жһҒй©ұеҠЁеҷЁйӣҶжҲҗз”өи·ҜйҒӯеҸ—зҒҫйҡҫжҖ§з ҙеқҸгҖӮ

В

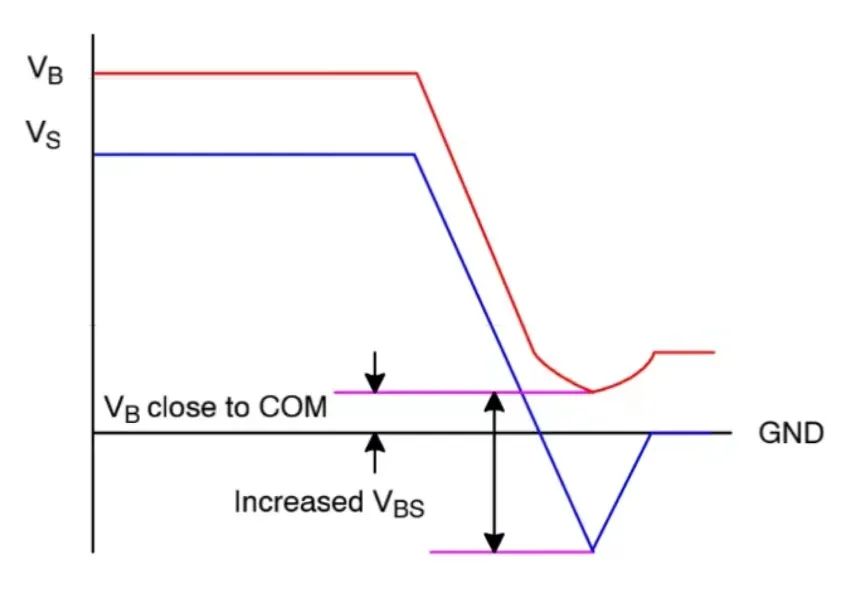

еҰӮжһңеҠҹзҺҮиҪ¬жҚўз”өи·Ҝе’ҢпјҸжҲ–ж …жһҒй©ұеҠЁйӣҶжҲҗз”өи·ҜеҸ—еҲ°з ҙеқҸпјҢиҝҷз§ҚеӨұж•ҲжЁЎејҸеә”иў«иҖғиҷ‘жҲҗдёҖдёӘеҸҜиғҪзҡ„ж №жң¬еҺҹеӣ гҖӮдёӢйқўзҡ„зҗҶи®әжһҒйҷҗеҸҜз”ЁжқҘеё®еҠ©и§ЈйҮҠVsз”өеҺӢдёҘйҮҚдёҚи¶іе’Ңз”ұжӯӨдә§з”ҹй—ӯй”Ғж•Ҳеә”д№Ӣй—ҙзҡ„е…ізі»гҖӮ

В

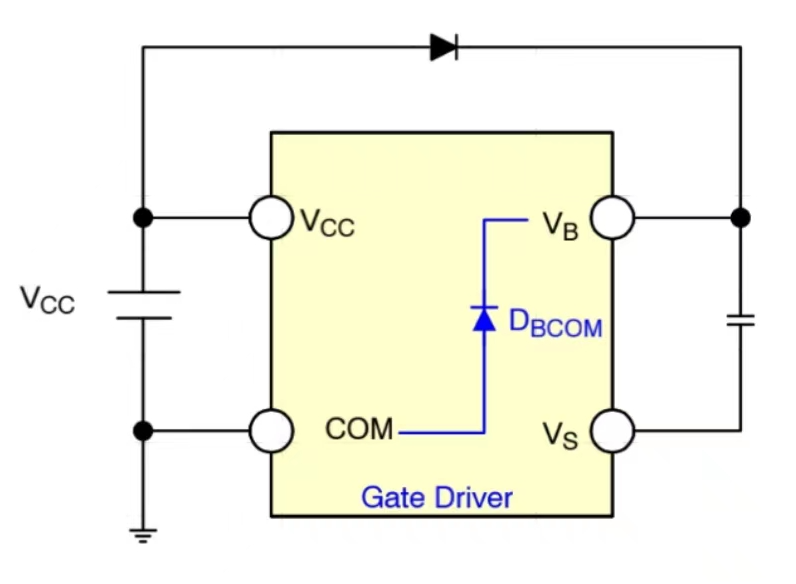

еңЁз¬¬дёҖз§Қжғ…еҶөдёӯпјҢдҪҝз”ЁдәҶдёҖдёӘзҗҶжғіиҮӘдёҫз”өи·Ҝж‘„пјҢиҜҘз”өи·Ҝзҡ„VDDз”ұдёҖдёӘйӣ¶ж¬§е§Ҷз”өжәҗй©ұеҠЁпјҢйҖҡиҝҮдёҖдёӘзҗҶжғідәҢжһҒз®ЎиҝһжҺҘеҲ°VBпјҢеҰӮеӣҫ9жүҖзӨәгҖӮеҪ“еӨ§з”өжөҒжөҒиҝҮз»ӯжөҒдәҢжһҒз®Ўж—¶пјҢз”ұдәҺdi / dtеҫҲеӨ§пјҢVsз”өеҺӢе°ҶдҪҺдәҺең°з”өеҺӢгҖӮиҝҷж—¶пјҢй—ӯй”ҒеҚұйҷ©еҸ‘з”ҹдәҶпјҢеӣ дёәж …жһҒй©ұеҠЁеҷЁеҶ…йғЁзҡ„еҜ„з”ҹдәҢжһҒз®ЎDBSпјҢжңҖз»ҲжІҝVsеҲ°VBж–№еҗ‘еҜјйҖҡпјҢйҖ жҲҗдёӢеҶІз”өеҺӢдёҺVDDеҸ еҠ пјҢдҪҝеҫ—иҮӘдёҫз”өе®№иў«иҝҮеәҰе……з”өпјҢеҰӮеӣҫ10жүҖзӨәгҖӮ

В

дҫӢеҰӮпјҡеҰӮжһңVDD =15 V, Vs дёӢеҶІи¶…иҝҮ10 VпјҢиҝ«дҪҝжө®еҠЁз”өжәҗз”өеҺӢеңЁ25 V д»ҘдёҠпјҢдәҢжһҒз®ЎDBsжңүиў«еҮ»з©ҝзҡ„еҚұйҷ©пјҢиҝӣиҖҢдә§з”ҹй—ӯй”ҒгҖӮ

В

В

еӣҫ9В жғ…еҶө1пјҡзҗҶжғіиҮӘдёҫз”өи·Ҝ

В

В

еӣҫ10В жғ…еҶө1зҡ„VBе’ҢVSжіўеҪў

В

еҒҮжғіиҮӘдёҫз”өжәҗиў«зҗҶжғіжө®еҠЁз”өжәҗжӣҝд»ЈпјҢеҰӮеӣҫ11жүҖзӨәпјҢиҝҷж—¶пјҢVBSеңЁд»»дҪ•жғ…еҶөдёӢйғҪжҳҜжҒ’е®ҡзҡ„гҖӮжіЁж„ҸеҲ©з”ЁдёҖдёӘдҪҺз”өйҳ»иҫ…еҠ©з”өжәҗжӣҝд»ЈиҮӘдёҫз”өи·ҜпјҢе°ұиғҪе®һзҺ°иҝҷз§Қжғ…еҶөгҖӮиҝҷж—¶пјҢеҰӮжһңVsиҝҮеҶІи¶…иҝҮж•°жҚ®иЎЁ(datasheet)规е®ҡзҡ„жңҖеӨ§VBSз”өеҺӢпјҢй—ӯй”ҒеҚұйҷ©е°ұдјҡеҸ‘з”ҹпјҢеӣ дёәеҜ„з”ҹдәҢжһҒз®ЎDBCOMжңҖз»ҲжІҝCOMз«ҜеҲ°VBж–№еҗ‘еҜјйҖҡпјҢеҰӮеӣҫ12жүҖзӨәгҖӮ

В

В

еӣҫ11В жғ…еҶө2пјҡзҗҶжғіжө®еҠЁз”өжәҗ

В

В

еӣҫ12В жғ…еҶө2зҡ„VBе’ҢVSжіўеҪў

В

дёҖз§Қе®һз”Ёзҡ„з”өи·ҜеҸҜиғҪеӨ„еңЁд»ҘдёҠдёӨз§ҚжһҒйҷҗд№Ӣй—ҙпјҢз»“жһңжҳҜ VBSВ з”өеҺӢзЁҚеҫ®еўһеӨ§пјҢе’Ң VB зЁҚдҪҺдәҺ VDD пјҢеҰӮеӣҫ13жүҖзӨәгҖӮ

В

В

еӣҫ13В Vgе’ҢVsзҡ„е…ёеһӢе“Қеә”

В

еҮҶзЎ®ең°иҜҙпјҢд»»дҪ•дёҖз§ҚжһҒйҷҗжғ…еҶөйғҪжҳҜжөҒиЎҢзҡ„пјҢжЈҖйӘҢеҰӮдёӢгҖӮеҰӮжһң Vs иҝҮеҶІжҢҒз»ӯж—¶й—ҙи¶…иҝҮ10дёӘзәіз§’пјҢиҮӘдёҫз”өе®№ CBOOTВ иў«иҝҮе……з”өпјҢйӮЈд№Ҳй«ҳз«Ҝж …жһҒй©ұеҠЁеҷЁз”өи·Ҝиў«иҝҮз”өеҺӢеә”еҠӣз ҙеқҸпјҢеӣ дёә VBS з”өеҺӢи¶…иҝҮдәҶж•°жҚ®иЎЁжҢҮе®ҡзҡ„з»қеҜ№жңҖеӨ§з”өеҺӢ(VBSMAXВ )гҖӮи®ҫи®ЎдёҖдёӘиҮӘдёҫз”өи·Ҝж—¶пјҢе…¶иҫ“еҮәз”өеҺӢдёҚиғҪи¶…иҝҮй«ҳз«Ҝж …жһҒй©ұеҠЁеҷЁзҡ„з»қеҜ№жңҖеӨ§йўқе®ҡз”өеҺӢгҖӮ

В

еҜ„з”ҹз”өж„ҹж•Ҳеә”

В

иҙҹз”өеҺӢзҡ„жҢҜе№…жҳҜпјҡ

В

В

дёәдәҶеҮҸе°ҸжөҒиҝҮеҜ„з”ҹз”өж„ҹзҡ„з”өжөҒйҡҸж—¶й—ҙеҸҳеҢ–жӣІзәҝзҡ„ж–ңеәҰпјҢиҰҒдҪҝзӯүејҸ1дёӯзҡ„еҜјж•°йЎ№жңҖе°ҸгҖӮ

В

дҫӢеҰӮпјҡеҰӮжһңеёҰ100 nHеҜ„з”ҹз”өж„ҹзҡ„10 A гҖҒ25 Vж …жһҒй©ұеҠЁеҷЁеңЁ50 nsеҶ…ејҖе…іпјҢеҲҷVsдёҺжҺҘең°д№Ӣй—ҙзҡ„иҙҹз”өеҺӢе°–еі°жҳҜ20 VгҖӮ

В

В02

иҮӘдёҫйғЁд»¶зҡ„и®ҫи®ЎжөҒзЁӢ

В

йҖүжӢ©иҮӘдёҫз”өе®№

В

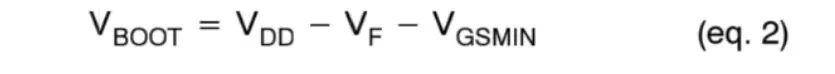

иҮӘдёҫз”өе®№(CBOOT)жҜҸж¬ЎйғҪиў«е……з”өпјҢжӯӨж—¶пјҢдёӢжЎҘй©ұеҠЁеҷЁеҜјйҖҡпјҢиҫ“еҮәз”өеҺӢдҪҺдәҺж …жһҒй©ұеҠЁеҷЁзҡ„з”өжәҗз”өеҺӢ(VDD)гҖӮиҮӘдёҫз”өе®№д»…еҪ“дёҠжЎҘејҖе…іеҜјйҖҡзҡ„ж—¶еҖҷж”ҫз”өгҖӮиҮӘдёҫз”өе®№з»ҷдёҠжЎҘз”өи·ҜжҸҗдҫӣз”өжәҗ(VBS)гҖӮйҰ–е…ҲиҰҒиҖғиҷ‘зҡ„еҸӮж•°жҳҜдёҠжЎҘејҖе…іеӨ„дәҺеҜјйҖҡж—¶пјҢиҮӘдёҫз”өе®№зҡ„жңҖеӨ§з”өеҺӢйҷҚгҖӮе…Ғи®ёзҡ„жңҖеӨ§з”өеҺӢйҷҚ(VBOOT)еҸ–еҶідәҺиҰҒдҝқжҢҒзҡ„жңҖе°Ҹж …жһҒй©ұеҠЁз”өеҺӢ(еҜ№дәҺдёҠжЎҘејҖе…і)гҖӮеҰӮжһң VGSMINжҳҜжңҖе°Ҹзҡ„ж …дёҖжәҗжһҒз”өеҺӢпјҢз”өе®№зҡ„з”өеҺӢйҷҚеҝ…йЎ»жҳҜпјҡ

В

В

е…¶дёӯпјҡВ

В

VDDВ пјқж …жһҒй©ұеҠЁеҷЁзҡ„з”өжәҗз”өеҺӢпјӣе’Ң

В

В VFВ пјқиҮӘдёҫдәҢжһҒз®ЎжӯЈеҗ‘з”өеҺӢйҷҚпј»V]

В

и®Ўз®—иҮӘдёҫз”өе®№дёәпјҡ

В

В

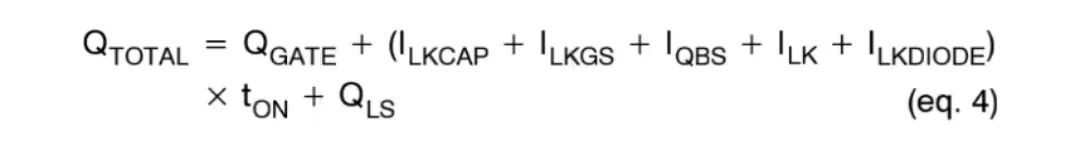

е…¶дёӯ QTOTAL жҳҜз”өе®№еҷЁзҡ„з”өиҚ·жҖ»йҮҸгҖӮ

В

иҮӘдёҫз”өе®№зҡ„з”өиҚ·жҖ»йҮҸйҖҡиҝҮзӯүејҸ4и®Ўз®—пјҡ

В

В

е…¶дёӯпјҡ

В

В QGATEВ пјқж …жһҒз”өиҚ·зҡ„жҖ»йҮҸеҪ“

В

В ILKGSВ пјқејҖе…іж …дёҖжәҗзә§жјҸз”өжөҒпјӣ

В

В ILKCAPВ пјқиҮӘдёҫз”өе®№зҡ„жјҸз”өжөҒпјӣ

В

В lQBS пјқиҮӘдёҫз”өи·Ҝзҡ„йқҷжҖҒз”өжөҒпјӣ

В

В ILKВ пјқиҮӘдёҫз”өи·Ҝзҡ„жјҸз”өжөҒпјӣ

В

В QLS =еҶ…йғЁз”өе№іиҪ¬жҚўеҷЁжүҖйңҖиҰҒзҡ„з”өиҚ·пјҢеҜ№дәҺжүҖжңүзҡ„й«ҳеҺӢж …жһҒй©ұеҠЁз”өи·ҜпјҢиҜҘеҖјдёә3 nC ;

В

В tONВ пјқдёҠжЎҘеҜјйҖҡж—¶й—ҙпјӣ

В

В LKDIODED пјқиҮӘдёҫдәҢжһҒз®Ўзҡ„жјҸз”өжөҒпјӣ

В

з”өе®№еҷЁзҡ„жјҸз”өжөҒпјҢеҸӘжңүеңЁдҪҝз”Ёз”өи§Јз”өе®№еҷЁж—¶пјҢжүҚйңҖиҰҒиҖғиҷ‘пјҢеҗҰеҲҷпјҢеҸҜд»ҘеҝҪз•ҘдёҚи®ЎгҖӮ

В

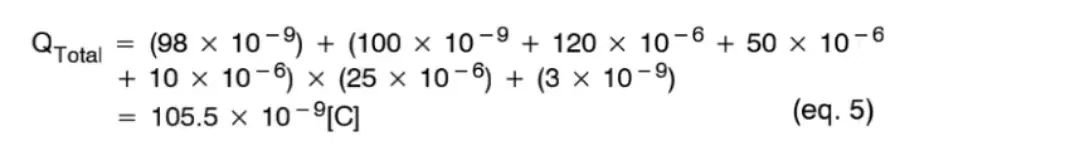

дҫӢеҰӮпјҡеҪ“дҪҝз”ЁеӨ–йғЁиҮӘдёҫдәҢжһҒз®Ўж—¶пјҢдј°з®—иҮӘдёҫз”өе®№зҡ„еӨ§е°ҸгҖӮ

В

в—Ҹж …жһҒй©ұеҠЁ IC =FAN7382( ON Semiconductor )

В

в—ҸејҖе…іеҷЁд»¶пјқFCP20N60( ON Semiconductor )

В

в—ҸиҮӘдёҫдәҢжһҒз®ЎпјқUF4007

В

в—ҸVDD =15 VВ

В

в—ҸQGATE =98 nC пјҲжңҖеӨ§еҖјпјү

В

в—ҸLKGS =100 nA пјҲжңҖеӨ§еҖјпјү

В

в—ҸILKCAP =0пјҲйҷ¶з“·з”өе®№пјү

В

в—ҸlQBS =120 ОјA пјҲжңҖеӨ§еҖјпјү ILK =50В ОјA пјҲжңҖеӨ§еҖјпјү

В

в—ҸQLS=3 nCВ

В

в—Ҹ TON =25 Ојs пјҲеңЁ fS=20 kHz ж—¶еҚ з©әжҜ”пјқ50%)

В

в—ҸВ ILKDIODE =10 ОјAВ

В

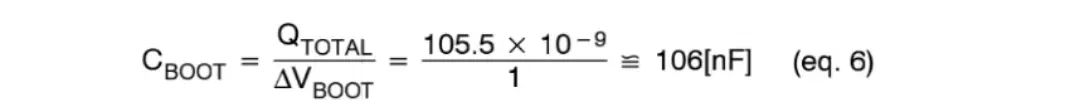

еҰӮжһңиҮӘдёҫз”өе®№еҷЁеңЁй«ҳз«ҜејҖе…іеӨ„дәҺејҖеҗҜзҠ¶жҖҒж—¶пјҢжңҖеӨ§е…Ғи®ёзҡ„з”өеҺӢйҷҚжҳҜ1.0 V пјҢжңҖе°Ҹз”өе®№еҖјйҖҡиҝҮзӯүејҸ3и®Ўз®—гҖӮ

В

В

иҮӘдёҫз”өе®№и®Ўз®—еҰӮдёӢ:

В

В

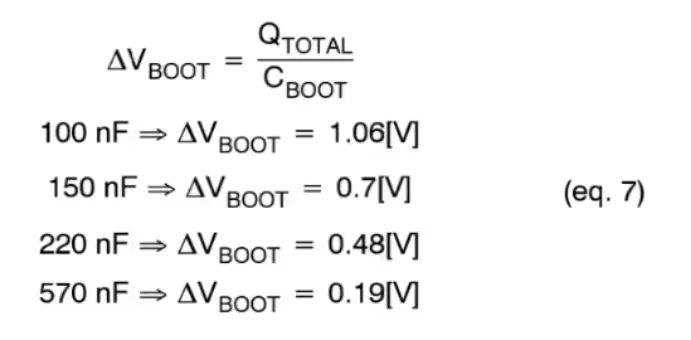

еӨ–йғЁдәҢжһҒз®ЎеҜјиҮҙзҡ„з”өеҺӢйҷҚеӨ§зәҰдёә0.7 V гҖӮеҒҮи®ҫз”өе®№е……з”өж—¶й—ҙзӯүдәҺдёҠжЎҘеҜјйҖҡж—¶й—ҙ(еҚ з©әжҜ”50%)гҖӮж №жҚ®дёҚеҗҢзҡ„иҮӘдёҫз”өе®№еҖјпјҢдҪҝз”Ёд»ҘдёӢзҡ„зӯүејҸ:

В

В

жҺЁиҚҗзҡ„з”өе®№еҖјжҳҜ100nF~570 nF пјҢдҪҶжҳҜе®һйҷ…зҡ„з”өе®№еҖјеҝ…йЎ»ж №жҚ®дҪҝз”Ёзҡ„еҷЁд»¶жқҘйҖүжӢ©гҖӮеҰӮжһңз”өе®№еҖјиҝҮеӨ§пјҢиҮӘдёҫз”өе®№зҡ„е……з”өж—¶й—ҙеҮҸе°‘пјҢдёӢжЎҘеҜјйҖҡж—¶й—ҙеҸҜиғҪдёҚи¶ід»ҘдҪҝз”өе®№иҫҫеҲ°иҮӘдёҫз”өеҺӢгҖӮ

В

йҖүжӢ©иҮӘдёҫз”өйҳ»

В

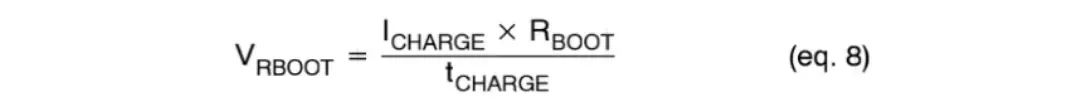

еҪ“дҪҝз”ЁеӨ–йғЁиҮӘдёҫз”өйҳ»ж—¶пјҢз”өйҳ» RBOOTеёҰжқҘдёҖдёӘйўқеӨ–зҡ„з”өеҺӢйҷҚпјҡ

В

В

е…¶дёӯпјҡ

В

В ICHARGEВ пјқиҮӘдёҫз”өе®№зҡ„е……з”өз”өжөҒпјӣ

В

В RР’OOT пјқиҮӘдёҫз”өйҳ»пјӣе’Ң

В

В tCHARGEВ пјқиҮӘдёҫз”өе®№зҡ„е……з”өж—¶й—ҙпјҲдёӢжЎҘеҜјйҖҡж—¶й—ҙпјү

В

дёҚиҰҒи¶…иҝҮ欧е§ҶеҖјпјҲе…ёеһӢеҖј5~10О©)пјҢе°ҶдјҡеўһеҠ VBSж—¶й—ҙеёёж•°гҖӮеҪ“и®Ўз®—жңҖеӨ§е…Ғи®ёзҡ„з”өеҺӢйҷҚ(VBOOT)ж—¶пјҢеҝ…йЎ»иҖғиҷ‘иҮӘдёҫдәҢжһҒз®Ўзҡ„з”өеҺӢйҷҚгҖӮеҰӮжһңиҜҘз”өеҺӢйҷҚеӨӘеӨ§жҲ–з”өи·ҜдёҚиғҪжҸҗдҫӣи¶іеӨҹзҡ„е……з”өж—¶й—ҙпјҢжҲ‘们еҸҜд»ҘдҪҝз”ЁдёҖдёӘеҝ«йҖҹжҒўеӨҚжҲ–и¶…еҝ«жҒўеӨҚдәҢжһҒз®ЎгҖӮ

В

03

иҖғиҷ‘иҮӘдёҫеә”з”Ёз”өи·Ҝ

В

иҮӘдёҫеҗҜеҠЁз”өи·Ҝ

В

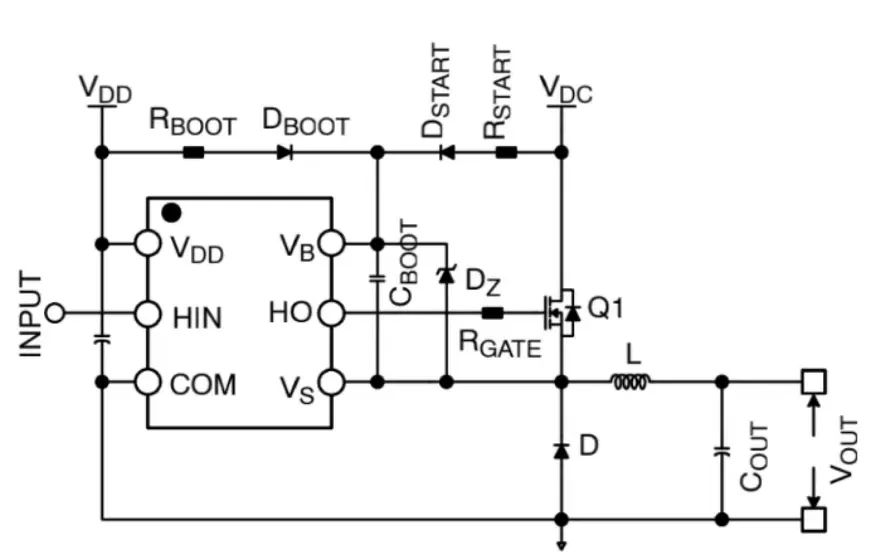

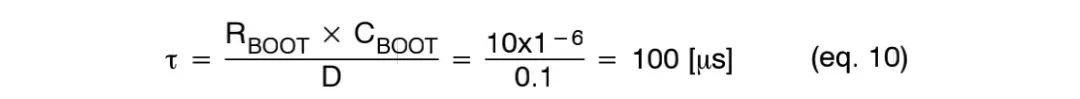

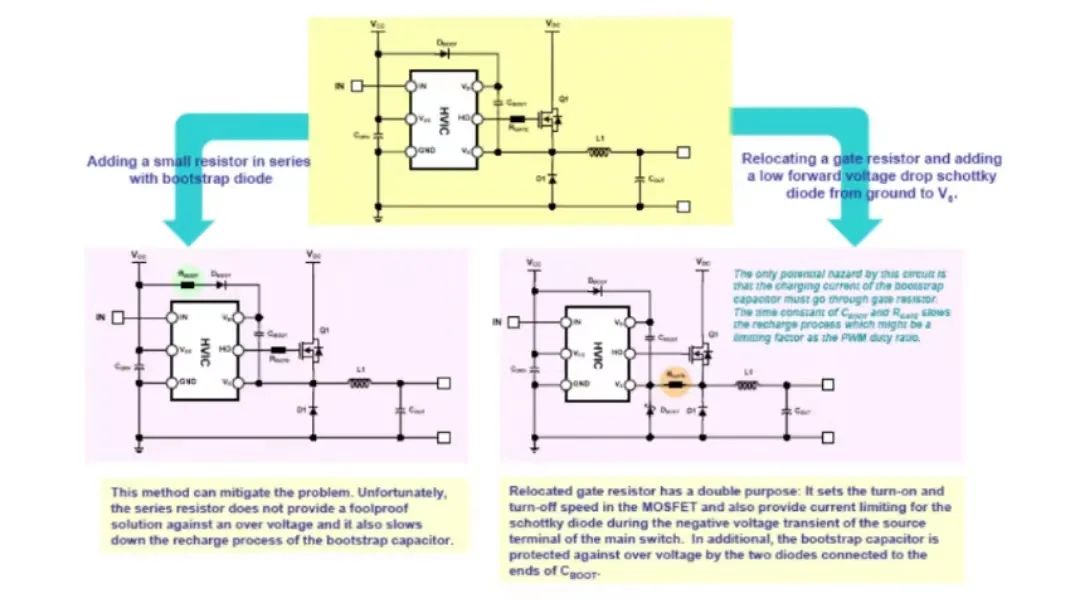

еҰӮеӣҫ1жүҖзӨәпјҢиҮӘдёҫз”өи·ҜеҜ№дәҺй«ҳз”өеҺӢж …жһҒй©ұеҠЁеҷЁжҳҜеҫҲжңүз”Ёзҡ„гҖӮдҪҶжҳҜпјҢеҪ“дё»иҰҒ MOSFET (Q1)зҡ„жәҗжһҒе’ҢиҮӘдёҫз”өе®№(CBOOT)зҡ„иҙҹеҒҸзҪ®иҠӮзӮ№дҪҚдәҺиҫ“еҮәз”өеҺӢж—¶пјҢе®ғжңүеҜ№иҮӘдёҫз”өе®№иҝӣиЎҢеҲқе§ӢеҢ–еҗҜеҠЁе’Ңе……з”өеҸ—йҷҗзҡ„й—®йўҳгҖӮеҗҜеҠЁж—¶пјҢиҮӘдёҫдәҢжһҒз®Ў(DBOOT)еҸҜиғҪеӨ„дәҺеҸҚеҒҸпјҢдё»иҰҒ MOSFET (Q1)зҡ„еҜјйҖҡж—¶й—ҙдёҚи¶іпјҢиҮӘдёҫз”өе®№дёҚиғҪдҝқжҢҒжүҖйңҖиҰҒзҡ„з”өиҚ·пјҢеҰӮеӣҫ1жүҖзӨәгҖӮ

В

еңЁжҹҗдәӣеә”з”ЁдёӯпјҢеҰӮз”өжұ е……з”өеҷЁпјҢиҫ“еҮәз”өеҺӢеңЁиҫ“е…Ҙз”өжәҗеҠ иҪҪеҲ°иҪ¬жҚўеҷЁд№ӢеүҚеҸҜиғҪе·Із»ҸеӯҳеңЁдәҶгҖӮз»ҷиҮӘдёҫз”өе®№(CBOOT)жҸҗдҫӣеҲқе§Ӣз”өиҚ·д№ҹи®ёжҳҜдёҚеҸҜиғҪзҡ„пјҢиҝҷеҸ–еҶідәҺз”өжәҗз”өеҺӢпјҲVDDпјүе’Ңиҫ“еҮәз”өеҺӢ(VOUT)д№Ӣй—ҙзҡ„з”өеҺӢе·®гҖӮеҒҮи®ҫиҫ“е…Ҙз”өеҺӢ(VDCе’Ңиҫ“еҮәз”өеҺӢпјҲVOUT)д№Ӣй—ҙжңүи¶іеӨҹзҡ„з”өеҺӢе·®пјҢз”ұеҗҜеҠЁз”өйҳ»(RSTART)пјҢеҗҜеҠЁдәҢжһҒз®Ў(DSTART)е’ҢйҪҗзәідәҢжһҒз®Ў(DSTART)з»„жҲҗзҡ„з”өи·ҜпјҢеҸҜд»Ҙи§ЈеҶіиҝҷдёӘй—®йўҳпјҢеҰӮеӣҫ14жүҖзӨәгҖӮ

В

еңЁжӯӨеҗҜеҠЁз”өи·ҜдёӯпјҢеҗҜеҠЁдәҢжһҒз®Ў DSTART е……еҪ“ж¬ЎиҮӘдёҫдәҢжһҒз®ЎпјҢеңЁдёҠз”өж—¶еҜ№иҮӘдёҫз”өе®№(CBOOT)е……з”өгҖӮиҮӘдёҫз”өе®№(CBOOT)е……з”өеҗҺпјҢиҝһжҺҘеҲ°йҪҗзәідәҢжһҒз®Ў Dz пјҢеңЁжӯЈеёёе·ҘдҪңж—¶пјҢиҝҷдёӘз”өеҺӢеә”иҜҘеӨ§дәҺй©ұеҠЁеҷЁзҡ„з”өжәҗз”өеҺӢ(VDD)гҖӮеҗҜеҠЁз”өйҳ»йҷҗеҲ¶дәҶиҮӘдёҫз”өе®№зҡ„е……з”өз”өжөҒе’ҢйҪҗзәіз”өжөҒгҖӮдёәдәҶиҺ·еҫ—жңҖеӨ§зҡ„ж•ҲзҺҮпјҢеә”иҜҘйҖүжӢ©еҗҲйҖӮзҡ„еҗҜеҠЁз”өйҳ»еҖјдҪҝз”өжөҒжһҒдҪҺпјҢеӣ дёәз”өи·ҜдёӯйҖҡиҝҮеҗҜеҠЁдәҢжһҒз®Ўзҡ„иҮӘдёҫи·Ҝеҫ„жҳҜдёҚеҸҳзҡ„гҖӮ

В

В

еӣҫ14В з®ҖеҚ•зҡ„иҮӘдёҫеҗҜеҠЁз”өи·Ҝ

В

иҮӘдёҫдәҢжһҒз®ЎдёІиҒ”з”өйҳ»

В

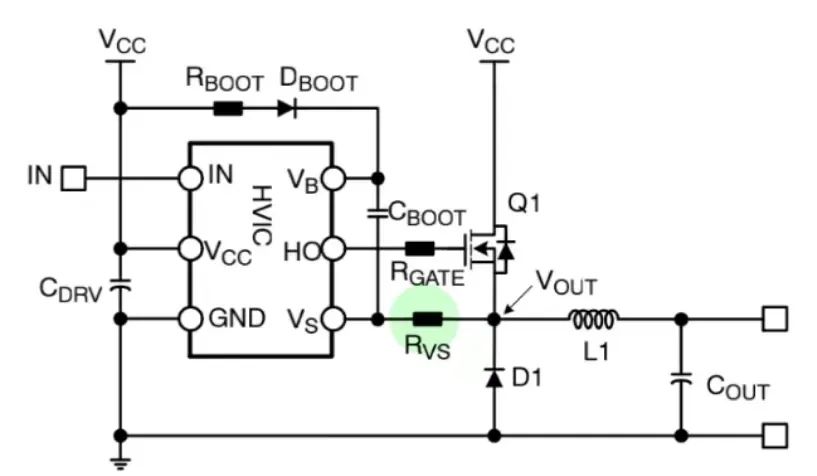

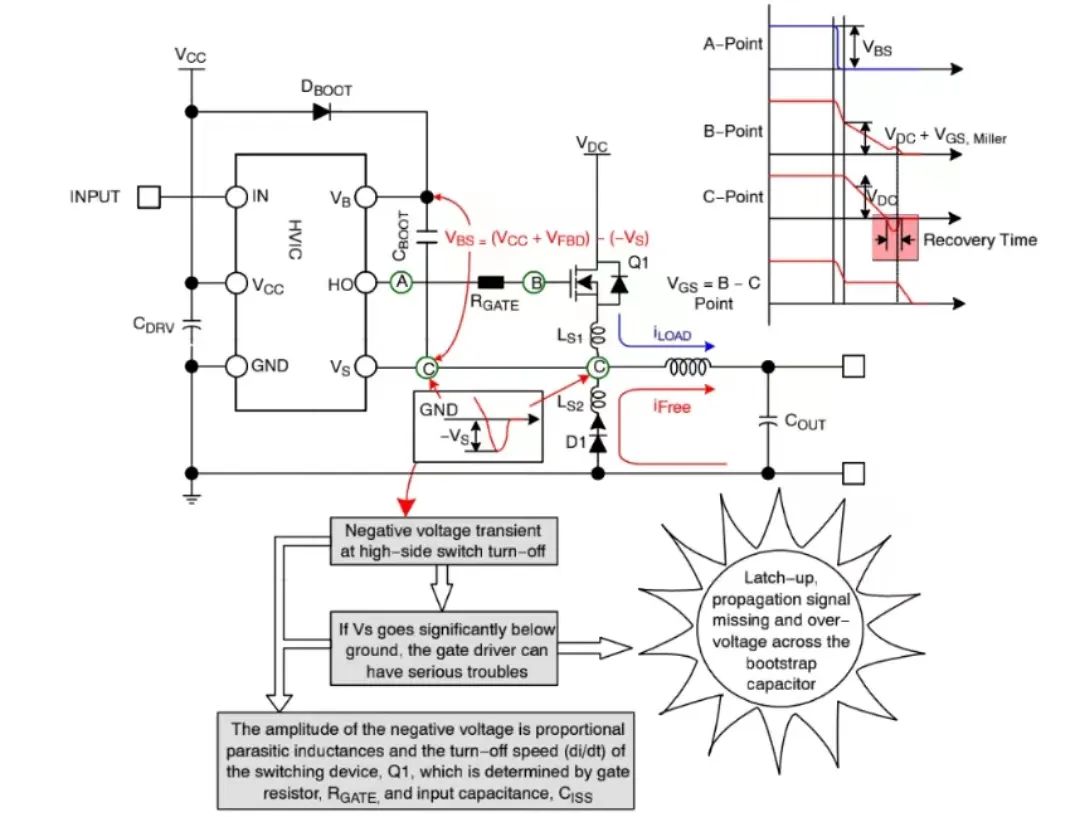

еңЁз¬¬дёҖдёӘйҖүйЎ№дёӯпјҢиҮӘдёҫз”өи·ҜеҢ…жӢ¬дёҖдёӘе°Ҹз”өйҳ»пјҢ RBOOT пјҢе®ғдёІиҒ”дәҶдёҖдёӘиҮӘдёҫдәҢжһҒз®ЎпјҢеҰӮеӣҫ15жүҖзӨәгҖӮиҮӘдёҫз”өйҳ» RBOOT пјҢд»…еңЁиҮӘдёҫе……з”өе‘Ёжңҹз”ЁжқҘйҷҗжөҒгҖӮиҮӘдёҫе……з”өе‘ЁжңҹиЎЁзӨә Vs йҷҚеҲ°йӣҶжҲҗз”өи·Ҝз”өжәҗз”өеҺӢ VDD д»ҘдёӢпјҢжҲ–иҖ… Vs иў«жӢүдҪҺеҲ°ең°(дёӢжЎҘејҖе…іеҜјйҖҡпјҢдёҠжЎҘејҖе…іе…ій—ӯ)гҖӮз”өжәҗ Vcc пјҢйҖҡиҝҮиҮӘдёҫз”өйҳ» RBOOTе’ҢдәҢжһҒз®Ў DBOOT пјҢеҜ№иҮӘдёҫз”өе®№ CBOOT е……з”өгҖӮиҮӘдёҫдәҢжһҒз®Ўзҡ„еҮ»з©ҝз”өеҺӢ( BV)еҝ…йЎ»еӨ§дәҺ VDC пјҢдё”е…·жңүеҝ«йҖҹжҒўеӨҚж—¶й—ҙпјҢд»ҘдҫҝжңҖе°ҸеҢ–д»ҺиҮӘдёҫз”өе®№еҲ° Vcc з”өжәҗзҡ„з”өиҚ·еҸҚйҰҲйҮҸгҖӮ

В

В

еӣҫ15В ж·»еҠ дёҖдёӘдёІиҒ”DBOOTзҡ„з”өйҳ»

В

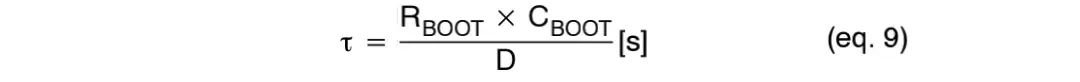

иҝҷжҳҜдёҖз§Қз®ҖеҚ•зҡ„пјҢйҷҗеҲ¶иҮӘдёҫз”өе®№еҲқж¬Ўе……з”өз”өжөҒзҡ„ж–№жі•пјҢдҪҶжҳҜе®ғд№ҹжңүдёҖдәӣзјәзӮ№гҖӮеҚ з©әжҜ”еҸ—йҷҗдәҺиҮӘдёҫз”өе®№ CBOOTеҲ·ж–°з”өиҚ·жүҖйңҖиҰҒзҡ„ж—¶й—ҙпјҢиҝҳжңүеҗҜеҠЁй—®йўҳгҖӮдёҚиҰҒи¶…иҝҮ欧е§ҶеҖј(е…ёеһӢеҖј5~10 О©)пјҢе°ҶдјҡеўһеҠ VBS ж—¶й—ҙеёёж•°гҖӮжңҖдҪҺеҜјйҖҡж—¶й—ҙпјҢеҚіз»ҷиҮӘдёҫз”өе®№е……з”өжҲ–еҲ·ж–°з”өиҚ·зҡ„ж—¶й—ҙпјҢеҝ…йЎ»еҢ№й…ҚиҝҷдёӘж—¶й—ҙеёёж•°гҖӮиҜҘж—¶й—ҙеёёж•°еҸ–еҶідәҺиҮӘдёҫз”өйҳ»пјҢиҮӘдёҫз”өе®№е’ҢејҖе…іеҷЁд»¶зҡ„еҚ з©әжҜ”пјҢз”ЁдёӢйқўзҡ„зӯүејҸи®Ўз®—пјҡ

В

В

е…¶дёӯRBOOTжҳҜиҮӘдёҫз”өйҳ»пјӣ CBOOTжҳҜиҮӘдёҫз”өе®№пјӣ D жҳҜеҚ з©әжҜ”гҖӮ

В

дҫӢеҰӮпјҢеҰӮжһң RBOOT=10,РЎBOOT=1 ОјF , D =10%;ж—¶й—ҙеёёж•°йҖҡиҝҮдёӢејҸи®Ўз®—пјҡ

В

В

еҚідҪҝиҝһжҺҘдёҖдёӘеҗҲзҗҶзҡ„еӨ§иҮӘдёҫз”өе®№е’Ңз”өйҳ»пјҢиҜҘж—¶й—ҙеёёж•°еҸҜиғҪеўһеӨ§гҖӮиҝҷз§Қж–№жі•иғҪеӨҹзј“и§ЈиҝҷдёӘй—®йўҳгҖӮдёҚе№ёзҡ„жҳҜпјҢиҜҘдёІиҒ”з”өйҳ»дёҚиғҪи§ЈеҶіиҝҮз”өеҺӢзҡ„й—®йўҳпјҢ并且еҮҸзј“дәҶиҮӘдёҫз”өе®№зҡ„йҮҚж–°е……з”өиҝҮзЁӢгҖӮ

В

VSВ дёҺ VOUT д№Ӣй—ҙзҡ„з”өйҳ»

В

еңЁз¬¬дәҢдёӘйҖүйЎ№дёӯпјҢиҮӘдёҫз”өи·Ҝзҡ„ VS е’Ң VOUT д№Ӣй—ҙпјҢж·»еҠ дёҠдёҖдёӘе°Ҹз”өйҳ» RVS пјҢеҰӮеӣҫ16жүҖзӨәгҖӮRVSзҡ„е»әи®®еҖјеңЁеҮ дёӘ欧е§Ҷе·ҰеҸігҖӮ

В

В

еӣҫ16В еңЁиҮӘдёҫз”өи·ҜдёӯпјҢеўһеҠ RVSВ

В

RVSдёҚд»…з”ЁдҪңиҮӘдёҫз”өйҳ»пјҢиҝҳз”ЁдҪңеҜјйҖҡз”өйҳ»е’Ңе…іж–ӯз”өйҳ»пјҢеҰӮеӣҫ17гҖӮиҮӘдёҫз”өйҳ»пјҢеҜјйҖҡз”өйҳ»е’Ңе…іж–ӯз”өйҳ»йҖҡиҝҮдёӢйқўзҡ„зӯүејҸи®Ўз®—пјҡ

В

В

еӣҫ17В еҜјйҖҡе’Ңе…іж–ӯзҡ„з”өжөҒи·Ҝеҫ„

В

VSз®қеҺӢдәҢжһҒз®Ўе’ҢйҮҚеёғзҪ®ж …жһҒз”өйҳ»

В

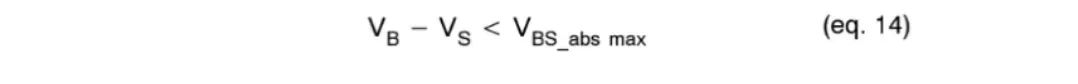

еңЁз¬¬дёүдёӘйҖүйЎ№дёӯпјҢиҮӘдёҫз”өи·ҜжҠҠж …жһҒз”өйҳ»йҮҚж–°еёғзҪ®еҲ° VSе’Ң VOUT д№Ӣй—ҙпјҢ并且еңЁ VSе’Ңең°д№Ӣй—ҙеўһеҠ дёҖдёӘдҪҺжӯЈеҗ‘еҺӢйҷҚзҡ„иӮ–зү№еҹәдәҢжһҒз®ЎпјҢеҰӮеӣҫ18жүҖдёҚгҖӮ VB е’Ң VSд№Ӣй—ҙзҡ„з”өеҺӢе·®пјҢеә”дҝқжҢҒеңЁж•°жҚ®иЎЁи§„е®ҡзҡ„з»қеҜ№жңҖеӨ§йўқе®ҡеҖјиҢғеӣҙеҶ…пјҢ并且еҝ…йЎ»з¬ҰеҗҲдёӢеҲ—зӯүејҸпјҡ

В

В

еӣҫ18В з®қдҪҚз»“жһ„

В

йҮҚеёғзҪ®ж …жһҒз”өйҳ»пјӣеҸҢйҮҚзӣ®зҡ„

В

ж …жһҒз”өйҳ»и®ҫзҪ®дәҶMOSFETзҡ„еҜјйҖҡйҖҹеәҰе’Ңе…іж–ӯйҖҹеәҰпјҢйҷҗеҲ¶дәҶеңЁдё»ејҖе…іжәҗжһҒзҡ„з”өеҺӢиҙҹеҗ‘зһ¬жҖҒж—¶пјҢиӮ–зү№еҹәдәҢжһҒз®Ўзҡ„з”өжөҒгҖӮеҸҰеӨ–пјҢиҝһжҺҘеҲ° CBOOTдёӨз«Ҝзҡ„еҸҢдәҢжһҒз®ЎпјҢзЎ®дҝқиҮӘдёҫз”өе®№дёҚдјҡеҮәзҺ°иҝҮз”өеҺӢгҖӮиҜҘз”өи·Ҝе”ҜдёҖзҡ„жҪңеңЁеҚұйҷ©жҳҜпјҢиҮӘдёҫз”өе®№зҡ„е……з”өз”өжөҒеҝ…йЎ»жөҒиҝҮж …жһҒз”өйҳ»гҖӮ CBOOT е’Ң RGATE зҡ„ж—¶й—ҙеёёж•°еҮҸзј“еҶҚе……з”өиҝҮзЁӢпјҢеҸҜиғҪжҲҗдёә PWM еҚ з©әжҜ”зҡ„йҷҗеҲ¶еӣ ж•°гҖӮ

В

第еӣӣдёӘйҖүжӢ©пјҢеҢ…жӢ¬еңЁ VS е’Ң VOUT д№Ӣй—ҙпјҢйҮҚж–°еёғзҪ®дёҖдёӘж …жһҒз”өйҳ»пјҢд»ҘеҸҠеңЁ VS е’Ңең°д№Ӣй—ҙж”ҫзҪ®дёҖдёӘз®қеҺӢеҷЁд»¶пјҢеҰӮеӣҫ19жүҖзӨәпјҢеёғзҪ®дәҶдёҖдёӘйҪҗзәідәҢжһҒз®Ўе’Ң600 V дәҢжһҒз®ЎгҖӮж №жҚ®дёӢеҲ—规еҲҷпјҢйҮҸеҢ–йҪҗзәіз”өеҺӢпјҡ

В

В

еӣҫ19В еёҰйҪҗзәідәҢжһҒз®Ўзҡ„з®қеҺӢз»“жһ„

В

йҖүжӢ© HVIC з”өжөҒиғҪеҠӣ

В

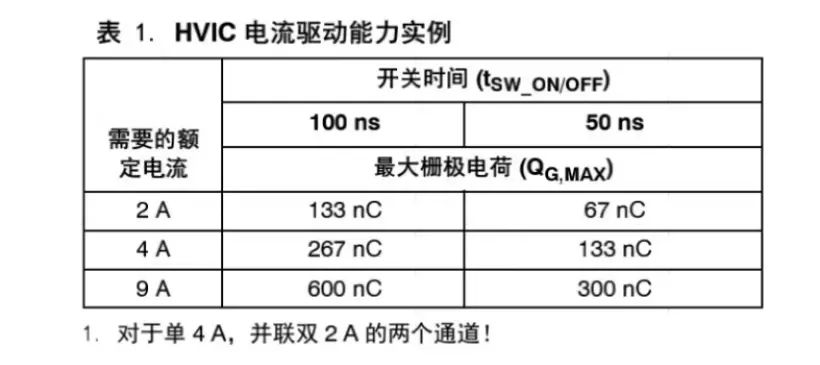

еҜ№дәҺжҜҸдёҖз§Қйўқе®ҡй©ұеҠЁз”өжөҒпјҢи®Ўз®—жҢҮе®ҡж—¶й—ҙеҶ…жүҖиғҪеҲҮжҚўзҡ„жңҖеӨ§ж …жһҒз”өиҚ·QGпјҢеҰӮиЎЁ1жүҖзӨәгҖӮ

В

В

дҫӢеҰӮпјҢ100 ns зҡ„ејҖе…іж—¶й—ҙжҳҜпјҡ

В

100 kHz ж—¶иҪ¬жҚўеҷЁејҖе…іе‘Ёжңҹзҡ„1%;

300 kHz ж—¶иҪ¬жҚўеҷЁејҖе…іе‘Ёжңҹзҡ„3%пјӣд»ҘжӯӨзұ»жҺЁгҖӮ

В

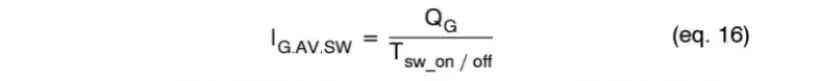

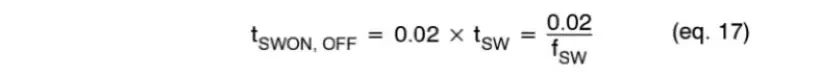

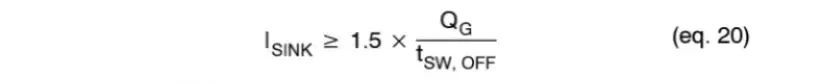

1пјҺжүҖйңҖзҡ„йўқе®ҡж …жһҒй©ұеҠЁз”өжөҒеҸ–еҶідәҺеңЁејҖе…іж—¶tSW - ON / OFF еҶ…пјҢеҝ…须移еҠЁзҡ„ж …жһҒз”өиҚ·ж•°QGпјҲеӣ дёәејҖе…іжңҹй—ҙзҡ„е№іеқҮж …жһҒз”өжөҒжҳҜIG):

В

В

2пјҺжңҖеӨ§ж …жһҒз”өиҚ· QG пјҢд»ҺMOSFETж•°жҚ®иЎЁеҫ—еҲ°гҖӮ

В

еҰӮжһңе®һйҷ…ж …жһҒй©ұеҠЁз”өеҺӢ VGSдёҺи§„ж јиЎЁдёҠзҡ„жөӢиҜ•жқЎд»¶дёҚеҗҢпјҢдҪҝз”Ё VGS дёҺ QG жӣІзәҝгҖӮж•°жҚ®иЎЁдёӯзҡ„еҖјд№ҳдёҠ并иҒ”зҡ„MOSFETж•°йҮҸе°ұжҳҜжүҖйңҖзҡ„еҖјгҖӮ

В

3.tSW ON / OFF иЎЁзӨәжүҖйңҖзҡ„MOSFETејҖе…ійҖҹеәҰгҖӮеҰӮжһңиҜҘеҖјжңӘзҹҘпјҢеҸ–ејҖе…іе‘Ёжңҹ tSWзҡ„2%:

В

В

еҰӮжһңйҖҡйҒ“пјҲV -IпјүејҖе…іжҚҹиҖ—дё»иҰҒеҸ—ејҖе…іиҪ¬жҚўпјҲеҜјйҖҡжҲ–е…іж–ӯпјүж”Ҝй…ҚпјҢйңҖиҰҒж №жҚ®иҪ¬жҚўи°ғж•ҙй©ұеҠЁеҷЁгҖӮеҜ№дәҺеҸ—зұҚеҲ¶зҡ„з”өж„ҹжҖ§ејҖе…іпјҲйҖҡеёёжғ…еҶөпјүпјҢжҜҸж¬ЎиҪ¬жҚўзҡ„йҖҡйҒ“ејҖе…іжҚҹиҖ—дј°з®—еҰӮдёӢпјҡ

В

В

е…¶дёӯVDSе’ҢIDжҳҜжҜҸдёӘејҖе…ій—ҙжңҹзҡ„жңҖеӨ§еҖјгҖӮ

В

4пјҺж …жһҒй©ұеҠЁеҷЁзҡ„иҝ‘дјјз”өжөҒй©ұеҠЁиғҪеҠӣи®Ўз®—еҰӮдёӢ

В

В a .жӢүз”өжөҒиғҪеҠӣпјҲеҜјйҖҡпјү

В

В

b пјҺзҒҢз”өжөҒиғҪеҠӣпјҲе…іж–ӯпјү

В

В

е…¶дёӯпјҡ

В

В QGВ = VGS = VDD ж—¶пјҢ

В

В MOSFET зҡ„ж …жһҒз”өиҚ·пјӣ

В

В tSW _ ON / OFF = MOSFET ејҖе…іеҜјйҖҡпјҸе…іж–ӯж—¶й—ҙпјӣ

В

е’Ң

В

1.5пјқз»ҸйӘҢеӣ еӯҗпјҲеҸ—йҖҡиҝҮй©ұеҠЁеҷЁиҫ“е…Ҙзә§зҡ„延иҝҹе’ҢеҜ„з”ҹж•Ҳеә”зҡ„еҪұе“Қпјү

В

ж …жһҒз”өйҳ»и®ҫи®ЎжөҒзЁӢ

В

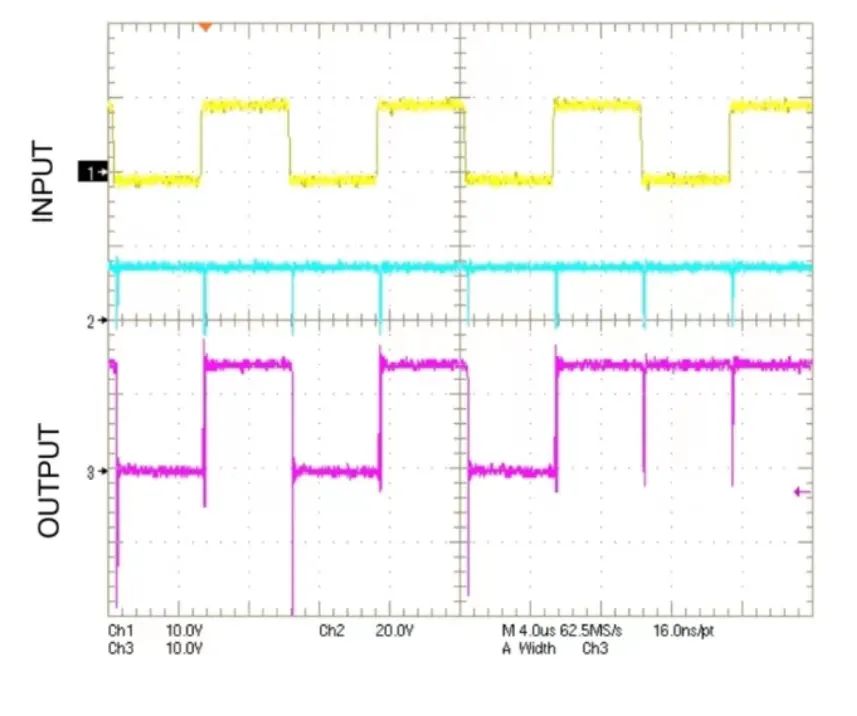

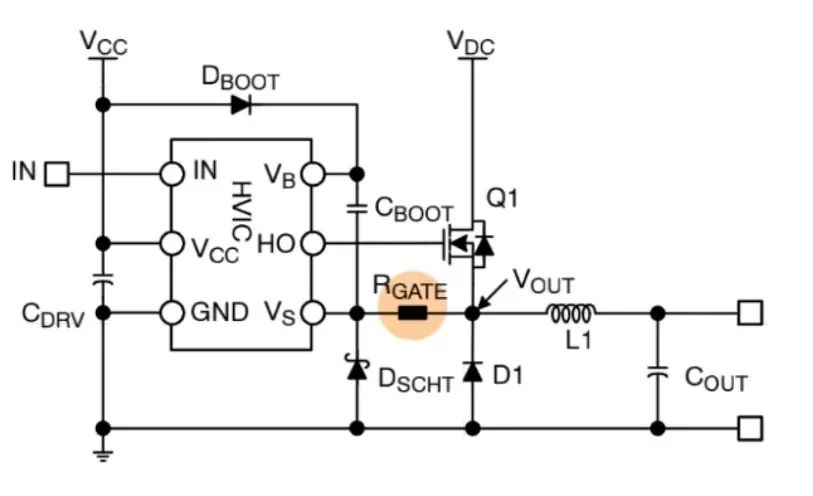

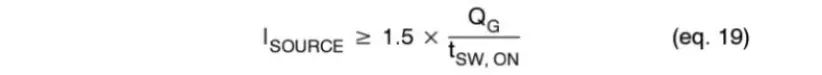

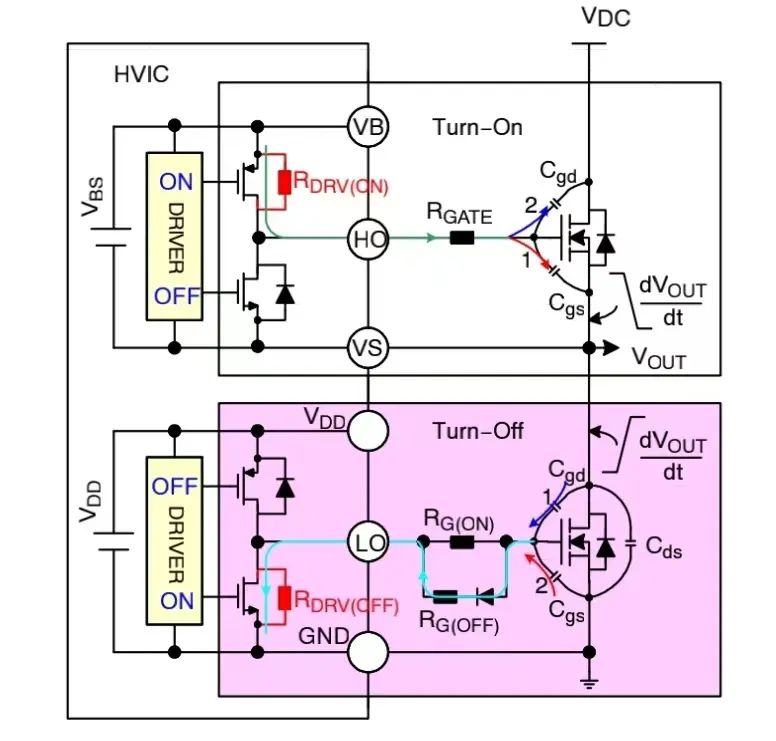

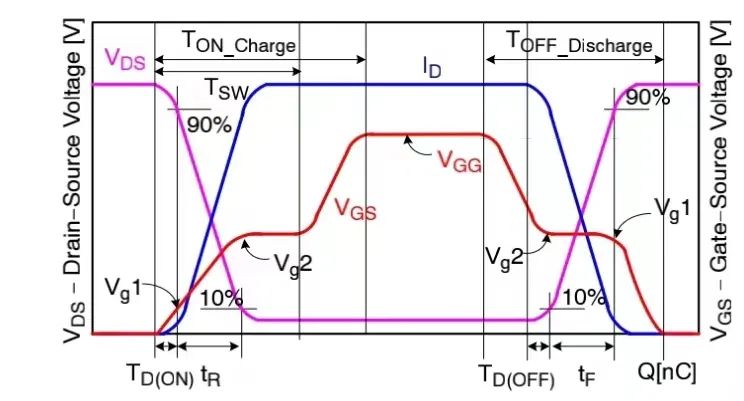

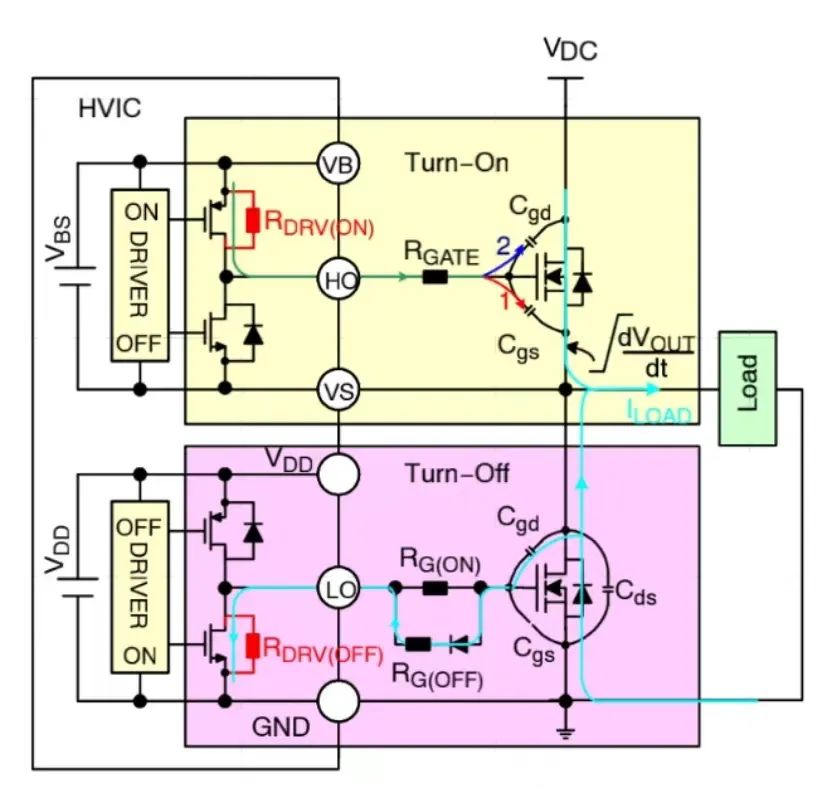

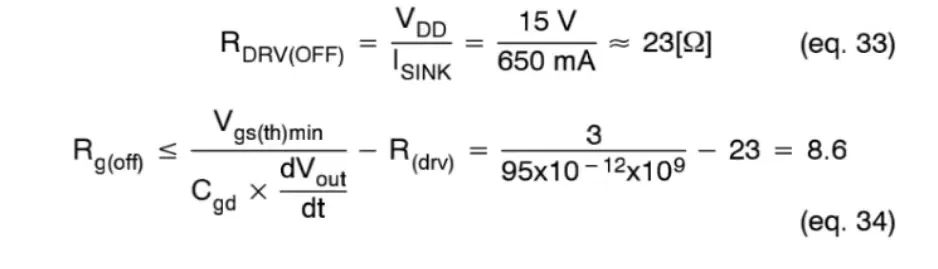

иҫ“еҮәжҷ¶дҪ“з®Ўзҡ„ејҖе…ійҖҹеәҰеҸ—еҜјйҖҡе’Ңе…іж–ӯж …жһҒз”өйҳ»зҡ„жҺ§еҲ¶пјҢиҝҷдәӣз”өйҳ»жҺ§еҲ¶дәҶж …жһҒй©ұеҠЁеҷЁзҡ„еҜјйҖҡе’Ңе…іж–ӯз”өжөҒгҖӮжң¬иҠӮжҸҸиҝ°дәҶжңүе…іж …жһҒз”өйҳ»зҡ„еҹәжң¬и§„еҲҷпјҢйҖҡиҝҮеј•е…Ҙж …жһҒй©ұеҠЁеҷЁзҡ„зӯүж•Ҳиҫ“еҮәз”өйҳ»жқҘиҺ·еҸ–жүҖйңҖзҡ„ејҖе…іж—¶й—ҙе’ҢйҖҹеәҰгҖӮеӣҫ20жҸҸиҝ°дәҶж …жһҒй©ұеҠЁеҷЁзҡ„зӯүж•Ҳз”өи·Ҝе’ҢеңЁеҜјйҖҡе’Ңе…іж–ӯжңҹй—ҙзҡ„з”өжөҒжөҒеҠЁи·Ҝеҫ„пјҢе…¶дёӯеҢ…жӢ¬ж …жһҒй©ұеҠЁеҷЁе’ҢејҖе…іеҷЁд»¶гҖӮ

В

В

еӣҫ20В ж …жһҒй©ұеҠЁеҷЁзҡ„зӯүж•Ҳз”өи·Ҝ

В

еӣҫ21жҳҫзӨәдәҶејҖе…іеҷЁд»¶еңЁеҜјйҖҡе’Ңе…іж–ӯжңҹй—ҙзҡ„ж …жһҒдёҖз”өиҚ·дј иҫ“зү№жҖ§гҖӮ

В

В

еӣҫ21В ж …жһҒз”өиҚ·дј иҫ“зү№жҖ§

В

йҮҸеҢ–еҜјйҖҡж …жһҒз”өйҳ»

В

ж №жҚ®ејҖе…іж—¶й—ҙ tswВ пјҢйҖүжӢ©еҜјйҖҡй—ёжһҒз”өйҳ» Rg ( ON ),д»ҘиҺ·еҫ—жүҖйңҖзҡ„ејҖе…іж—¶й—ҙгҖӮж №жҚ®ејҖе…іж—¶й—ҙзЎ®е®ҡз”өйҳ»еҖјж—¶пјҢжҲ‘们йңҖиҰҒзҹҘйҒ“з”өжәҗз”өеҺӢ VDD(жҲ–VBS)пјҢж …жһҒй©ұеҠЁеҷЁзҡ„зӯүж•ҲеҜјйҖҡз”өйҳ»(RDRV ( ON ))пјҢе’ҢејҖе…іеҷЁд»¶зҡ„еҸӮж•°(Qgs Qgd пјҢе’Ң Vgs ( th ))

В

ејҖе…іж—¶й—ҙе®ҡд№үдёәеҲ°иҫҫеқӘз”өеҺӢпјҲз»ҷ MOSFET жҸҗдҫӣдәҶжҖ»е…ұ Qgs + Qgd зҡ„з”өиҚ·пјүжң«з«ҜжүҖиҠұиҙ№зҡ„ж—¶й—ҙпјҢеҰӮеӣҫ21жүҖзӨәгҖӮ

В

еҜјйҖҡж …жһҒз”өйҳ»и®Ўз®—еҰӮдёӢпјҡ

В

В

е…¶дёӯ Rg ( ON пјүжҳҜж …жһҒеҜјйҖҡз”өйҳ»пјҢ RDRv ( ON пјүжҳҜй©ұеҠЁеҷЁзҡ„зӯүж•ҲеҜјйҖҡз”өйҳ»гҖӮ

В

иҫ“еҮәз”өеҺӢж–ңзҺҮ

В

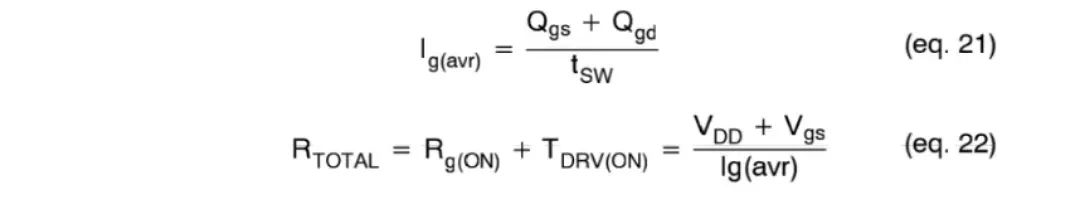

еҜјйҖҡж …жһҒз”өйҳ» Rg ( ON пјүйҖҡиҝҮжҺ§еҲ¶иҫ“еҮәз”өеҺӢж–ңзҺҮ(dVOUT/ dt)жқҘеҶіе®ҡгҖӮеҪ“иҫ“еҮәз”өеҺӢжҳҜйқһзәҝжҖ§ж—¶пјҢжңҖеӨ§иҫ“еҮәз”өеҺӢж–ңзҺҮеҸҜд»Ҙиҝ‘дјјдёәпјҡ

В

В

жҸ’е…ҘеҸҳеҪўиЎЁиҫҫејҸ Ig ( avr ),并ж•ҙзҗҶеҫ—еҲ°пјҡ

В

В

е…¶дёӯ Cgd ( off )жҳҜеҜҶеӢ’ж•Ҳеә”з”өе®№пјҢеңЁж•°жҚ®иЎЁдёӯе®ҡд№үдёәCrssгҖӮ

В

йҮҸеҢ–е…іж–ӯж …жһҒз”өйҳ»

В

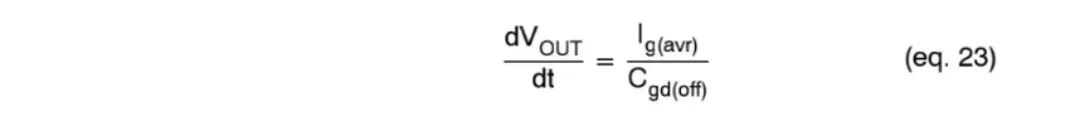

еңЁйҮҸеҢ–е…іж–ӯз”өйҳ»ж—¶пјҢжңҖеқҸзҡ„жғ…еҶөжҳҜеҪ“MOSFETжјҸжһҒеӨ„дәҺе…іж–ӯж—¶пјҢеӨ–йғЁеҠЁдҪңиҝ«дҪҝз”өйҳ»ж•ҙжөҒеҷЁгҖӮ

В

еңЁиҝҷз§Қжғ…еҶөдёӢпјҢиҫ“еҮәиҠӮзӮ№зҡ„ dv / dt пјҢиҜұеҜјдёҖиӮЎеҜ„з”ҹз”өжөҒз©ҝиҝҮ Cgd пјҢжөҒеҗ‘ RG ( OFF пјүе’Ң RDRV ( OFF )пјҢеҰӮеӣҫ22жүҖзӨәгҖӮ

В

дёӢйқўйҳҗиҝ°дәҶпјҢеҪ“иҫ“еҮә dv / dt жҳҜз”ұдјҙйҡҸMOSFETзҡ„еҜјйҖҡйҖ жҲҗж—¶пјҢеҰӮдҪ•йҮҸеҢ–е…іж–ӯз”өйҳ»пјҢеҰӮеӣҫ22зӨәгҖӮ

В

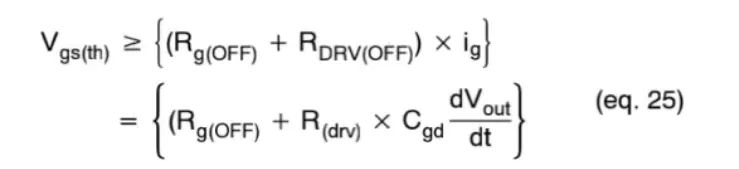

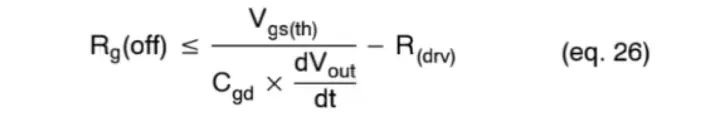

еӣ дёәиҝҷдёӘеҺҹеӣ пјҢе…іж–ӯйҳ»жҠ—еҝ…йЎ»ж №жҚ®жңҖеқҸзҡ„еә”з”Ёжғ…еҶөжқҘйҮҸеҢ–гҖӮдёӢйқўзҡ„зӯүејҸе°ҶMOSFETж …жһҒйҳҲеҖјз”өеҺӢе’ҢжјҸжһҒ dv / dt е…іиҒ”иө·жқҘпјҡ

В

В

еӣҫ22В з”өжөҒи·Ҝеҫ„пјҡдёӢжЎҘејҖе…іе…іж–ӯпјҢдёҠжЎҘејҖе…іеҜјйҖҡ

В

В

йҮҚж–°ж•ҙзҗҶиЎЁиҫҫејҸеҫ—еҲ°пјҡ

В

В

и®ҫи®Ўе®һдҫӢ

В

дҪҝз”ЁйЈһе…ҶMOSFET FCP20N60е’Ңж …жһҒй©ұеҠЁеҷЁFAN7382пјҢзЎ®е®ҡеҜјйҖҡе’Ңе…іж–ӯж …жһҒз”өйҳ»гҖӮFCP20N60еҠҹзҺҮMOSFETзҡ„еҸӮж•°еҰӮдёӢпјҡ

В

В

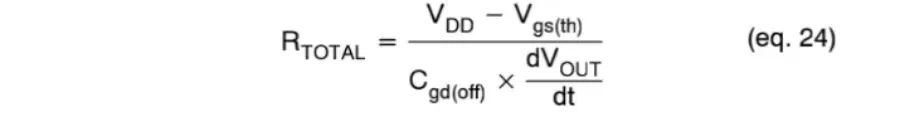

еҜјйҖҡж …жһҒз”өйҳ»

В

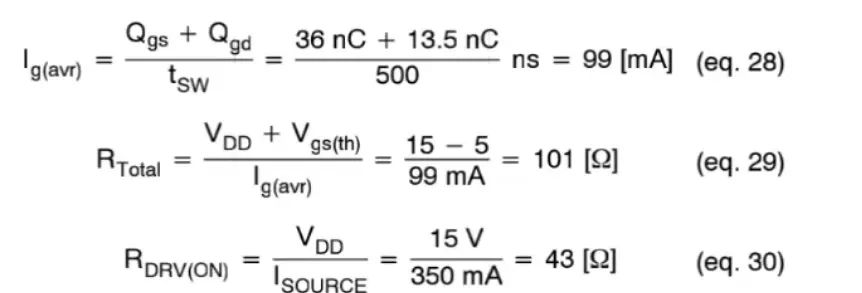

1пјҺеҰӮжһңVDD =15 V ж—¶пјҢжүҖйңҖзҡ„ејҖе…іж—¶й—ҙжҳҜ500 ns пјҢи®Ўз®—е№іеқҮж …жһҒе……з”өз”өжөҒпјҡ

В

В

еҜјйҖҡз”өйҳ»еҖјзәҰдёә58 О©гҖӮ

В

2пјҺеҰӮжһң dVout/ dt =1 V / ns (VDD =15 V ж—¶)пјҢжҖ»ж …жһҒз”өйҳ»еҰӮдёӢи®Ўз®—пјҡ

В

В

еҜјйҖҡз”өйҳ»еҖјзәҰдёә62 О©

В

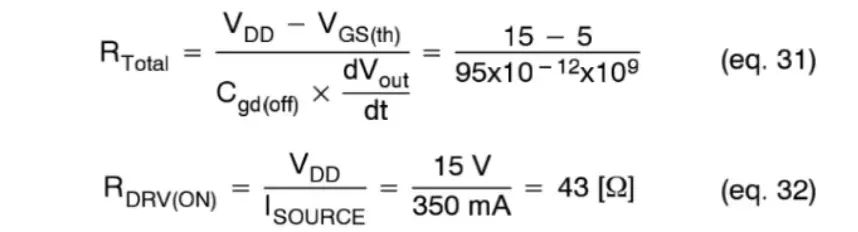

е…іж–ӯж …жһҒз”өйҳ»

В

еҰӮжһң dVout / dt =1 V / ns пјҢе…іж–ӯж …жһҒз”өйҳ»еҸҜи®Ўз®—дёәпјҡ

В

В

04

иҖғиҷ‘еҠҹиҖ—

В

ж …жһҒй©ұеҠЁеҷЁзҡ„еҠҹиҖ—

В

жҖ»зҡ„еҠҹиҖ—еҢ…жӢ¬ж …жһҒй©ұеҠЁеҷЁеҠҹиҖ—е’ҢиҮӘдёҫдәҢжһҒз®ЎеҠҹиҖ—гҖӮж …жһҒй©ұеҠЁеҷЁеҠҹиҖ—з”ұйқҷжҖҒеҠҹиҖ—е’ҢеҠЁжҖҒеҠҹиҖ—дёӨйғЁеҲҶз»„жҲҗгҖӮе®ғдёҺејҖе…ійў‘зҺҮпјҢдёҠжЎҘе’ҢдёӢжЎҘй©ұеҠЁеҷЁзҡ„иҫ“еҮәиҙҹиҪҪз”өе®№пјҢд»ҘеҸҠз”өжәҗ VDD жңүе…ігҖӮ

В

йқҷжҖҒеҠҹиҖ—жҳҜеӣ дёәдёӢжЎҘй©ұеҠЁеҷЁзҡ„з”өжәҗ VDD еҲ°ең°зҡ„йқҷжҖҒз”өжөҒпјҢд»ҘеҸҠдёҠжЎҘй©ұеҠЁеҷЁзҡ„з”өе№іиҪ¬жҚўйҳ¶ж®өзҡ„жјҸз”өжөҒйҖ жҲҗзҡ„гҖӮеүҚиҖ…еҸ–еҶідәҺ VS з«Ҝзҡ„з”өеҺӢпјҢеҗҺиҖ…д»…еңЁдёҠжЎҘеҠҹзҺҮеҷЁд»¶еҜјйҖҡж—¶дёҺеҚ з©әжҜ”жҲҗжӯЈжҜ”гҖӮ

В

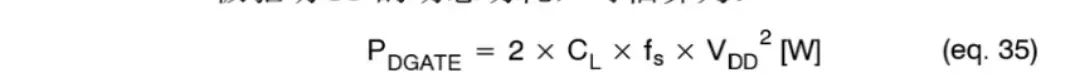

еҠЁжҖҒеҠҹиҖ—е®ҡд№үеҰӮдёӢпјҡеҜ№дәҺдёӢжЎҘй©ұеҠЁеҷЁпјҢеҠЁжҖҒеҠҹиҖ—жңүдёӨдёӘдёҚеҗҢзҡ„жқҘжәҗгҖӮдёҖжҳҜеҪ“иҙҹиҪҪз”өе®№йҖҡиҝҮж …жһҒз”өйҳ»е……з”өжҲ–ж”ҫз”өж—¶пјҢиҝӣе…Ҙз”өе®№зҡ„з”өиғҪжңүдёҖеҚҠиҖ—ж•ЈеңЁз”өйҳ»дёҠгҖӮж …жһҒй©ұеҠЁз”өйҳ»зҡ„еҠҹиҖ—пјҢж …жһҒй©ұеҠЁеҷЁеҶ…йғЁзҡ„е’ҢеӨ–йғЁзҡ„пјҢд»ҘеҸҠеҶ…йғЁ CMOS з”өи·Ҝзҡ„ејҖе…іеҠҹиҖ—гҖӮеҗҢж—¶пјҢдёҠжЎҘй©ұеҠЁеҷЁзҡ„еҠЁжҖҒеҠҹиҖ—д№ҹеҢ…жӢ¬дёӨдёӘдёҚеҗҢзҡ„жқҘжәҗгҖӮдёҖдёӘжҳҜеӣ дёәз”өе№іиҪ¬жҚўз”өи·ҜпјҢдёҖдёӘжҳҜеӣ дёәдёҠжЎҘз”өе®№зҡ„е……з”өе’Ңж”ҫз”өгҖӮиҝҷйҮҢпјҢеҸҜд»ҘеҝҪз•ҘйқҷжҖҒеҠҹиҖ—пјҢеӣ дёәйӣҶжҲҗз”өи·Ҝзҡ„жҖ»еҠҹиҖ—дё»иҰҒжҳҜж …жһҒй©ұеҠЁ IC зҡ„еҠЁжҖҒеҠҹиҖ—пјҢеҸҜдј°з®—дёәпјҡ

В

В

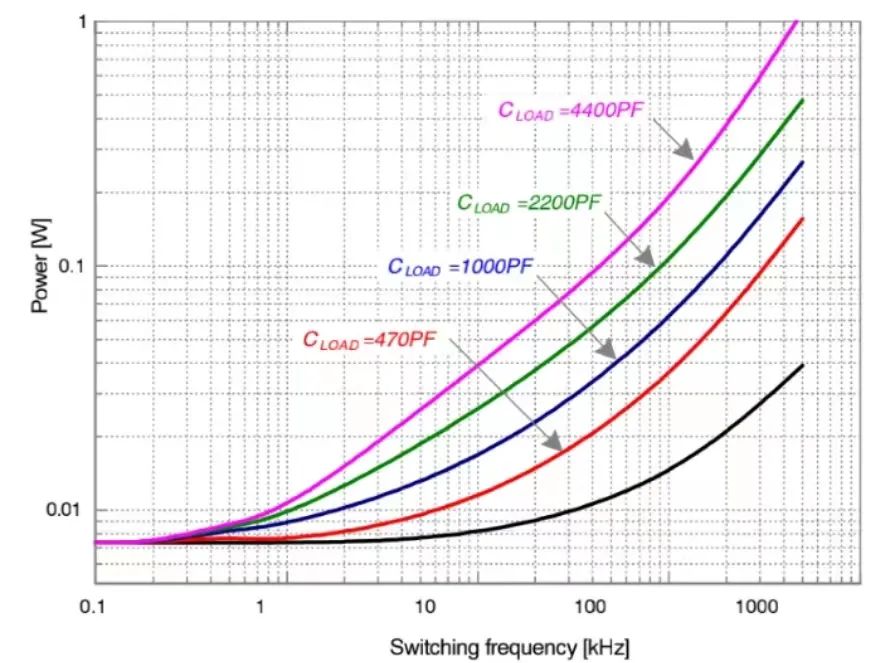

еӣҫ23иЎЁзӨәи®Ўз®—зҡ„ж …жһҒй©ұеҠЁеҷЁеҠҹиҖ—дёҺйў‘зҺҮе’ҢиҙҹиҪҪз”өе®№зҡ„е…ізі»(VDD=15 V)гҖӮжӯӨжӣІзәҝеҸҜз”ЁдәҺи®Ўз®—ж …жһҒй©ұеҠЁеҷЁйҖ жҲҗзҡ„еҠҹиҖ—гҖӮ

В

В

еӣҫ23В жһҒй©ұеҠЁеҷЁзҡ„жҖ»еҠҹиҖ—

В

иҮӘдёҫз”өи·Ҝзҡ„еҠҹиҖ—жҳҜиҮӘдёҫдәҢжһҒз®ЎеҠҹиҖ—е’ҢиҮӘдёҫз”өйҳ»еҠҹиҖ—зҡ„жҖ»е’ҢпјҢеҰӮжһңе®ғ们еӯҳеңЁзҡ„иҜқгҖӮиҮӘдёҫдәҢжһҒз®Ўзҡ„еҠҹиҖ—жҳҜеҜ№иҮӘдёҫз”өе®№е……з”өж—¶дә§з”ҹзҡ„жӯЈеҗ‘еҒҸзҪ®еҠҹиҖ—дёҺдәҢжһҒз®ЎеҸҚеҗ‘жҒўеӨҚж—¶дә§з”ҹзҡ„еҸҚеҗ‘еҒҸзҪ®еҠҹиҖ—зҡ„жҖ»е’ҢгҖӮеӣ дёәжҜҸдёӘдәӢ件жҜҸдёӘе‘ЁжңҹеҸ‘з”ҹдёҖж¬ЎпјҢжүҖд»ҘдәҢжһҒз®Ўзҡ„еҠҹиҖ—дёҺејҖе…ійў‘зҺҮжҲҗжӯЈжҜ”гҖӮеӨ§з”өе®№иҙҹиҪҪйңҖиҰҒжӣҙеӨҡзҡ„з”өжөҒпјҢеҜ№иҮӘдёҫз”өе®№еҷЁйҮҚж–°е……з”өпјҢд»ҺиҖҢеҜјиҮҙжӣҙеӨҡзҡ„еҠҹиҖ—гҖӮ

В

еҚҠжЎҘиҫ“е…Ҙз”өеҺӢ(VDCВ )и¶Ҡй«ҳпјҢеҸҚеҗ‘жҒўеӨҚеҠҹиҖ—и¶ҠеӨ§гҖӮйӣҶжҲҗз”өи·Ҝзҡ„жҖ»еҠҹиҖ—еҸҜд»Ҙдј°з®—дёәпјҡж …жһҒй©ұеҠЁеҷЁзҡ„еҠҹиҖ—дёҺиҮӘдёҫдәҢжһҒз®Ўзҡ„еҠҹиҖ—зҡ„жҖ»е’ҢпјҢеҮҸеҺ»иҮӘдёҫз”өйҳ»зҡ„еҠҹиҖ—гҖӮ

В

еҰӮжһңиҮӘдёҫдәҢжһҒз®ЎеңЁж …жһҒй©ұеҠЁеҷЁеҶ…йғЁзҡ„иҜқпјҢж·»еҠ дёҖдёӘдёҺеҶ…йғЁиҮӘдёҫдәҢжһҒ管并иҒ”зҡ„еӨ–йғЁдәҢжһҒз®ЎпјҢеӣ дёәдәҢжһҒз®ЎеҠҹиҖ—еҫҲеӨ§гҖӮеӨ–йғЁдәҢжһҒз®Ўеҝ…йЎ»ж”ҫзҪ®еңЁйқ иҝ‘ж …жһҒй©ұеҠЁеҷЁзҡ„ең°ж–№пјҢд»ҘеҮҸе°‘дёІиҒ”еҜ„з”ҹз”өж„ҹпјҢ并жҳҫи‘—йҷҚдҪҺжӯЈеҗ‘з”өеҺӢйҷҚгҖӮ

В

е°ҒиЈ…зғӯйҳ»

В

з”өи·Ҝи®ҫи®ЎиҖ…еҝ…йЎ»жҸҗдҫӣпјҡ

В

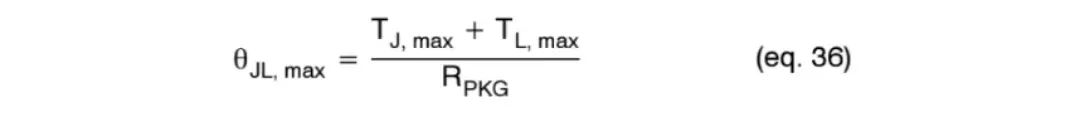

в—Ҹдј°з®—ж …жһҒй©ұеҠЁеҷЁе°ҒиЈ…еҗҺзҡ„еҠҹиҖ—

В

в—ҸжңҖеӨ§е·ҘдҪңз»“жё©TJ . MAX . OPRпјҢдҫӢеҰӮпјҢеҰӮйҷҚйўқиҮі TJ, MAX =150в„ғзҡ„80%пјҢеҜ№дәҺиҝҷдәӣй©ұеҠЁеҷЁдёә120в„ғгҖӮ

В

в—ҸжңҖй«ҳе·ҘдҪңеј•и„ҡз„Ҡй”Ўжё©еәҰ TL,MAX,OPRпјҢеӨ§зәҰзӯүдәҺй©ұеҠЁеҷЁдёӢжңҖеӨ§ PCB жё©еәҰпјҢжҜ”еҰӮ100в„ғгҖӮ

В

в—ҸжңҖеӨ§е…Ғи®ёз»“еҲ°еј•и„ҡзҡ„зғӯйҳ»и®Ўз®—дёәпјҡ

В

В

05

дёҖиҲ¬еҮҶеҲҷ

В

еҚ°еҲ·з”өи·ҜжқҝзүҲеӣҫ

В

е…·жңүжңҖе°ҸеҜ„з”ҹз”өж„ҹзҡ„зүҲеӣҫеҰӮдёӢпјҡ

В

в—ҸејҖе…ід№Ӣй—ҙзҡ„иө°зәҝжІЎжңүеӣһи·ҜжҲ–еҒҸе·®гҖӮ

в—ҸйҒҝе…Қдә’иҝһй“ҫи·ҜгҖӮе®ғдјҡжҳҫи‘—еўһеҠ з”өж„ҹгҖӮ

в—ҸйҷҚдҪҺе°ҒиЈ…дҪ“и·қзҰ»PCBжқҝзҡ„й«ҳеәҰпјҢд»ҘеҮҸе°‘еј•и„ҡз”өж„ҹж•Ҳеә”гҖӮ

в—ҸиҖғиҷ‘жүҖжңүеҠҹзҺҮејҖе…ізҡ„й…ҚеҗҲж”ҫзҪ®пјҢд»ҘеҮҸе°‘иө°зәҝй•ҝеәҰгҖӮ

в—ҸеҺ»иҖҰз”өе®№е’Ңж …жһҒз”өйҳ»зҡ„еёғеұҖе’ҢеёғзәҝпјҢеә”е°ҪеҸҜиғҪйқ иҝ‘ж …жһҒй©ұеҠЁйӣҶжҲҗз”өи·ҜгҖӮ

в—ҸиҮӘдёҫдәҢжһҒз®Ўеә”е°ҪеҸҜиғҪйқ иҝ‘иҮӘдёҫз”өе®№гҖӮ

В

иҮӘдёҫйғЁд»¶

В

еңЁйҮҸеҢ–иҮӘдёҫйҳ»жҠ—е’ҢеҲқж¬ЎиҮӘдёҫе……з”өж—¶зҡ„з”өжөҒж—¶пјҢеҝ…йЎ»иҖғиҷ‘иҮӘдёҫз”өйҳ»(RBOOT)гҖӮеҰӮжһңйңҖиҰҒз”өйҳ»е’ҢиҮӘдёҫдәҢжһҒз®ЎдёІиҒ”ж—¶пјҢйҰ–е…ҲзЎ®и®ӨVBдёҚдјҡдҪҺдәҺCOM(ең°)пјҢе°Өе…¶жҳҜеңЁеҗҜеҠЁжңҹй—ҙе’ҢжһҒйҷҗйў‘зҺҮе’ҢеҚ з©әжҜ”дёӢгҖӮ

В

иҮӘдёҫз”өе®№(CBOOT)дҪҝз”ЁдёҖдёӘдҪҺESRз”өе®№пјҢжҜ”еҰӮйҷ¶з“·з”өе®№гҖӮVDD е’Ң COMд№Ӣй—ҙзҡ„з”өе®№пјҢеҗҢж—¶ж”ҜжҢҒдёӢжЎҘй©ұеҠЁеҷЁе’ҢиҮӘдёҫз”өе®№зҡ„еҶҚе……з”өгҖӮе»әи®®иҜҘз”өе®№еҖјиҮіе°‘жҳҜиҮӘдёҫз”өе®№зҡ„еҚҒеҖҚд»ҘдёҠгҖӮ

В

иҮӘдёҫдәҢжһҒз®Ўеҝ…йЎ»дҪҝз”ЁиҫғдҪҺзҡ„жӯЈеҗ‘еҺӢйҷҚпјҢдёәдәҶеҝ«йҖҹжҒўеӨҚпјҢејҖе…іж—¶й—ҙеҝ…йЎ»е°ҪеҸҜиғҪеҝ«пјҢеҰӮи¶…й«ҳйҖҹгҖӮ

В

В

иҮӘдёҫз”өи·Ҝй—®йўҳзҡ„жҖқиҖғ

В

В

еӣҫ24

В

иҮӘдёҫз”өи·Ҝй—®йўҳзҡ„иЎҘж•‘жҺӘж–Ҫ

В

В

еӣҫ25

В

зӮ№еҮ»йҳ…иҜ»еҺҹж–ҮпјҢдәҶи§ЈжӣҙеӨҡ

еҺҹж–Үж Үйўҳпјҡй«ҳеҺӢж …жһҒй©ұеҠЁ IC иҮӘдёҫз”өи·Ҝзҡ„и®ҫи®ЎдёҺеә”з”ЁжҢҮеҚ—

ж–Үз« еҮәеӨ„пјҡгҖҗеҫ®дҝЎе…¬дј—еҸ·пјҡе®үжЈ®зҫҺгҖ‘ж¬ўиҝҺж·»еҠ е…іжіЁпјҒж–Үз« иҪ¬иҪҪиҜ·жіЁжҳҺеҮәеӨ„гҖӮ

- зӣёе…іжҺЁиҚҗ

- зғӯзӮ№жҺЁиҚҗ

- е

-

жҷ®иҜҡPT5606/PT5607й«ҳеҺӢж …жһҒй©ұеҠЁICзҡ„ж ёеҝғдјҳеҠҝ2025-11-24 2214

-

иҮӘдёҫз”өи·Ҝзҡ„з”өе®№еӨ§е°ҸиҜҘжҖҺд№ҲйҖүпјҹ2025-03-03 2789

-

DGD2101й«ҳеҺӢж …жһҒй©ұеҠЁеҷЁIC2023-07-24 897

-

еҰӮдҪ•е®ҡд№үж …жһҒз”өйҳ»еҷЁгҖҒиҮӘдёҫз”өе®№еҷЁд»ҘеҸҠдёәд»Җд№Ҳй«ҳдҫ§ж …жһҒй©ұеҠЁеҷЁеҸҜиғҪйңҖиҰҒеҜ№MOSFETжәҗжһҒж–ҪеҠ дёҖдәӣз”өйҳ»пјҹ2023-04-19 753

-

FAN73912MX е·Ҙдёҡзә§з”өжңәи§ЈеҶіж–№жЎҲ еҚҠжЎҘж …жһҒй©ұеҠЁ IC2021-12-20 1129

-

ir21xxзі»еҲ—ж …жһҒй©ұеҠЁеҷЁиҮӘдёҫз”өи·Ҝ2021-10-29 2402

-

й«ҳеҺӢж …жһҒй©ұеҠЁеҷЁиҮӘдёҫз”өи·Ҝи®ҫи®Ў2021-06-19 1899

-

NCP5106BA36WGEVBпјҢз”ЁдәҺNCP5106,36 Wй•ҮжөҒеҷЁпјҢжҳҜдёҖж¬ҫй«ҳеҺӢж …жһҒй©ұеҠЁеҷЁIC2019-10-12 2388

-

й«ҳйҖҹMOSFETж …жһҒй©ұеҠЁз”өи·Ҝзҡ„и®ҫи®ЎдёҺеә”з”ЁжҢҮеҚ—2019-03-08 4216

-

е·ҘзЁӢеёҲз»ҸйӘҢд№Ӣй«ҳеҺӢж …жһҒй©ұеҠЁеҷЁиҮӘдёҫз”өи·Ҝи®ҫи®Ў2017-10-31 44566

-

йЈһе…ҶеҚҠеҜјдҪ“жҺЁдёҡз•ҢйўҶе…Ҳзҡ„й«ҳеҺӢж …жһҒй©ұеҠЁеҷЁIC2016-06-22 3655

-

й«ҳеҺӢжө®еҠЁMOSж …жһҒй©ұеҠЁйӣҶжҲҗз”өи·Ҝ(еә”з”ЁжүӢеҶҢ)2010-01-04 1319

-

AN-6076дҫӣй«ҳз”өеҺӢж …жһҒй©ұеҠЁеҷЁICдҪҝз”Ёзҡ„иҮӘдёҫз”өи·Ҝзҡ„и®ҫи®Ўе’ҢдҪҝ2009-12-03 1696

-

и®ҫи®Ўй«ҳеҺӢдҫ§ж …жһҒй©ұеҠЁз”өи·ҜдёҺжҚҹиҖ—2009-10-01 529

е…ЁйғЁ0жқЎиҜ„и®ә

еҝ«жқҘеҸ‘иЎЁдёҖдёӢдҪ зҡ„иҜ„и®әеҗ§ !