AMD第四代EPYC服务器处理器内存如何?

处理器/DSP

描述

AMD第四代EPYC服务器处理器内存如何?

AMD在美国加利福尼亚州举行了名为“Together We Advance Data Centers”的主题活动,正式发布了基于Zen 4架构、代号Genoa的第四代EPYC服务器处理器。AMD称,新款处理器将为企业、云计算和高性能计算的工作负载提供无与伦比的性能。

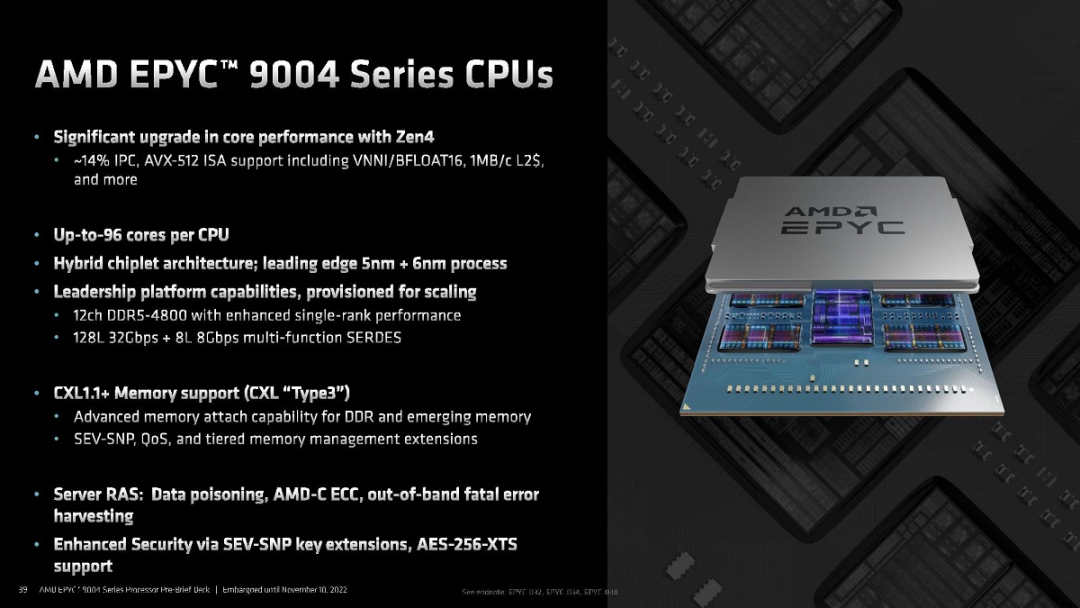

第四代EPYC服务器处理器使用了全新的SP5插座,最多可配备12个CCD,每个CCD具有8个Zen 4架构核心,L3缓存为32MB,而每个核心拥有1MB的L2缓存,加起来最多共有96个核心192线程、96MB的L2缓存和384MB的L3缓存。与消费级的Ryzen 7000系列处理器一样,CCD和IOD分别采用了台积电的5nm和6nm工艺。 此外,第四代EPYC服务器处理器支持12通道DDR5内存(每个通道有两个DIMM),最大可以支持12TB容量;配备了128个PCIe 5.0通道,其中112个可用;支持AVX-512和VNNI指令;同时还实现了对CXL 1.1+的支持,提供了突破性的内存扩展能力。 发布会上,AMD选择了与第三代英特尔至强(Xeon)可扩展处理器进行了对比。 结果显示在SPEC CPU 2017的整数性能测试中,核心数量相等的情况下,16核心的EPYC 9174F相比Xeon Gold 6346快了44%;32核心的EPYC 9374F相比Xeon Platinum 8362快了45%;48核心的EPYC 9474F相比40核心的Xeon Platinum 8380快了44%。 新的“EPYC”搭载了最新的CPU核心“Zen4”,这是x86兼容CPU核心“Zen”系列的第四代。本文将汇报一下4代EPYC处理器的内存配置。

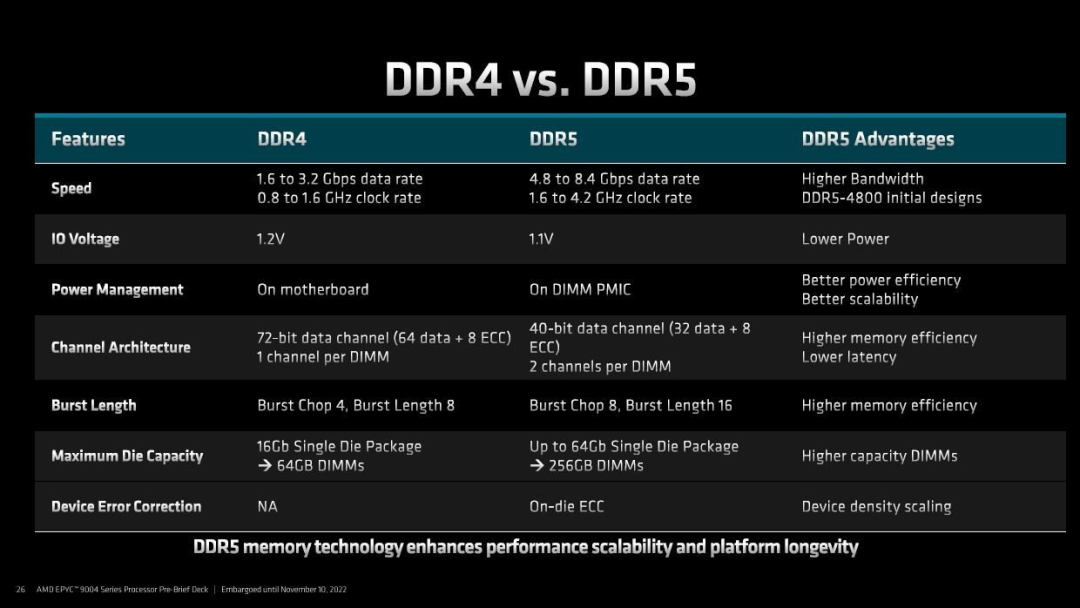

各代服务器处理器“EPYC”概览。来源:AMD 第 4 代 EPYC主存所支持的外部半导体存储器,比上一代第 3 代 EPYC具有更高的数据传输速度和更大的存储容量。第三代 EPYC 支持 DDR4 类型的 DRAM。第 4 代 EPYC 支持下一代 DDR5 类型 DRAM。 因此,DRAM 的最大数据传输速度提高了 1.5 倍,每个处理器(插槽)的最大存储容量增加了一倍。每个DRAM输入/输出引脚的数据传输速率为4800Mbps,每个处理器的内存容量达到6T字节。

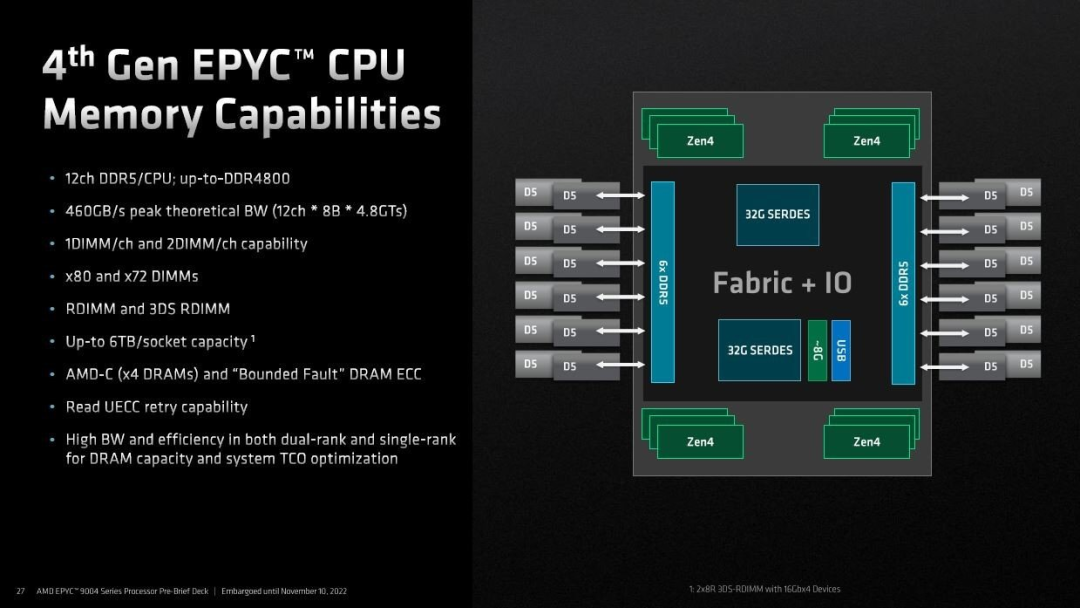

EPYC处理器支持的DDR4型DRAM和DDR5型DRAM的主要规格 来源:AMD 支持高达 64 Gbit DRAM 容量和 256 Gbyte DIMM 容量 EPYC 处理器采用 chiplet 配置。与主存DRAM交换数据的是输入/输出芯片(IOD或IO Die)。输入/输出芯片配备了一个 12 通道 DDR5 内存控制器,每个通道最多可以连接两个 DRAM 模块(DRAM DIMM)。 唯一受支持的 DIMM 类型是 RDIMM(带寄存器的 DIMM)和 3DS(三维堆栈)RDIMM。DRAM的最大存储容量为64 Gbits,DIMM的最大存储容量为256 Gbytes。如果您将两个 256GB DIMM 连接到每个通道,则每个插槽的存储容量将为 6TB。 AMD 将输入/输出芯片的内存控制器称为“UMC(通用内存控制器)”。在输入/输出管芯的说明图中,内存控制器的符号混合了“DDR5”和“UMC”的图样。请注意,两者是相同的。

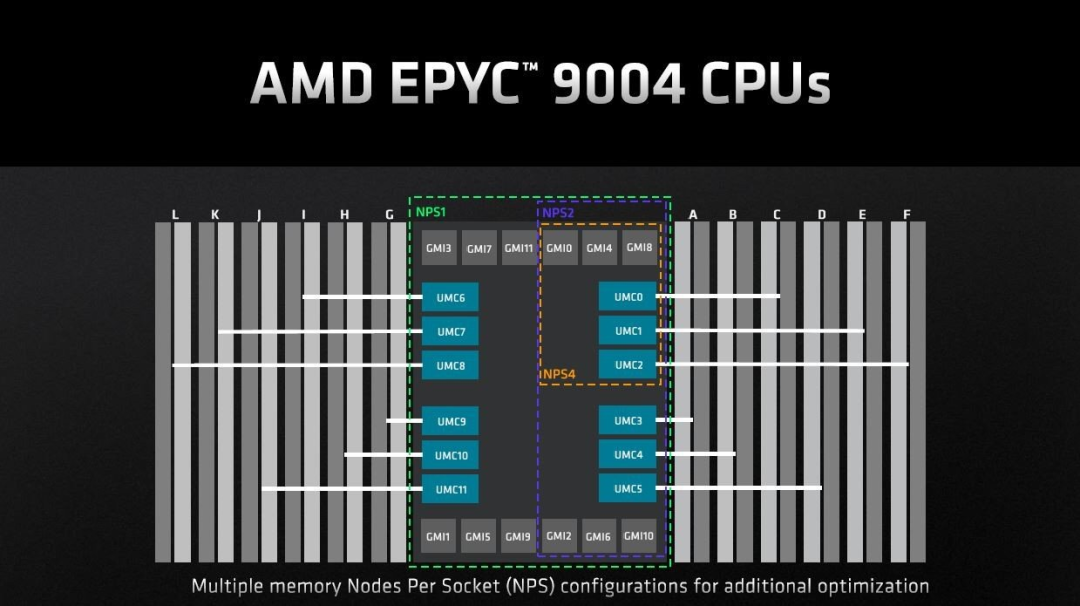

第4代EPYC处理器的主内存(main memory)配置。输入/输出裸片(图中表示为“Fabric + IO”)配备了一个12通道的DDR5内存控制器,每个通道都连接到主内存DRAM模块(DIMM)来源:AMD 将 CPU 内核嵌入式芯片和内存通道分成最多 4 组 第 4 代 EPYC(霄龙)还有一个选项“NPS(Nodes Per Socket)”,通过对 CPU 内核和内存通道进行分组来优化内存访问。NPS 有选项 1、2 和 4。NPS1自由连接包含CPU内核和内存通道的裸片(CCD),无需分组。 NPS2 分为两组。将12个CCD和12个内存通道一分为二。输入/输出管芯的内存通道被6个通道分为左右,所以靠近左边6个通道的6个CCD组成一组,靠近右边6个通道的6个CCD组成另一组。这缩短了CCD到内存控制器的平均距离,缩短了信号传输延迟时间,减少了延迟变化。 此外,NPS4 创建了一组三个 CCD 和三个物理上彼此靠近的内存通道。进一步缩短了信号传输的平均延迟时间,减少了延迟变化。因此,它有助于有效加速内存访问。

来源:AMD

主存带宽扩大至上一代的2.3倍

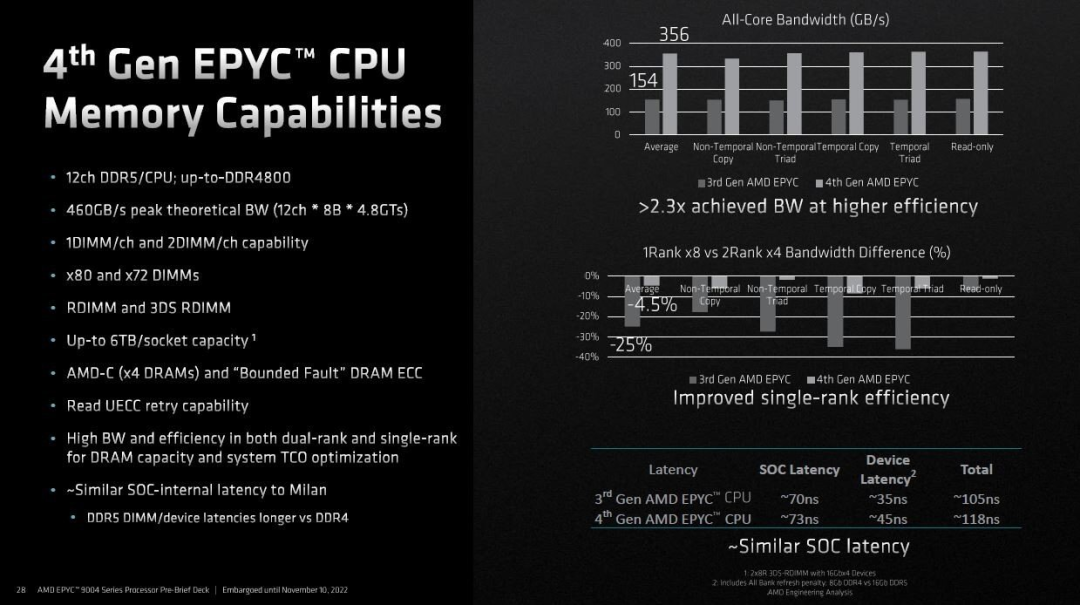

AMD还展示了第4代EPYC与第3代EPYC的主存性能对比结果。主存带宽平均达到356 GB/s。比第 3 代 EPYC(霄龙)宽 2.3 倍。单列和双列之间的带宽差异显着缩小到平均 4.5%。第三代 EPYC DIMM 的平均性能差异为 25%。

4代EPYC主内存性能与3代EPYC主内存性能对比。从顶部开始,“数据传输速率(带宽)”、“单列和双列带宽之间的差异”、“访问延迟(延迟)的差异” 来源:AMD 此外,尽管集成规模有所扩大,但与第三代 EPYC 相比,内存访问延迟(延迟时间)增加了约 13 纳秒(约 12%)。

编辑:黄飞

-

安勤科技发布HPM-SIEUA服务器主板,搭载AMD第四代Siena处理器2024-12-27 1263

-

AMD EPYC处理器:AI推理能力究竟有多强?2024-03-15 1303

-

AMD第四代EPYC(霄龙)系列处理器介绍2024-01-29 3834

-

AMD扩展第四代EPYC CPU产品带来突破性的性能2023-10-07 1574

-

AMD 3D V-Cache技术的第四代EPYC处理器性能介绍2023-08-14 1112

-

全新亚马逊EC2 M7a实例使用第四代AMD EPYC处理器2023-06-20 1455

-

AMD 推出第四代 AMD EPYC 处理器,为嵌入式网络、安全、存储与工业系统提供卓越性能2023-03-15 1475

-

美光 DDR5 内存配合第四代 AMD EPYC 处理器,提升高性能计算工作负载2022-12-19 1353

-

详细解读四代EPYC处理器技术2022-12-16 5859

-

第四代AMD EPYC处理器独家测试2022-12-15 3853

-

AMD EPYC 9004系列正式发布:升级支持DDR5内存,最高频率4800MHz2022-12-06 3621

-

美光DDR5内存现已配合第四代AMD EPYC处理器平台出货2022-11-21 736

-

金山云第四代云服务器正式发布,性能提升23%2020-03-19 2964

-

英特尔正式推出第四代酷睿Haswell处理器2013-06-03 1737

全部0条评论

快来发表一下你的评论吧 !