RISC-V给我们带来了什么?

电子说

描述

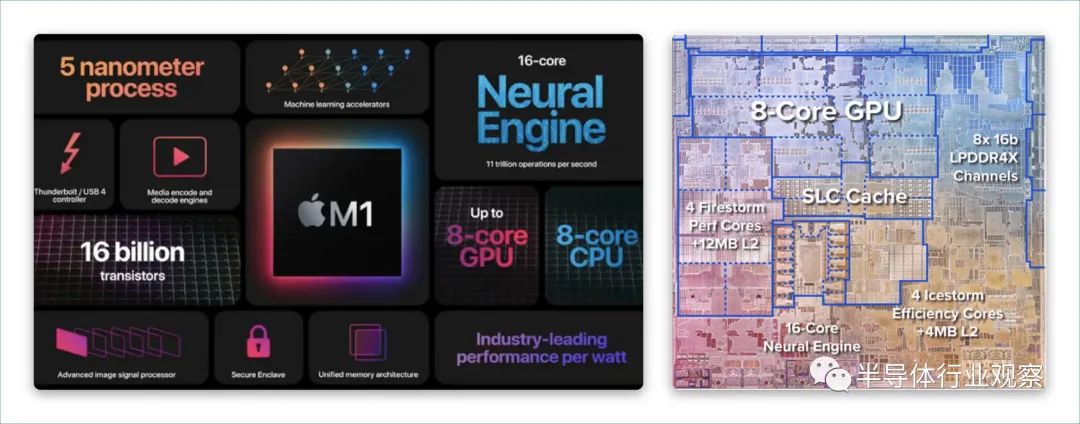

图 1:Apple M1 SoC 参考:AnandTech

在这种情况下,主要挑战是:

1.选择并与多家 IP 供应商合作

2.不同的 IP 供应商可能有不同的 IP 许可方案,工程师将无法自由地定制 ISA 和设计,因为他们更愿意满足他们的设计目标。

3.所有专门的 ISA 都不会持续/生存很长时间,从而影响长期产品支持计划和路线图。

4.此外,涉及多个 ISA 和工具链的软件/应用程序开发和更新将具有挑战性。

什么是 RISC-V,它与其他 ISA 有何不同?

二、RISC-V 基础 ISA

RISC-V 是一个相关 ISA 家族:RV32I、RV32E、RV64I、RV128I。

RV32I/ RV32E/ RV64I/RV128I 是什么意思:

RV——RISC-V

32/64/128 – 定义寄存器宽度 [XLEN] 和地址空间

I – 整数基 ISA

32 个用于所有基本 ISA 的寄存器

E – 嵌入式:只有 16 个寄存器的基本 ISA

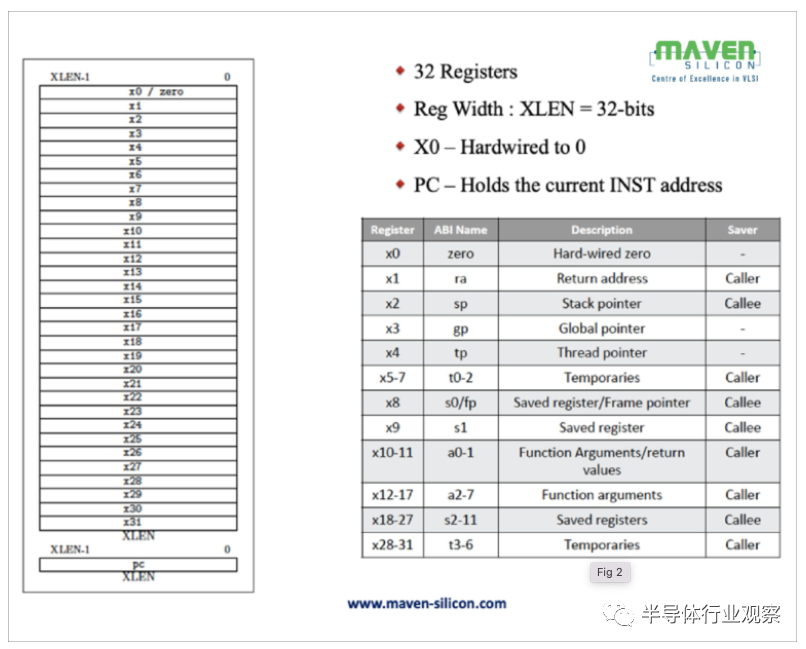

(1)RISC-V 寄存器:

图 2:RISC-V 寄存器和 ABI 名称参考:RISC-V 规范

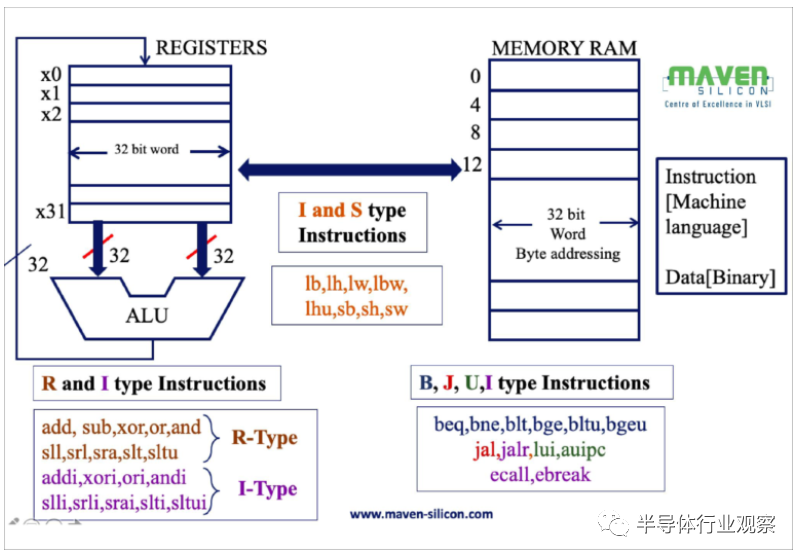

(2)RISC-V内存:

(3)RISC-V 加载存储架构

RISC-V处理器根据PC中的地址从主存中取/载指令,译码32位指令,然后ALU进行算术/逻辑/内存读写操作。ALU 的结果将存储回其寄存器或内存中。

图 3:RISC-V 加载存储架构

(4)RISC-V RV32 I 基础 ISA

R-Type:注册到注册说明

I-Type:立即注册、加载、JLR、Ecall 和 Ebreak

S型:商店

B型:分支

J型:跳跃和链接

U 型:立即加载/添加上层

图 4:RV32I 基本 ISA 指令格式

(5)用于优化 RTL 设计的 RISC-V ISA

立即数总是经过符号扩展,并且通常被打包到指令中最左边的可用位,并且已被分配以降低硬件复杂性。尤其是,

主要操作码总是在位 0-6 中。

目标寄存器(如果存在)始终位于位 7-11 中。

第一个源寄存器(如果存在)始终位于第 15-19 位。

第二个源寄存器(如果存在)始终位于第 20-24 位。

但是为什么立即位会被打乱呢?想想解码直接场的物理电路。由于它是硬件实现,因此这些位将被并行解码;输出立即数中的每一位都有一个多路复用器来选择它来自哪个输入位。多路复用器越大,成本越高,速度也越慢。

值得注意的是,只需要主要操作码(位 0-6)就可以知道如何解码立即数,因此立即数解码可以与指令其余部分的解码并行完成。

(6)RV32I 基本 ISA 指令

RISC-V ISA 扩展

此处列出了所有 RISC-V ISA 扩展:

图 5:RISC-V ISA 扩展

整数 64 位基本 ISA + 扩展:[乘法 + 原子 + SP 浮动 + DP 浮动 + 压缩]

RISC-V 特权架构

RISC-V 特权架构涵盖了 RISCV 系统的所有方面,超出了我到目前为止所解释的非特权 ISA。特权架构包括特权指令以及运行操作系统和连接外部设备所需的附加功能。

示例:运行类 Unix 操作系统的桌面等系统

Hypervisor Execution Environment – HEE:RISC-V hypervisor,为来宾操作系统提供多个管理级执行环境。

示例:运行多个guest操作系统的云服务器

图 6:RISC-V 特权软件堆栈参考:RISC-V 规范

原文链接:https://semiwiki.com/semiconductor-services/maven-silicon/321555-is-your-career-at-risk-without-risc-v/

END

(添加请备注公司名和职称)

对话Imagination中国区董事长:以GPU为支点加强软硬件协同,助力数字化转型

原文标题:RISC-V给我们带来了什么?

文章出处:【微信公众号:Imagination Tech】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- imagination

-

直播预约 | RISC-V大使谈RISC-V软硬件生态最新进展和未来趋势张国斌2024-11-12 1091

-

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !2024-09-10 1536

-

走进RISC-V:芯片界的新革命2024-07-12 1730

-

RISC-V芯粒,终于来了2023-09-15 1716

-

RISC-V设计支持工具,支持RISC-V技术的基础2023-07-14 831

-

RISC-V给我们带来了什么?2022-12-15 1907

-

什么是模型呢?模型给我们带来了什么?2021-07-02 2492

-

CAN究竟给我们带来了什么电子技术呢?2021-05-12 1522

-

RISC-V规范的演进 RISC-V何时爆发?2021-02-11 4389

-

对于RISC-V,我们对它有些误解?2020-08-02 4319

-

为什么选择RISC-V?2020-07-27 5006

-

RISC-V给FPGA带来了什么机遇2020-06-09 4287

-

科技进步究竟给我们带来了什么?2019-07-23 13813

-

RISC阵营便动作频频,为加速RISC-V的生态发展和相关技术成熟2019-02-19 5270

全部0条评论

快来发表一下你的评论吧 !