多晶粒SoC成趋势,UCIe标准助其一臂之力

电子说

1.3w人已加入

描述

单片 SoC 的尺寸变得太大,无法制造 某些 SoC 的功能要获得最佳实现,可能需要不同的工艺节点 对增强产品的可扩展性和可组合性需求正在增加

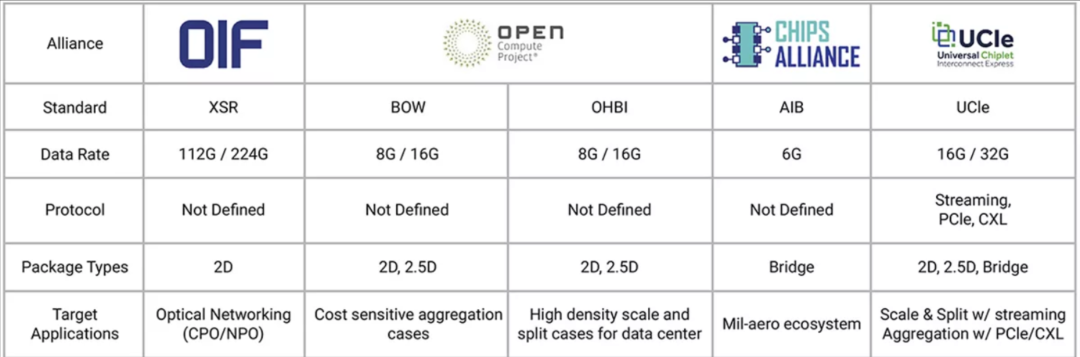

Optical Interface Forum (OIF) – 针对晶粒间连接而优化的 XSR 和 USR 物理层规范 Chips Alliance – 最初由英特尔推出的 AIB 规范 Open Compute Platform (OCP) – 针对不同用例而优化的 OpenHBI 和 Bunch-of-Wires (BOW) 规范 Unified Chiplet Interconnect Express (UCIe) – 涵盖多个用例和完整协议栈的全面晶粒间互连规范

UCIe 系谱

UCIe 路线图和用例

用于先进封装(硅中介层、硅桥或 RDL 扇出)的 UCIe 用于标准包装(有机基材或层压板)的 UCIe

UCIe 规范概述

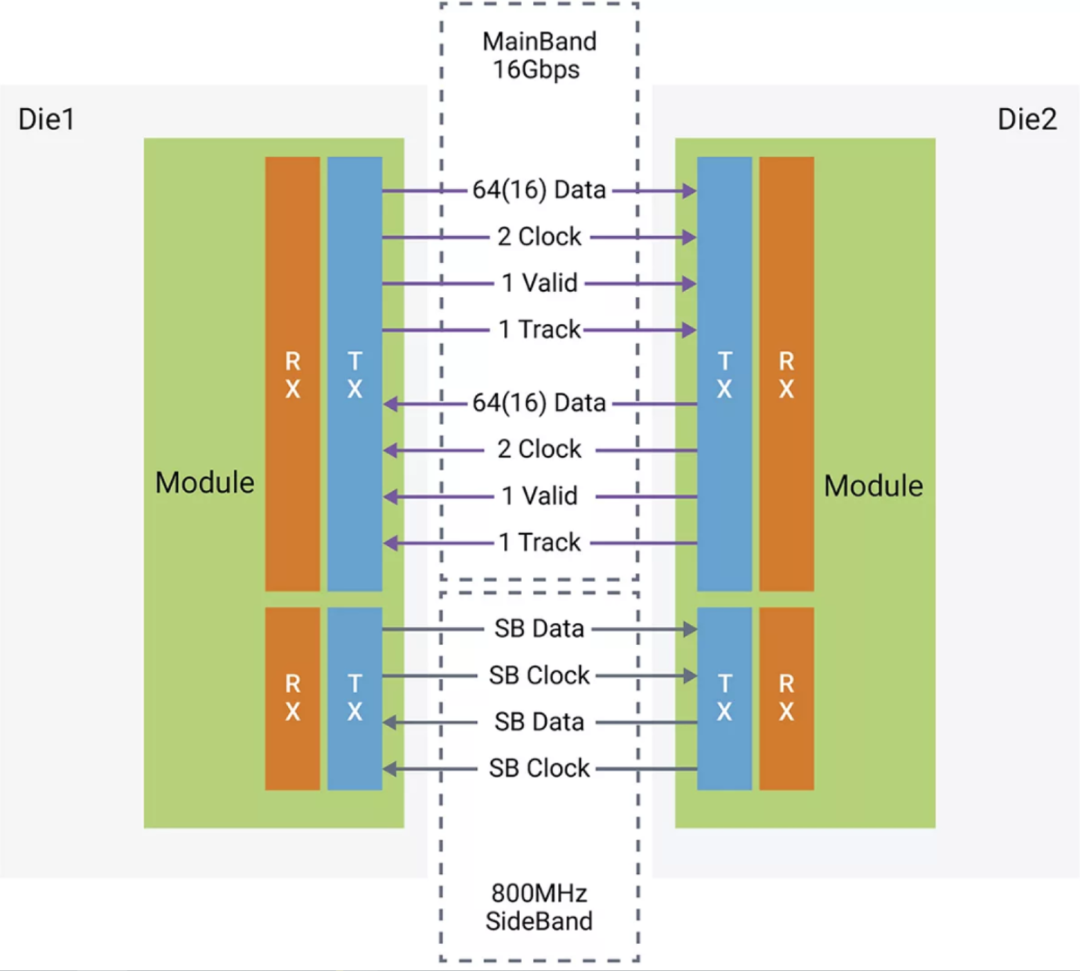

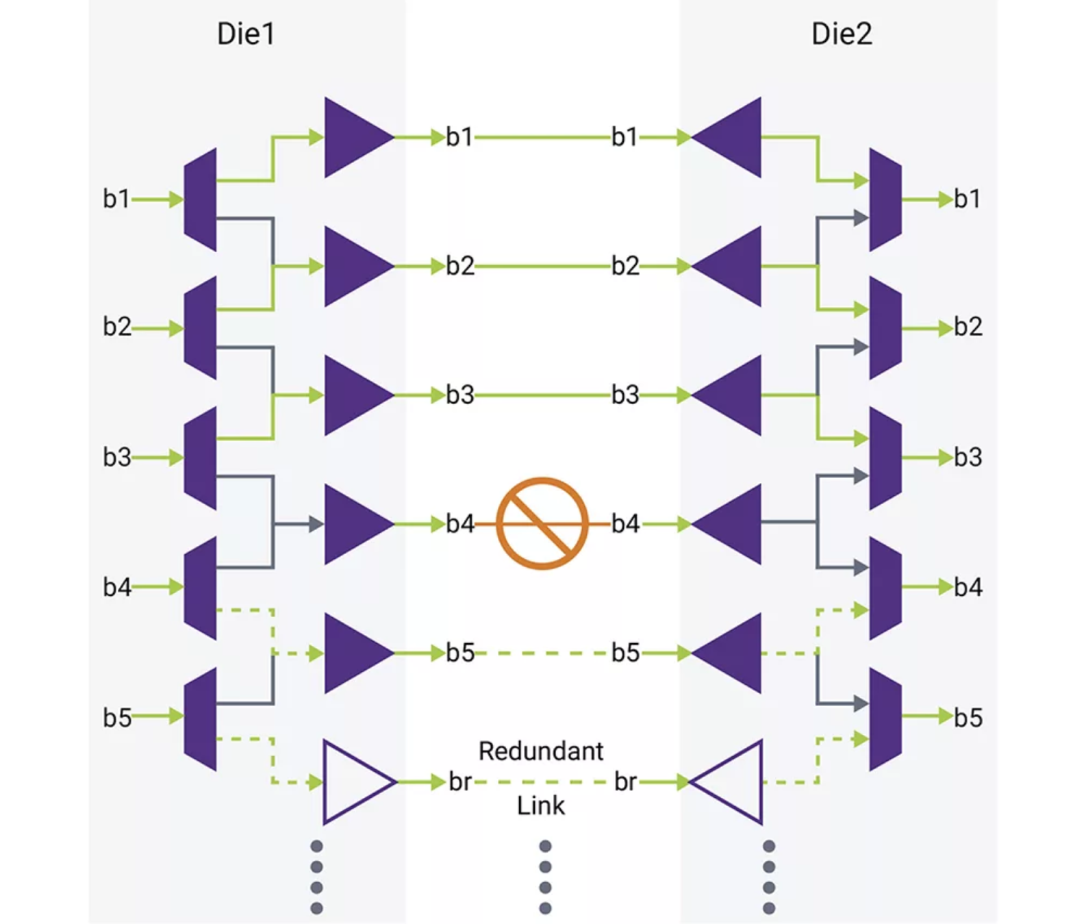

物理层是封装介质的电气接口。它包括电气 AFE(发射器、接收器)以及边带信道,可实现两个晶粒之间的参数交换和协商。它还包括可实现链路初始化、训练和校准算法以及测试和修复功能的逻辑 PHY。 晶粒间适配器层负责链路管理功能以及协议仲裁和协商。它包括基于 CRC 和重试机制的可选纠错功能。 协议层实施一个或多个 UCIe 支持的协议。如今,此类协议是 PCI Express、CXL 和/或流式传输协议。它们是基于 Flit 的协议,可提供最高效率和更低的延迟。

物理层

晶粒间适配器层

CXL3 256B 标准 FLIT 模式 CXL3 256B 延迟优化 FLIT 模式 PCIe6 256B FLIT 模式 CXL2 68B 增强型 FLIT 模式 流式传输 64B 原始模式

协议层

结语

经过硅验证的 IP 产品组合,包括接口 IP、处理器 IP、安全 IP 和测试 IP 适用于 UCIe 和 112G XSR 的完整晶粒间控制器和 PHY IP 完整的 HBM3 控制器和 PHY IP 广泛的集成支持 统一的 3DIC 探索和设计基础架构 与代工厂和 OSAT 的生态系统协作

原文标题:多晶粒SoC成趋势,UCIe标准助其一臂之力

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 电子发烧友网

全部0条评论

快来发表一下你的评论吧 !